1

Изобретение относится к вычислительной технике и может быть применено при изготовлении однократно электрически программируемых полупроводниковых постоянных запоминающих устройств, сохраняющих информацию при отключении питания.

Известны программируемые постоянные запоминающие элементы, использующие способ пережигания плавких перемычек, содержащие разрядные и словарные щины, в местах пересечения которых находятся ключевые элементы и элементы связи .

Недостаток этих запоминающих элементов состоит в больщой мощности импульса пережигания плавких перемычек, что ведет к усложнению всего устройства.

Для однократно электрически программируемых запоминающих элементов, использующих явление лавинного пробоя р-п-иерехода диода транзистора, требуется импульс значительно меньщей мощности . При этом ключевым элементом может служить транзистор, соответствующие выводы которого подключаются к словарной и разрядной щинам.

Наиболее близок к изобретению программируемый постоянный запоминающий элемент, содержащий ключевой диод, последовательно соединенный с лавинно пробиваемым диодом, соединенным с разрядной и числовой шинами 3.

Недостатком такого запоминающего элемента является больщая сложность, так

как применение технологии: кремний на сапфире и биполярной-требует изоляции элементов конструкции для устранения паразитных связей. Цель изобретения - упрощение запоминающего элемента.

Поставленная цель достигается тем, что в программируемом постоянном запоминающем элементе, содержащем подложку, на поверхности которой расположен полупроводниковый слой с диффузионными истоковой и стоковой областями МДП-транзистора, затвор которого подключен к словарной щине и размещен в диэлектрическом слое, расположенном на поверхности полупроводникового слоя, диффузионная стоковая область МДП-транзистора подключена к разрядной щине, расположенной на поверхности диэлектрического слоя перпендикулярно к словарной шине, подложка выполнена проводящей, например металлической, и образует с диффузионной истоковой областью МДП-транзистора пробиваемый напряжением переход. Кроме того, с целью уменьщения напряжения пробоя, предлагаемый элемент может содержать в полупроводниковом слое диффузионную эмиттерную область, иодключенную к подложке и образующую с диффузионной с истоковой областью МДПтранзистора биполярный транзистор.

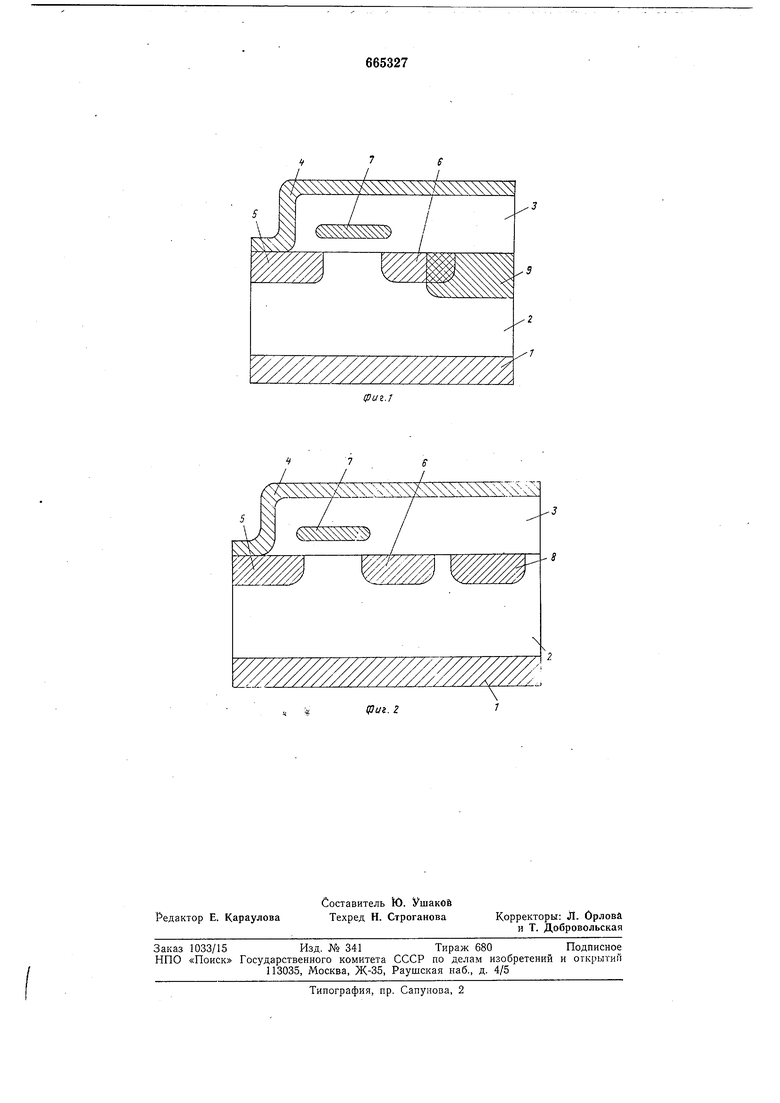

На фиг. 1 изображен предлагаемый запоминающий элемент; на фиг. 2 -запоминающий элемент с диффузионной эмиттерной областью в полупроводниковом слое.

Запоминающий элемент содержит подложку 1, полупроводниковый слой 2, диэлектрический слой 3, разрядную щину 4, диффузионные стоковую 5 и истоковую 6 области МДП-транзистора, затвор 7 которого соединен со словарной шиной.

В полупроводниковом слое 2 может быть расположена диффузионная эмиттерная область 8 биполярного транзистора, базой которого является полупроводниковый слой 2, а коллектором - диффузионная истоковая область 6.

Дополнительная диффузионная область 9, тип проводимости которой совпадает с типом проводимости полупроводникового слоя 2, также ведет к уменьшению напряжения пробоя перехода между истоковой областью 6 и подложкой 1, которая выполнена металлической и служит третьей шиной- щиной нулевого потенциала при записи и считывании информации из запоминающего элемента.

Запись информации в запоминающий элемент проводится подачей открывающего напряжения по словарной щине на затвор 7 и импульса программируемого напряжения на стоковую область 5 по разрядной щине 4, что приводит к закорачиванию истоковой области 6 на полупроводниковый слой 2, а следовательно, и на подложку 1.

Считывание информации осуществляется по величине тока в разрядной шине при подаче открывающего напряжения по словарной шине на затвор 7, наличие тока соответствует единичному состоянию,

т. е. тому, что истоковая область 6 закорочена на подложку 1.

Введение областей 8 и 9 существенно уменьшает напряжение пробоя и снижает требования к импульсу программируемого напряжения.

Такая конструкция за счет простоты позволяет снизить стоимость изготовления запоминающих устройств.

.

Формула изобретения

1.Программируемый постоянный запоминающий элемент, содержащий подложку, на поверхности которой расположен полупроводниковый слой с диффузионными истоковой и стоковой областями МДПтранзистора, затвор которого подключен к словарной шине и размещен в диэлектрическом слое, расположенном на поверхн.ости полупроводникового слоя, диффузионная стоковая область МДП-транзистора подключена к разрядной шине, расположенной на поверхности диэлектрического слоя перпендикулярной к словарной щине,

отличающийся тем, что, с целью упрощения элемента, подложка выполнена проводящей, например металлической, и образует с диффузионной истоковой областью МДП-транзистора пробиваемый напряжением переход.

2.Элемент по п. 1, отличающийся тем, что, с целью уменьшения напряжения пробоя, он содержит в полупроводниковом слое диффузионную эмиттерную область,

подключенную к подложке и образующую с диффузионной истоковой областью МДПтранзистора биполярный транзистор.

Источники информации, принятые во внимание при экспертизе 1. Патент США № 3611319, кл. 340-173, опублик. 1971.

2.Патент США № 3699540, кл. 340-173, опублик 1971.

3.Патент США № 3733690, кл. 29-577, опублик. 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1980 |

|

SU888731A1 |

| МДП-транзистор | 1990 |

|

SU1762342A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444891A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444890A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1385872A1 |

| Элемент памяти для постоянного запоминающего устройства и способ его изготовления | 1989 |

|

SU1642888A1 |

Авторы

Даты

1979-05-30—Публикация

1977-04-04—Подача