( ТРОИЧНЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный сумматор | 1976 |

|

SU638960A1 |

| Сумматор по модулю три | 1976 |

|

SU669354A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Двоичный сумматор | 1980 |

|

SU857976A1 |

| Сумматор по модулю три | 1977 |

|

SU734684A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Сумматор по модулю три | 1982 |

|

SU1057941A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

| Двоичный счетчик импульсов | 1981 |

|

SU1001486A1 |

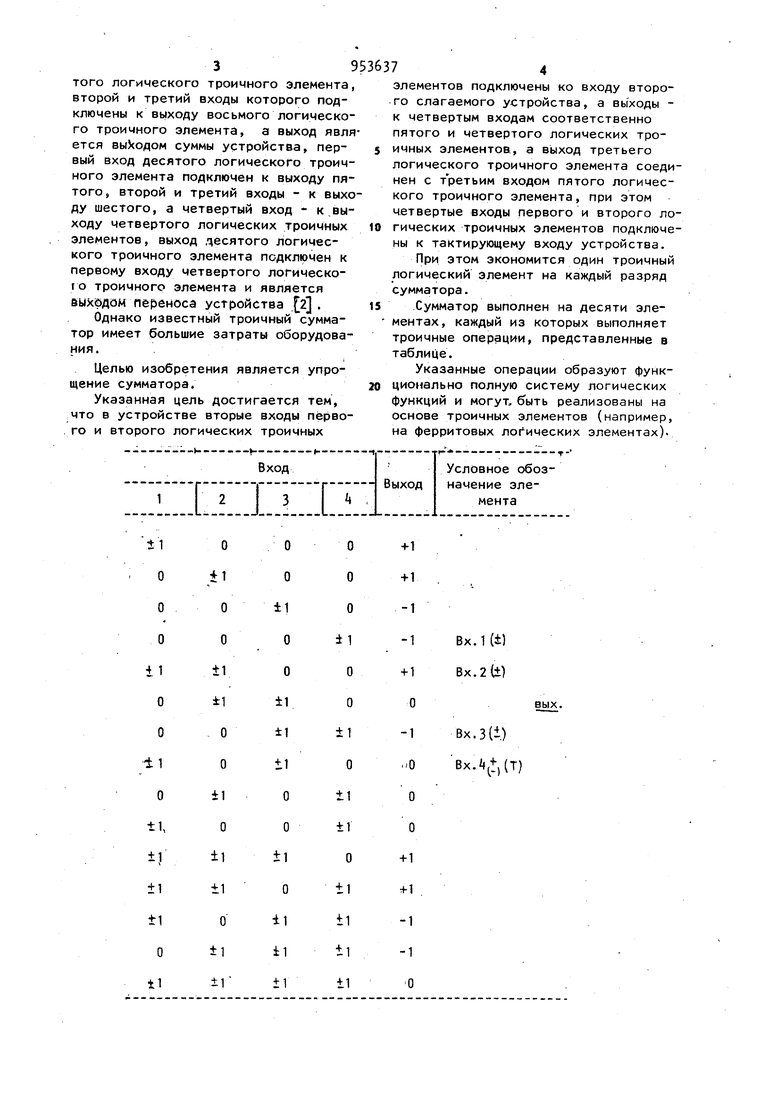

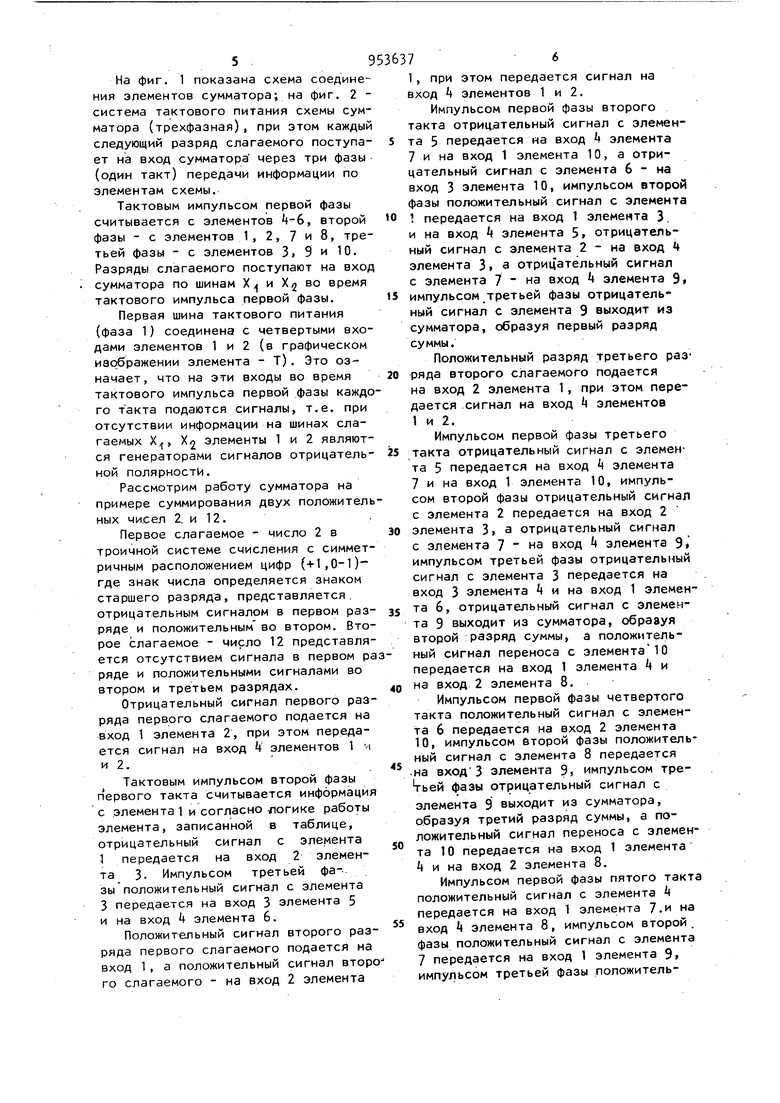

Изобретение относится к вычисли тельной технике и может быть испол зовано при проектировании сумматор цифровых вычислительных устройств троичной системой счисления. Известнь троичные сумматоры, вы лненные на троичных логических элементах. Сумматор содержит шестнадцать троичных логических элементов 1 . Однако известные троичные сумматоры имеют большие затраты оборудования. Наиболее близким к изобретению по технической сущности и достигаемому результату является троичный сумматор, содержащий десять логических троичных элементов, причем первые входы первого и второго логических троичных элементов подключены ко входу первого слагаемого устройства, выход первого логического троичного элемента соединен с первым и вторым, а выход второ:го логического троичного элемента с третьим и четвертым входами третьего логического троичного элемента , выход которого подключен к третьему входу четвертого логического троичного элемента, первый вход которого подключен к первому входу пятого логического троичного элемента, третий вход - к первому и четвертому входам шестого логического троичного элемента, а выход - к первому и второму входам седьмого и четвертому входу восьмого логических троичных элементов, выход пятого логического троичного элемента подключен к третьему и четвертому входам седьмого логического троичного элемента и первому входу восьмого логического троичного элемента, второй и третий входы которого подключены к первому входу четвертого логического троич- . ного элемента, выход седьмого логического троичного элемента подключен к первому и четвертому входам девя39того логического троичного элемента второй и третий входы которого подключены к выходу восьмого логического троичного элемента, а выход явля ется выводом суммы устройства, первый вход десятого логического троичного элемента подключен к выходу пятого, второй и третий входы - к выхо ду шестого, а четвертый вход - к,выходу четвертого логических троичных элементов, выход десятого логического троичного элемента подключен к первому входу четвертого логического троичного элемента и является выхедом переноса устройства 2. Однако известный троичный сумматор имеет большие затраты оборудования. Целью изобретения является упрощение сумматора. Указанная цель достигается тем, что в устройстве вторые входы первого и второго логических троичных 7 элементов подключены ко входу второго слагаемого устройства, а выходы к четвертым входам соответственно пятого и четвертого логических троичных элементов, а выход третьего логического троичного элемента соединен с третьим входом пятого логического троичного элемента, при этом четвертые входы первого и второго логических троичных элементов подключены к тактирующему входу устройства. ПРИ этом экономится один троичный логический элемент на каждый разряд сумматора. Сумматор выполнен на десяти элементах, каждый из которых выполняет троичные операции, представленные в таблице. Указанные операции образуют функционально полную систему логических функций и могут, быть реализованы на основе троичных элементов (например, на ферритовых логических элементах). На фиг. 1 показана схема соедине ния элементов сумматора; на фиг. 2 система тактового питания схемы сум матора (трехфазная), при этом кажды следующий разряд слагаемого поступа ет на вход сумматора через три фазы (один такт) передачи информации по элементам схемы. Тактовым импульсом первой фазы считывается с элементов k-6, второй фазы - с элементов 1, 2, 7 и 8, тре тьей фазы - с элементов Bi 9 и 10. Разряды слагаемого поступают на вход сумматора по шинам Х и Х2 во время тактового импульса первой фазы. Первая шина тактового питания (фаза 1) соединена с четвертыми входами элементов 1 и 2 (в графическом изображении элемента - Т). Это означает, что на эти входы во время тактового импульса первой .фазы каждо го такта подаются сигналы, т.е. при отсутствии информации на шинах слагаемых Х, Х2 элементы 1 и 2 являются генераторами сигналов отрицательной полярности. Рассмотрим работу сумматора на примере суммирования двух положитель ных чисел 2. и 12. Первое слагаемое - число 2 в троичной системе счисления с симметричным расположением цифр (+1,0-1) где знак числа определяется знаком старшего разряда, представляется, отрицательным сигналом в первом разряде и положительным во втором. Второе слагаемое - число 12 представляется отсутствием сигнала в первом ра ряде и положительными сигналами во втором и третьем разрядах. Отрицательный сигнал первого разряда первого слагаемого подается на вход 1 элемента 2, при этом передается сигнал на вход элементов 1 м и 2. Тактовым импульсом второй фазы первого такта считывается информация с .элемента 1 и согласно логике работы элемента, записанной в таблице, отрицательный сигнал с элемента 1 передается на вход 2 элемента 3. Импульсом третьей фа-зы положительный сигнал с элемента 3 передается на вход 3 элемента 5 и на вход k элемента 6. Положительный сигнал второго разряда первого слагаемого подается на вход 1, а положительный сигнал второ го слагаемого - на вход 2 элемента 1, при этом передается сигнал на вход элементов 1 и 2. Импульсом первой фазы второго такта отрицательный сигнал с элемента 5 передается на вход Ц элемента 7 и на вход 1 элемента 10, а отрицательный сигнал с элемента 6 - на вход 3 элемента 10, импульсом второй фазы положительный сигнал с элемента 1 передается на вход 1 элемента 3 и на вход k элемента 5, отрицательный сигнал с элемента 2 - на вход 4 элемента 3, а отрицательный сигнал с элемента 7 - на вход k элемента 9 импульсом третьей фазы отрицательный сигнал с элемента 9 выходит из сумматора, образуя первый разряд суммы. Положительный разряд третьего разряда второго слагаемого подается на вход 2 элемента 1, при этом передается сигнал на вход 4 элементов 1 и 2. Импульсом первой фазы третьего ;такта отрицательный сигнал с элемента 5 передается на вход k элемента 7 и на вход 1 элемента 10, импульсом второй фазы отрицательный сигнал с элемента 2 передается на вход 2 элемента 3, а отрицательный сигнал с элемента 7 - на вход k элемента 9 импульсом третьей фазы отрицательный сигнал с элемента 3 передается на вход 3 элемента t и на вход 1 элемента 6, отрицательный сигнал с элемента 9 выходит из сумматора, образуя второй разряд суммы, а положительный сигнал переноса с элемента10 передается на вход 1 элемента и на вход 2 элемента 8. Импульсом первой фазы четвертого такта положительный сигнал с элемента 6 передается на вход 2 элемента 10, импульсом бторой фазы положительный сигнал с элемента 8 передается на вход3 элемента 9, импульсом тре4-ьей фазы отрицательный сигнал с элемента 9 выходит из сумматора, образуя третий разряд суммы, а положительный сигнал переноса с элемента 10 передается на вход 1 элемента и на вход 2 элемента 8. Импульсом первой фазы пятого такта положительный сигнал с элемента А передается на вход 1 элемента 7.и на вход элемента 8, импульсом второй, фазы положительный сигнал с элемента 7 передается на вход 1 элемента 9 импульсом третьей фазы положитель

Авторы

Даты

1982-08-23—Публикация

1978-12-07—Подача