(54) ДВОИЧНЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Двоичный сумматор | 1976 |

|

SU638960A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Сумматор по модулю три | 1982 |

|

SU1057941A1 |

| Троичный сумматор | 1978 |

|

SU953637A1 |

| Сумматор по модулю три | 1976 |

|

SU669354A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

| Сумматор по модулю три | 1977 |

|

SU734684A1 |

| Двоичный п-разрядный счетчик импульсов | 1976 |

|

SU678675A1 |

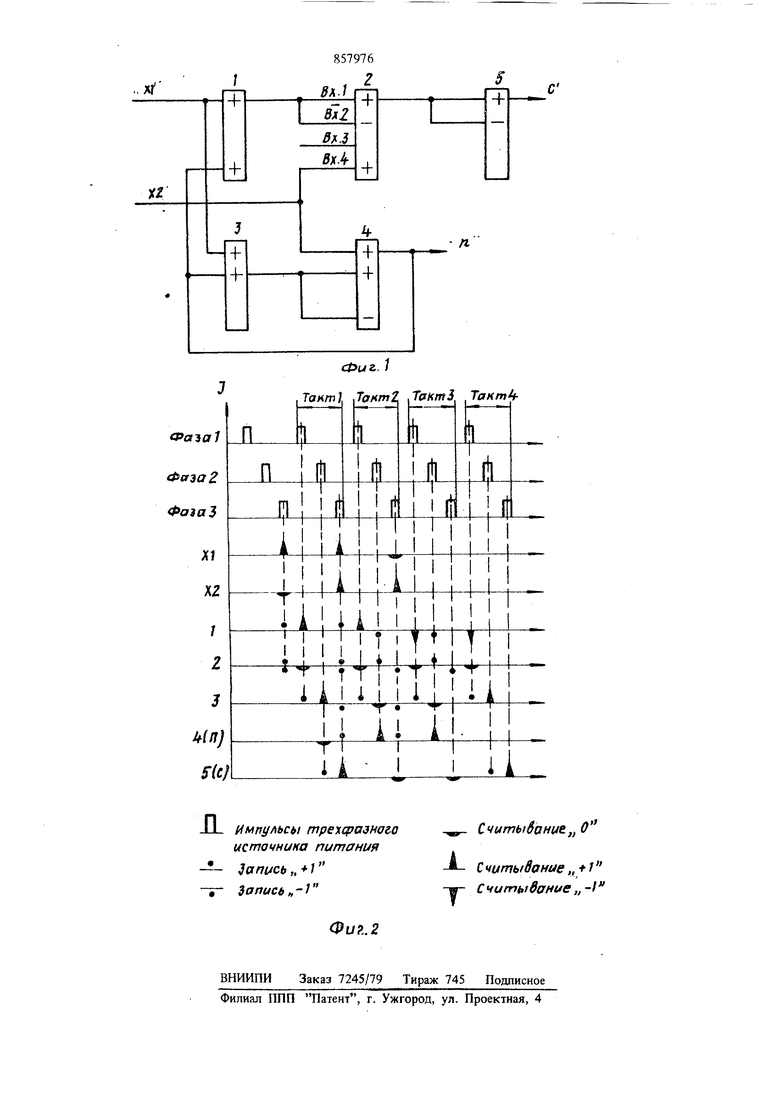

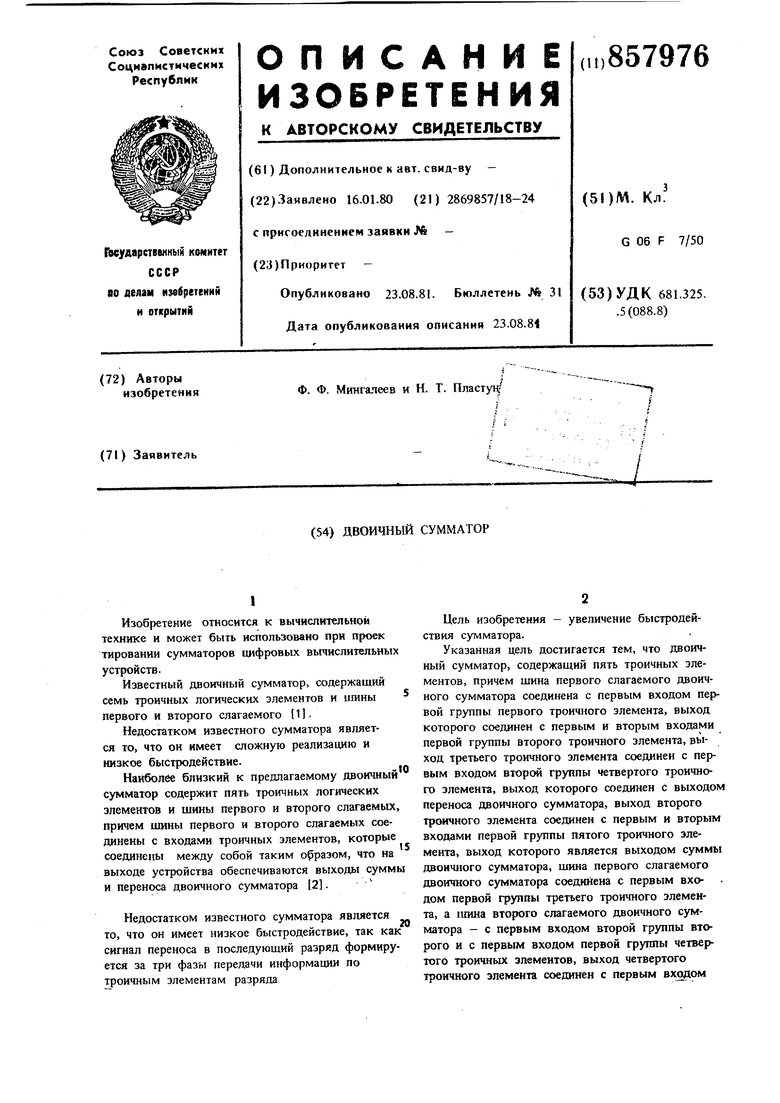

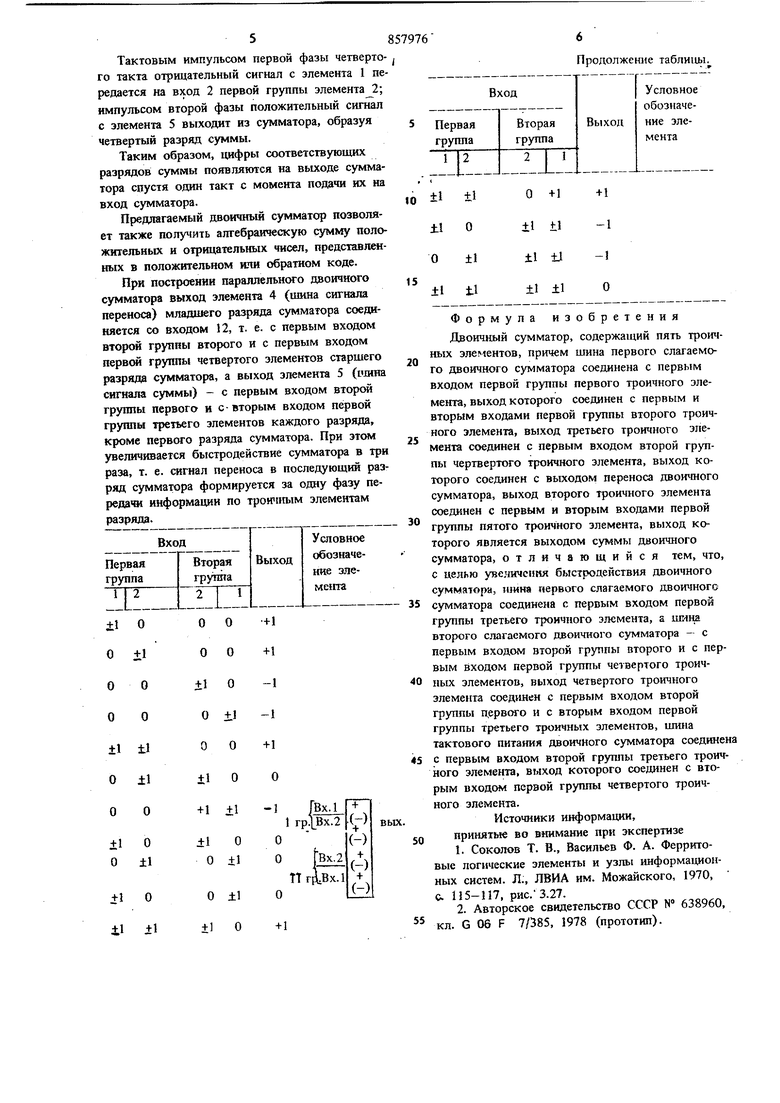

Изобретение относится к вычислительной технике и может быть использовано при проек тировании сумматоров цифровых вычислительны устройств. Известный двоичный сумматор, содержащий семь троичных логических элементов и шины первого и второго слагаемого 11 . Недостатком известного сумматора является то, что он имеет сложную реализацию и низкое быстродействие. Наиболее близкий к предлагаемому двоичный сумматор содержит пять троичных логических элементов и шины первого и второго слагаемых причем шины первого и второго слагаемых соединены с входами троичных элементов, которые соединены между собой таким образом, что на выходе устройства обеспечиваются выходы сумм и переноса двоичного сумматора 2. Недостатком известного сумматора является то, что он имеет низкое быстродействие, так как сигнал переноса в последующий разряд формиру ется за три фазы передачи информации по троичным элементам разряда Цель изобретения - увеличение быстродействия сумматора. Указанная цель достигается тем, что двоичный сумматор, содержащий пять троичных элементов, причем шина первого слагаемого двоичного сумматора соединена с первым входом первой группы первого троичного элемента, выход которого соединен с первым и вторым входами первой группы второго троичного элемента, выход третьего троичного элемента соединен с первым входом второй группы четвертого троичного элемента, выход которого соединен с выходом переноса двоичного сумматора, выход второго троичного элемента соединен с первым и вторым входами первой группы пятого троичного элемента, выход которого является выходом суммы двоичного сумматора, шина первого слагаемого двоичного сумматора соедийена с первым входом первой группы третьего троичного элемента, а шина второго слагаемого двоичного сумматора - с первым входом второй группы второго и с первым входом первой группы четвертого троичных элементов, выход четвертого троичного элемента соединен с первым входом второй группы первого и с вторым входом пер вой группы третьего троичных элементов, шина тактового питания двоичного сумматора соединена с первым входом второй группы третьего троичного элемента, выход которого соединен с вторым входом первой группы четвертого троичного элемента. Этим увеличивается быстродействие сумматора, т. е. сигнал переноса в последующий разряд сумматора формируется за две фаэы передачи информации по троичным элементам разряда. В таблиде представлены троичные операции пяти элементов, на которых выполняется разряд двоичного сумматора. Указанные операции образуют функционально полную систему логических функций и могут быть реализованы на основе троичных элементов. На фиг. 1 представлена функциональная схема двоичного сумматора; на фиг. 2 - временная диаграмма работы двоичного сумматора при сложении двух положительных чисел 3 и 6. Функциональная схема двоичного сумматора содержит троичные элементы 1, 2, 3, 4 и 5 (фиг. 1). Шина первого слагаемого XI соединена с первыми входами первой группы первого и тре гьего троичных элементов 1 и 3. Шина второго слагаемого Х2 соединена с первым входом второй группы второго и с первым входом первой группы четвертого троичных элементов 2 и 4. Выход первого троичного элемента 1 соединен с первым и вторым входами первой группы второго троичного элемента 2. Выход второго троичного элемента 2 соединен с первым и вторым входами первой группы пятого элемента 5 формирующего сигнал с окончательной суммы даоичного сумматора. Выход третьего троичного элемента 3 соединен с вторым первой группы и первым второй группы входами четвертого троичного элемента 4, формирующего сигнал п окончательного переноса двоичного сумматора. Выход четвертого троичного элемента 4 (шина сигнала переноса) соединен с первым входом второй группы первого и с вторым входом первой группы третьего элементов 1 и 3. Система тактового питания схемы сумматор трехфазная, при этом каждый следующий разряд слагаемого поступает на вход сумматора через три фазы (один такт) передачи информации по элементам схемы (фиг. 2). Тактовым импульсом первой фазы считывается информация с троичных элементов 1 и 3, второй фазы - с троичных элементов 2 и 4, третьей фаэы - с троичных элементов 5. Разряды . слагаемого поступают на вход двоичного сумматора по щинам XI и Х2 во время тактового импульса третьей фазы. Третья щина тактового питания (фаза 3) соединена с первым входом второй группы троичного элемента 3 (в графическом изображении элемента-Т). Это означает, что на этот вход во время тактового импульса третьей фазы каждого такта подается сигнал, т, е. при отсутствии импульсов на щинах XI и Х2 троичный элемент 3 является генератором сигналов отрицательной полярности. Рассмотрим работу двоичного сумматора на примере суммирования двух положительньк чисел 3 и 6. Первое слагаемое, число 3, в двоичной системе счисления представляется положительными сигналами в первом и втором разрядах. Второе слагаемое, число 6, представляется отсутствием сигнала в первом разряде и положительными сигналами во втором и третьем разрядах. Положительный сигнал первого разряда первого слагаемого подается на вход 1 первой группы элементов 1 и 3, при зтом передается сигнал на вход 1 второй группы элемента 3 (фиг. 1 и 2). Тактовым импульсом первой фазы первого такта считывается информаадя с элемента 1, и согласно логике работы элемента, записанной в таблице, положительный сигнал с элемента 1 передается на вход 1 перасй группы элемента 2; импульсом второй фазы положительный сигнал с элемента 2 передается на вход 1 первой группы элемента 5; импульсом третьей фазы положительный сигнал с элемента 5 выходит из сумматора, образует первый разряд суммы, одновременно положительный сигнал второго разряда первого слагаемого подается на вход 1 первой группы элементов 1 и 3, а второго слагаемого - на вход 1 второй группы элемента 2 и на вход 1 первой группы элемента 4, при этом передается сигнал на вход 1 второй группы элемента 3. Тактовым импульсом первой фазы второго такта положительный сигнал с элемента 1 передается на вход 2 первой группы элемента 2; импульсом второй фазы положительный сигнал с элемента 4 (сигнал переноса) передается на вход 1 второй группы элемента 1 и на вход 2 первой группы элемента 3; во время тактового импульса третьей фазы положительный сигнал третьего разряда второго слагаемого подается на вход 1 второй группы элемента 2 и на вход 1 первой группы элемента 4, при этом передается сигнал на вход 1 второй группы элемента 3. Тактовым импульсом первой фазы третьего такта отрицательный сигнал с элемента 1 передается на вход 2 первой группы элемента 2; импульсом второй фазы положительный сигнал с элемента 4 (сигнал переноса) передается на вход 1 второй группы элемента 1 и на вход 2 первой группы элемента 3; во время тактового импульса третьей фазы сигнал передается на вход второй группы элемента 3. 5 Тактовым импульсом первой фазы четверто го такта отрицательный сигнал с элемента 1 пе редается на вход 2 первой группы элемента 2; импульсом второй фазы положительный сигнал с элемента 5 выходит из сумматора, образуя четвертый разряд суммы. Таким образом, цифры соответствующих разрядов сумгяы появляются на выходе сумматора спустя один такт с момента подачи их на вход сумматора. Предлагаемый двоичный сумматор позволяет также получить алгебраическую сумму поло жительных и отрицательных чисел, представленных в положительном или обратном коде. При построении параллельного двоичного сумматора выход элемента 4 (шина сигнала переноса) младшего разряда сумматора соединяется со входом 12, т. е. с первым входом второй группы второго и с первым входом первой группы четвертого элементов старшего разряда сумматора, а выход элемента 5 (ишна сигнала суммы) - с первым входом второй группы первого и с-вторым входом первой группы третьего элементов каждого разряда, кроме первого разряда сумматора. При этом увеличивается быстродействие сумматора в три раза, т. е. сигнал переноса в последующий разряд сумматора формируется за одну фазу переда ш информации по троинп.1м элементам разряда. 11 ±1 6 Продолжение таблицы. Двоичный сумматор, содержащий пять троичных элементов, причем шина первого слагаемого двоичного сумматора соединена с первым входом первой группы первого троичного элемента, выход которого соединен с первым и вторым входами первой группы второго троичного элемента, выход третьего троичного элемента соединен с первым входом второй группы чертвертого троичного элемента, выход которого соединен с выходом переноса двоичного сумматора, выход второго троичного элемента соединен с первым и вторым входами первой группы пятого троичного элемента, выход которого является выходом суммы двоичного сумматора, отличающийся тем, что, с целью увеличс1 О1 быстродействия двоичного сумматора, тина первого слагаемого двоичного сумматора соединена с первым входом первой группы третьего троичного элемента, а шина второго слагаемого двоичного сумматора - с первым входом второй группы второго и с первым входом первой группы четвертого троичных элементов, выход четвертого троичного элемента соединен с первым входом второй группы дервого и с вторым входом первой группы третьего троичных элементов, илша тактового питания двоичного сумматора соединена с первым входом второй группы третьего троичного элемента, выход которого соединен с вторым входом первой группы четвертого троичного элемента. Источники информации, принятые во внимание при экспертизе 1.Соколов Т. В., Васильев Ф. А. Ферритовые логические элементы и узлы информационных систем. Л., ЛВИА им. Можайского, 1970, с. 115-117, рис.3.27. 2.Авторское свидетельство СССР № 638960, кл. G 06 F 7/385, 1978 (прототип).

Авторы

Даты

1981-08-23—Публикация

1980-01-16—Подача