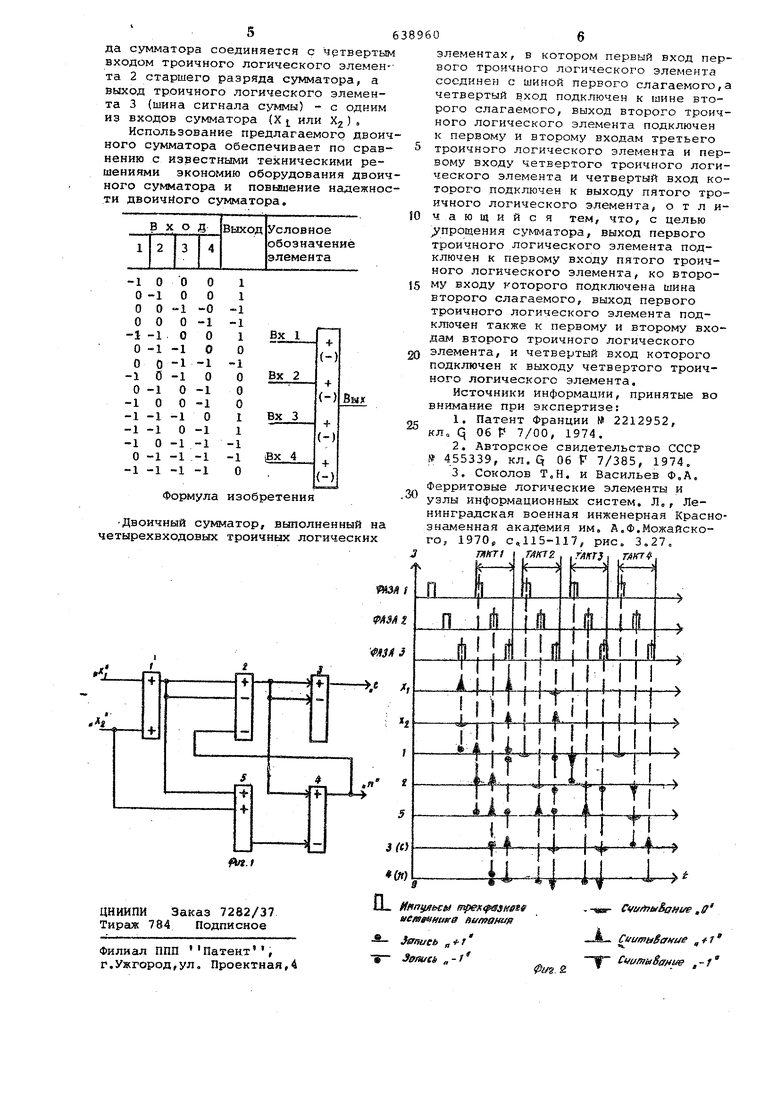

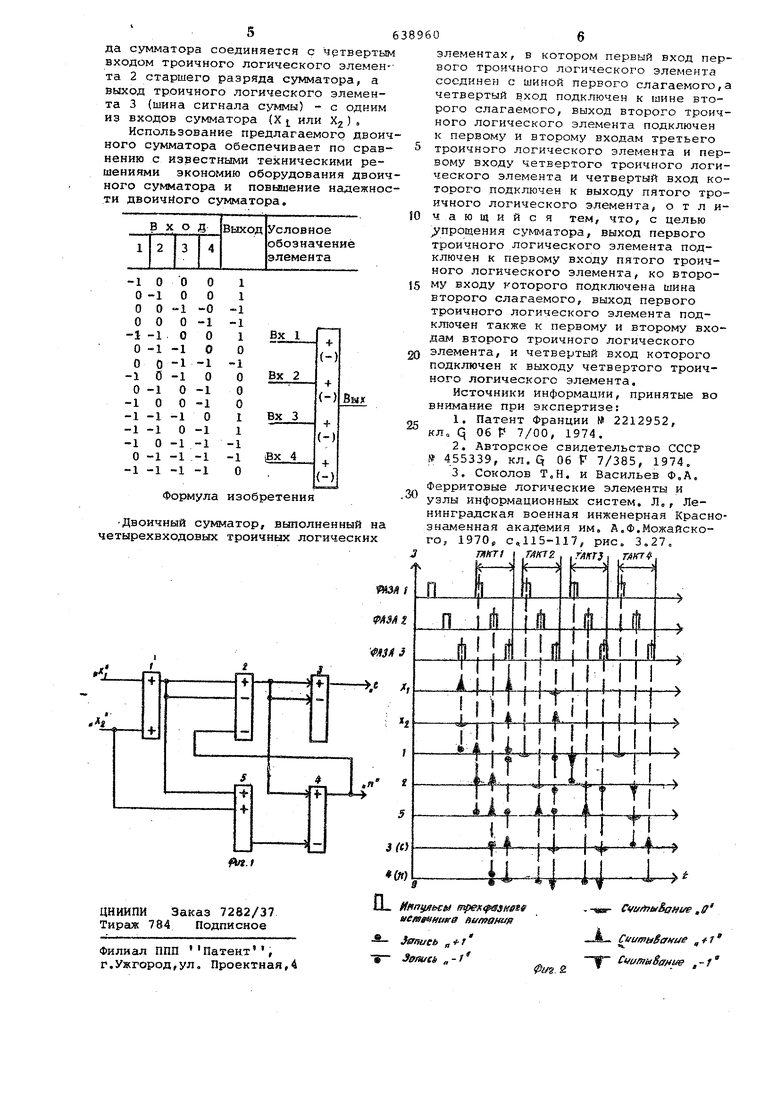

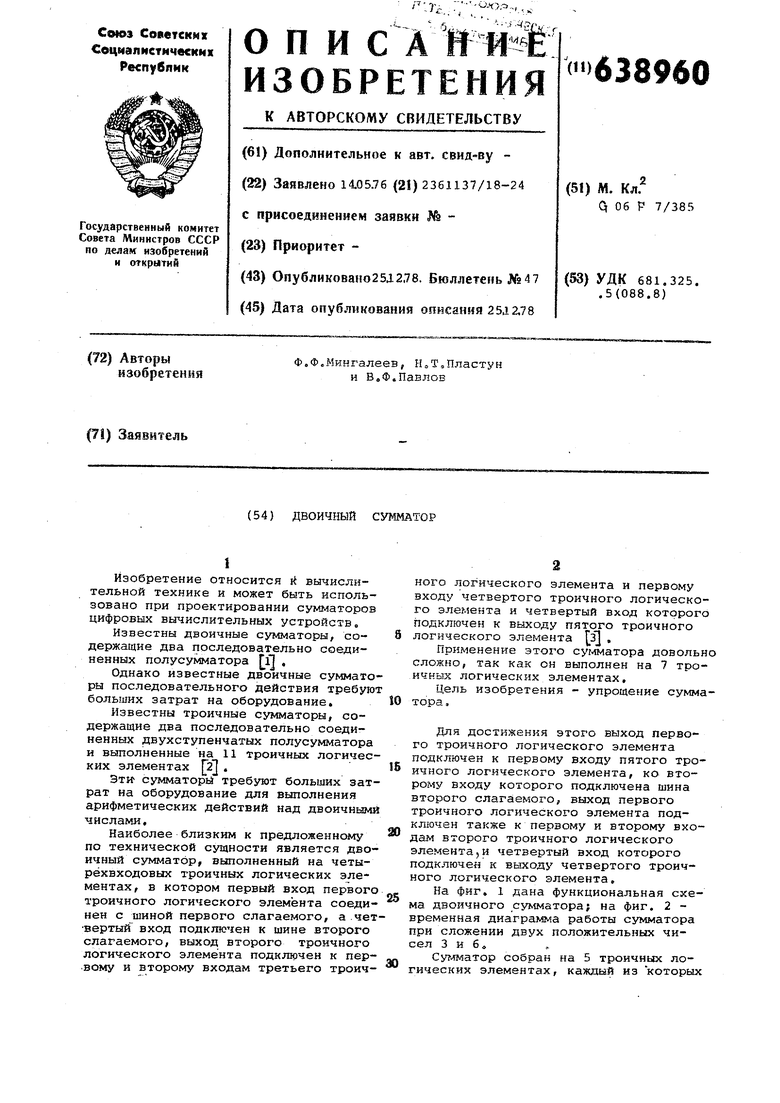

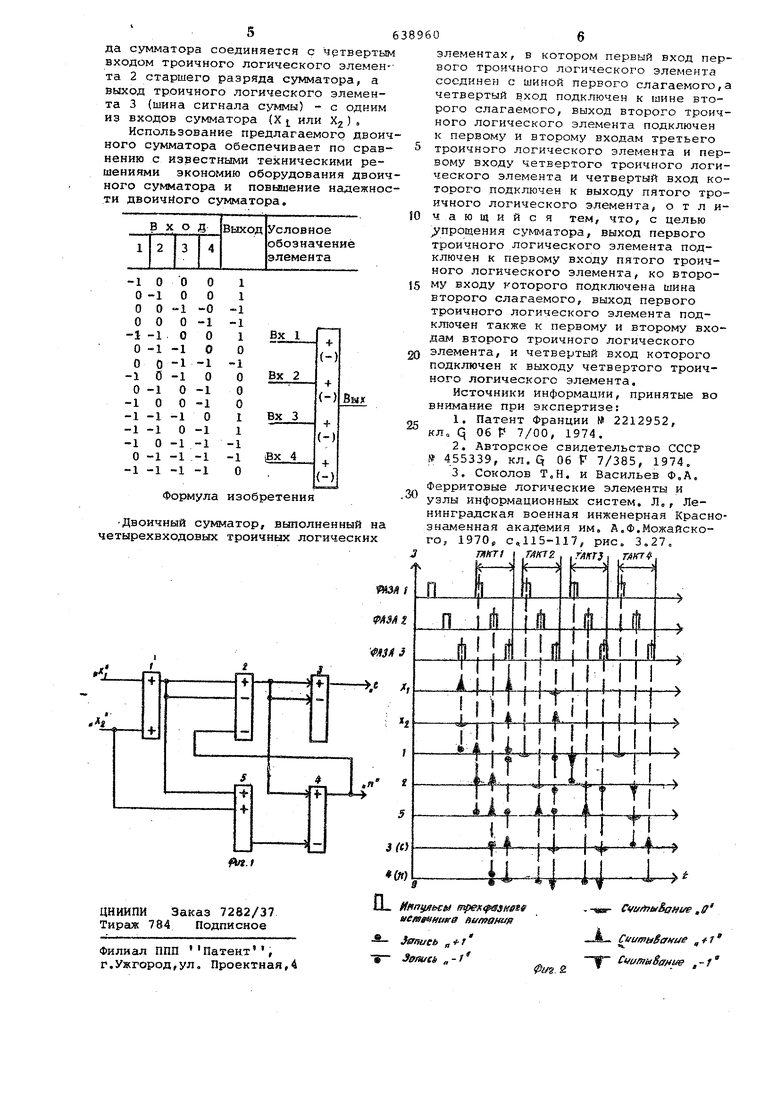

изобретение относится k вычислительной технике и может быть использовано при проектировании сумглаторов цифровых вычислительных устройств. Известны двоичные сумматоры, содержащие два последовательно соединенных полусумматора i . Однако известные двоичные суммато ры последовательного действия требую больших затрат на оборудование. Известны троичные сумматоры, содержащие два последовательно соединенных двухступенчатых полусумматора и выполненные на 11 троичных логических элементах 2J . ЭТИ сумматор требуют больших затрат на оборудование для выполнения арифметических действий над двоичными числами. Наиболее близким к предложенному по технической сущности является двоичный сумматор, выполненный на четырёхвходовых троичных логических элементах, в котором первый вход первого троичного логического элемента соединен с шиной первого слагаемого, а .чет вертый вход подключен к шине второго слагаемого, выход второго троичного логического элемента подклизчен к первому и второму входам третьего троичкого логического элемента и первому входу четвертого троичного логического элемента и четвертый вход которого подключен к выходу пятого троичного логического элемента 3 , Применение этого суГЛматора довольно сложно, так как он выполнен на 7 троичных логических элементах. Цель изобретения - упрощение сумматора. Для достижения этого выход первого троичного логического элемента подключен к первому входу пятого троичного логического элемента, ко второму входу которого подключена шина второго слагаемого, выход первого троичного логического элемента подключен также к первому и второму входам второго троичного логического элемента,и четвертый вход которого подключен к выходу четвертого троичного логического элемента. На фиг. 1 дана функциональная схема двоичного сумматора; на фиг. 2 временная диаграмма работы сумматора при сложении двух положительных чисел 3 и 6, Сумматор собран на 5 троичных логических элементах, каждый из которых выполняет троичные операции, приведенные в таблице. Эти операции образуют функционально полную систему логических функций и могут быть реализованы на основе троичных логических элементов (например, на ферритовых логических элементах) , Шины первого и второго слагаемых. Xj и Xg соединены с первым и четвертым входами первого троичного логичес кого элемента 1, выход которого подключен к .первому и второму входам второго троичного логического элемента 2 , выход которого подключен к первому и второму входам третьего троичного логического элемента 3, формирующего сигнал окончательной суммы С, и первому входу четвертого троичного логического элемента 4, формирующего сигнал переноса П. Вьзход четвертого троичного логического элемента 4 подключей к четвертому входу второго троичного логического элемента 2. Пер вый и второй входы пятого троичного логического -элемента 5 соединены соот ветственно с выходом первого троичног логического элемента 1 и шиной второг слагаемого Xj,, Выход пятого троичного элемента 5 подключен к четвертому входу четвертого троичного логического, элемента 4 Система тактового питания схенаг сумматора трехфазная, при этом каждый следующий разряд слагаемого поступае на вход сумматора через три фазы (один .такт) передачи информации-по элементам схемы, Тактовыр/ импульсом первой фазы сч тнваегся информация с троичного логи ческого элемента 1, второй фазы - с троичных логических .элементов 2 и 5, третьей фазы - троичных логических элементов 5 и 4, Разряды слагаемого поступают на вход сумматора по шинам Х| и Х во время тактового импульса третьей фазыв Рассмотрим работу сумматора на примере суммирования двух -положитель ных чисел 3 и 6„ Первое сла.гаемое число 3 в двоичной системе счисления представляется положительными сигналами в первом и втором разрядах. Вто рое слагаемое - число б представляет ся отсутствием сигнала в первом разряде и положительными сигналами во втором и третьем разрядах. Положительный сигнал первого разр да первого слагаемого подается на пе вый вход троичного логического элеме та 1. . Тактовым импульсом перврй фазы пе вого такта считывается информация с троичного логического элемента 1 и согласно логике работы элемента, при веденной в таблице, положительный сигнал с троичного логического элемента 1 передается на первый вход троичных логических элементов 2 и 5| импульсом второй фазы положительный сигнал с троичного логического элемента 2 передается на первый вход троичных логических элементов 3 и 4, а с троичного логического элемента 5 передается на четвертый вход троичного ло1ического элемента 4; импульсом третьей фазы положительный сигнал с троичного логического элемента 3 выходит из сумматора, образуя первый разряд суммы, одновременно положительный сигнал второго разряда первого слагаемого подается на первый вход троичного логического элемента 1, а второго слагаемого - на четвертый вход троичного логического элемента 1 и второй вход троичного логического элемента 5, Импульсом второй фазы второго такта положительный сигнал с троичного логического элемента 5 передается на четвертый вход троичного логического элемента 4 импульсом третьей фазы отрицательный сигнал с троичного логического элемента 4 (сигнал переноса) йёредается на четвертый вход троичного логического элемента 2, одновременно положительный сигнал третьего разряда второго слагаемого подается на четвертый вход троичного логического элемента 1 и второй вход троичного логического элемента 5, Импульсом первой фазы третьего такта отркдательный сигнал с троичного логического элемента 1 передается на второй вход троичного логического элемента 2j импульсом второй фазы по.ложительный сигнал с троичного логи-. ческого элемента 5 передается на четвертый вход троичного логического элемента 4I импульсом третьей фазы отрицательный сигнал с троичного логического элемента 4 (сигнал переноса) передается на четвертый вход троичного логического элемента 2, Импульсом второй фазы четвертого такта отрицательный сигнал с троичного логического элемента 2 передается.. на второй вход троичного логического элемента .3 г импульсом третьей фазы Положительный сигнал с троичного логигеского элемента 3 выходит из суммйтора образуя четвертый разряд суммы, образом/ цифры соответствующих разрядов cym/sK появляются на выходе сумматора спустя один такт с момента подачи их на вхрд сумматора Предложенный сумматор позволяет так5ке получить алгебраическую сумму положительных и отрицательных чисел, представленных в дополнительном или обратном коде, Так работает последовательный двоичный cyMf/iaTOp. При построении параллельного двоичного сумматора выход троичного логического- элемента 4 (шина сигнала переноса) младшего разряда сумматора соединяется с четверты входом троичного логического элемен та 2 старшего разряда сумматора, а вьоход троичного логического элемента 3 (шина сигнала суммы) - с одним из входов сумматора (X j или Xg ) . Использование предлагаемого двои ного сумматора обеспечивает по срав нению с известными техническими решениями экономию оборудования двои ного сумматора и повышение надежно ти двоичного су матора. Формула изобретения Двоичный сумматор, выполненный н четырехвходовых троичных логических элементах, в котором первый вход первого троичного логического элемента соединен с шиной первого слагаемого,а четвертый вход подключен к шине второго слагаемого, выход второго троичного логического элемента подключен к первому и второму входам третьего троичного логического элемента и первому входу четвертого троичного логического элемента и четвертый вход которого подключен к выходу пятого троичного логического элемента, отличающийся тем, что, с целью упрощения cy мaтopa, выход первого троичного логического элемента подключен к первому входу пятого троичного логического элемента, ко второму входу которого подключена шина второго слагаемого, выход первого троичного логического элемента подключен также к первому и второму входам второго троичного логического элемента, и четвертый вход которого подключен к выходу четвертого троичного логического элемента. Источники информации, принятые во внимание при экспертизе: 1.Патент Франции № 2212952, кл. q Об Р 7/00, 1974. 2.Авторское свидетельство СССР № 455339, кл.Q 06 V 7/385, 1974. 3.Соколов Т.Н. и Васильев Ф,А. Ферритовые логические элементы и узлы информационных систем. Л, Ленинградская военная инженерная Краснознаменная академия им. А.Ф.Можайского, 1970, с,115-117, рис. 3,27с

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Двоичный сумматор | 1980 |

|

SU857976A1 |

| Сумматор по модулю три | 1976 |

|

SU669354A1 |

| Сумматор по модулю три | 1982 |

|

SU1057941A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Троичный сумматор | 1978 |

|

SU953637A1 |

| Сумматор по модулю три | 1977 |

|

SU734684A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Троичный сумматор | 1972 |

|

SU455339A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

Авторы

Даты

1978-12-25—Публикация

1976-05-14—Подача