. Изобретение относится к области автоматизации управления кбнтурйгам перемещением рабочих органов автоматических устройств и предназначено для использования в системах про раммного управления группой объ Ктов. Известно устройство для программного управдекия, содержащее блоки вычислений, вшода программы к oneративнрй памяти, блоки рабпределе ния и блоки управления {ij . Недостатком известного устройства является низкая наг-рузрчная способность Известно также устройство, содер жащее блок местного управления, бло ввода программы,оперативную память, исполнительныйблок и вычислительный блок, причем первый и второй информационные входы вычислительного бдокд подключены соответственно к выходу блока ввода программы и первому выходу оперативной памяти, информационный вход которой соединен с первым информационным выходом вычислительного блока, управляющий и адресный выходы которого соединены соответственно с первым управляю щим входом исполнительного блока и первым адресным входом блока мвстнего управлания, первый, второй, третий и четвертый управляющие выходы которого подключены к управляющим . вхолам соответственно вычислительного блока, блока ввода программы, . оперативной памяти и второму управляющему входу исполнительного блока, адресный выход блока местного управления пойключен к адресному входу оперативной памяти, информационный вход блока программы средвнен со входом устройства, выход которого соединен с выходом исполнительного блока f2j. Недостаток этого устройства.состоит в Том, что приоритет управляемых объектов определяется только по их номерам без учета распределения запросов по номерам скоростей, что приводит к снижению нагрузочной способности устройства и производительности обслуживаемых объектов. Целью предлагаемого изобретения является увеличение нагрузочной способности устройства, С этой целью в предлагаемое устройство введены генератор дискретHHic частот и блок формирования запросов, причем первый и второй инфор-.

ационные входы блока формирования запросов соединены соответственно со вторым информационным выходом вычислительного блоха и вторым выходом оперативной памяти, пятый правляющий выход блока местного управления подключен к управляюще- 5 у входу блока формирования запроов, запросный вход которого соедиен с выходом генератора дискретных астот, выход блока формирования запросов подключен ко второму адрес- Q ному входу блока местного управления; кроме того, блок формирования запросов содержит формирователь адреса микрокоманд, коммутатор заявок, регистр заявок, регистр состояния jc объектов, дешифратор анализа скоостей, схему сравнения, регистр запросов, коммутатор запросов, регистр номеров скоростей, первый, второй, третий, четвертый и пятый элементы и, причем выход формирователя адре- са микрокомайд подключёГн к вйхд дУ . блока формирования запросов, выход коммутатора заявок подключен к пёр- ; вому входу формирователя адреса микрокоманд и информационным входам пер- 25 вого и второго элементов И, второй и третий входы формирователя адреса микрокоманд соединены соответственно с выходом дешифратора анализа скоростей и выходом схемы срайнения, 30 выход коммутатора запросов соединен с четвертым входом формирователя адреса микрокоманд, информационным входом третьего элемента И и первым входом схема сравнения, второй вход 35 которой соединен с информационным входом коммутатора запросов, и выходом Регистра запросов, выхой пёрвого элемента и подклю чен к первому нулевому входу регистра заявок и к ну- д« левому входу регистра состояния объек-. тов, первый и второй единичные входы которого соединены соответственно с выходом второго и четвертого элементов И, информационный вхОй которогосоединён с выходом регистра 5 заявок и первым входом коммутатора заявок, второй вход которого соединен с выходом регистра состояния объектов и первым входом дешифраToj5a анализа скоростей, второй вход 50 которого соединен с ва5содОй-рё1Т1ст а номеров скоростей и первым входом пятого элемента И, второй вход которого подключен к запросному входу 4лрка формирования запросов, выход 55 третьего элемента И подключён к нулевому входу регистра запросов, единичный вход которого соединен с выходом пятого элемента И, вход регистра HONtepOB скоростей соединен с пер- Q вым информационным входом блока формирования запросов, второй информационный вход котбрюго соёдийёй с единичным входом регистра эайвок, управляющий вход формирователя адреса мйк- j рокоманд соединен с управляющим входом коммутатора заявок, вторам нулевым входом регистра заявок, управляющим входом первого, второго, третьего, четвертого элементов И, упраляющим входом коммутатора запросов и с управляющим входом блока формирования запросов.

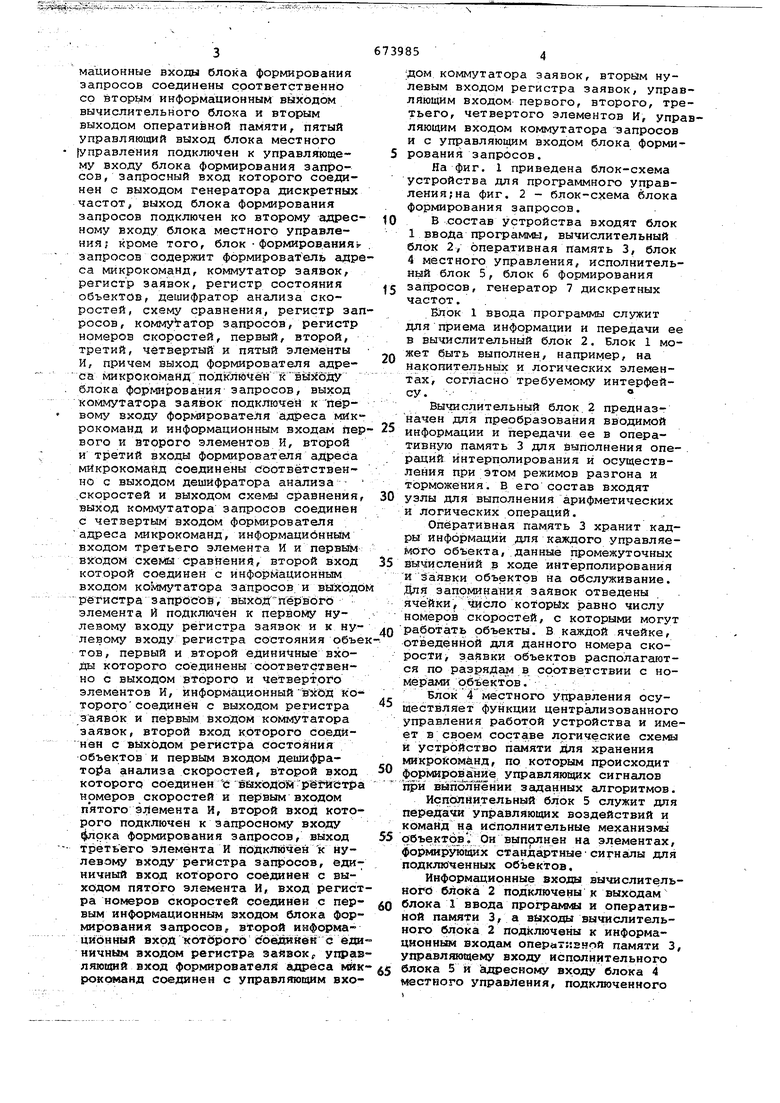

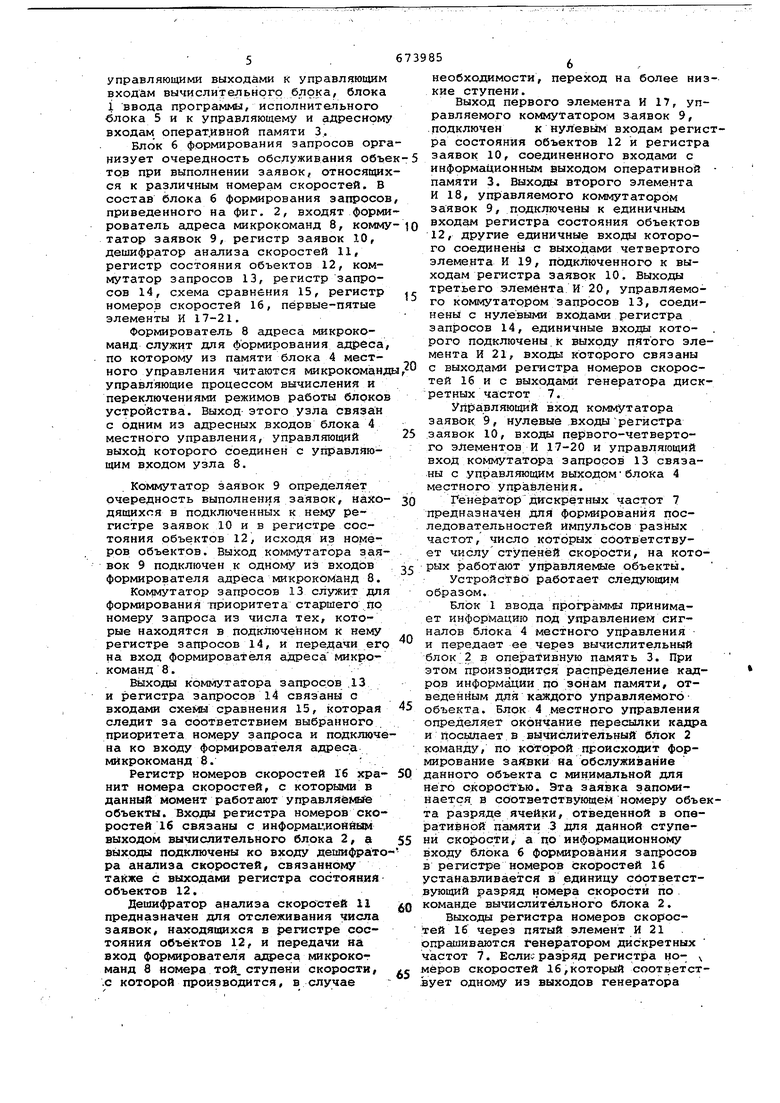

На фиг. 1 приведена блок-схема устройства для программного управления; на фиг. 2 - блок-схема блока формирования запросов.

В .состав устройства входят блок 1 ввода программы, вычислительный блок 2, оперативная память 3, блок 4 местного управления, исполнительный блок 5, блок 6 формирования запросов, генератор 7 дискретных частот. .

Блок 1 ввода программы служит для приема информации и передачи ее в вычислительный блок 2. Блок 1 может быть выполнен, например, на накопительных и логических элементах, согласно требуемому интерфейсу. . . ,

Вычислительный блок.2 предназначен для преобразования вводимой информации и передачи ее в оперативную память 3 для выполнения oneрадий интерполирования и осуществления при этом режимов разгона и торможения. В его состав входят узлы для выполнения арифметических и Логических операций.

Оперативная память 3 хранит кадры информации для каждого управляемого объекта, данные промежуточных вычислений в ходе интерполирования и Заявки объектов на обслуживание. Для запоминания заявок отведены ячейки, Число KOTOpfcJx равно числу номеров скоростей, с которыми могут работать объекты. В каждой ячейке, от Веденной для данного номера скорости, эайвки объектов располагаются по разрядам в соответствии с номерами о:б ектов. .

Блок 4 местного управления осуществляет функции централизованного управления работой устройства и имеет в своем составе логические схемы и уст ройство памяти Для хранения микрокоманд, по которым происходит формирование управляющих сигналов выполнении заданных гшгоритмов.

Исполнительный блок 5 служит для Передачи упра Вляющих воздействий и команд на исполнительные механизмы объект эв1 Он выполнен на элементах, формирующих стандартные-сигналы для подключенных объектов.

Информационные входы вычислительного блока 2 подключены к выходам блока 1 ввода программа и оперативной памяти 3, а выходы вычислительного блока 2 подключены к информационным входам оператигнрй памяти 3 управляющему входу исполнительного блока 5 и Адресному входу блока 4 MecTfioro управления, подключенного управляющими выходами к управляющим входам вычислительного блока, блока 1 ввода программы, исполнительного блока 5 и к управляющему и адресном входам операт.Ивной памяти 3. Блок 6 формирования запросов орг низует очередность обслуживания объ трв при выполнении заявок, относящи ся к различным номерам скоростей. В состав блока 6 формирования запросо приведенного на фиг. 2, входят форм рователь адреса микрокоманд 8, комм татор заявок 9, регистр заявок 10, дешифратор анализа скоростей 11, регистр состояния объектов 12, коммутатор запросов 13, регистр запросов 14, схема сравнения 15, регистр номеров скоростей 16, первые-пятые элементы И 17-21. Формирователь 8 адреса микрокоманд служит для формирования адреса по которому из памяти блока 4 местного управления читаются микрокоман управляющие процессом вычисления и переключениями режимов работы блоко устройства. Выход этого узла связан с одним из адресных входов блока 4 местного управления, управляющий выход которого соединен с управляющим входом узла 8. Коммутатор заявок 9 определяет очередность выполнения заявок, нахо дящихся в подключенных к нему регистре заявок 10 и в регистре состояния объектов 12, исходя из номеров объектов. Выход коммутатора зая вок 9 подключен к одному из входов формирователя адреса микрокоманд 6. Коммутатор запросов 13 служит дл формирования приоритета старшего по номеру запроса из числа тех, которые находятся в подключенном к нему регистре запросов 14, и передачи его на вход формирователя адресамикрокоманд 8. Выходы коммутатора запросов .13 и регистра запросов 14 связаны с входами схемы сравнения 15, которая следит за соответствием выбранного . приоритета номеру запроса и подклк че на ко входу формирователя адреса микрокоманд 8. Регистр номеров скоростей 16 хранит номера скоростей, с которыми в данный момент работают управляем: объекты. Входы регистра номеров скоростей 16 связаны с информаи,иоййым выходом вычислительного блока 2, а выходы подключены ко входу дешифрато ра анализа скоростей, связанному также с выходами регистра состояния объектов 12, Дешифратор анализа скоростей 11 предназначен для отслеживания числа заявок, находяпщхся в регистре состояния объектов 12, и передачи на вход формирователя адфеса микроког манд 8 номера той. ступени скорости, .с которой производится, в случае необходимости, переход на более низкие ступени. Выход первого элемента И 17, управляемого коммутатором заявок 9, .подключен к нулевьЬи входам регистра состояния объектов 12 и регистра заявок 10, соединенного входами с информационным выходом оперативной памяти 3. Выходы второго элемента И 18, управляемого коммутатором заявок 9, подключены к единичным регистра состояния объектов 12, другие единичные входы которого соединены с выходами четвертого элемента И 19, подключенного к выходам регистра заявок 10. Выходы третьего элемента И 20, управляемого коммутатором запросов 13, соединены с нулевыми входами регистра запросов 14, единичные входы которого подключены к выходу пятого элемента И 21, входы которого связаны с выходами регистра номеров скоростей 16 и с выходами генератора дискретных частот 7. Управляющий вход коммутатора заявок 9, нулевые входы регистра заявок 10, входы первого-четвертого элементов И 17-20 и управляющий вход коммутатора запросов 13 связаны с управляющим выходомблока 4 местного управления. TeHepat-op дискретных частот 7 предназначен для формирования последовательностей импульсов разных частот, число которых соответствует числу ступеней скорости, на которых работают управляемые объекты. Устройство работает следующим образом. .... Блок 1 ввода программы принимает информацию под управлением сигналов блока 4 местного управления и передает ее Через вычислительный блок 2 в оперативную память 3. При этом производится распределение кадров информации по зонам памяти, отведенным для каждого управляемого объекта. Блок 4 местного управления определяет окончание пересылки кадра и посылает в.вычислительный блок 2 команду, по которой происходит формирование заягвки на обслуживание данного объекта с минимальной для него скоростью. Эта заявка запоминается, в соответствующем номеру объекта разряде ячейки, отведенной в оперативной памяти 3 для данной ступени скорости, а по информационному входу блока б формирования запросов в регистре номеров скоростей 16 устанавливается в единицу соответствующий разряд номера скорости по . команде вычислительного блока 2. Выхода регистра номеров скоросгей 16 через пятый элемент И 21 прашиваются генератором дискретных астот 7. Если -раз1ряд регистра но- ёров скоростей 16,который соответстует одному из выходов генератора дискретных частот 7, находится в ед ничном состоянии, и на выходе генератора появляется опрашивающий импульс, то этот Импульс проходит на один из единичных входов рёгистрй э апроеов 14, уст аи авлив ая т ем самым запрос на обслуживание объектов, работающих на данйбй чистоте. Этот Запрос становится в очередь, в которой приб13йтёт запросов растётс увеличением номера скбростй. По командам блока 4 местного управлёнйя коммутатор запросов 13. предоставяйёт приоритет ста рШему пб нойёру запросу а форШрЩатёль ШШёса микрокоманд 8 формирует Адрёс, йачйная с которого is Влоке 4 местного управления записаны ко Майды flnW управления объектов, у которых имеются заявки для работы на данной скорости. Блок. 4 местного управления указывает по адресному входу оперативной памяти 3 на адрес ячейки, кото |5аяЬ вёденав Оперативной памяти 3дл й данной ступени скорости. Со-. держимре этой ячейки ; й a TWno информационным входам в регистре заявок 10, где заявки объектов ставятся в очередьсоотвёТс вёнИономерам объектов.Коммутатор заявок 9 прёдоставляет приоритет старшему . по номеру объекту, а ф615Ш1рователь адаеса микрокоманд Зфбрми-рует ajjpec, исходя из которого блок 4местного управления организует доступ вычислительно.го блока 2 в зону памяти, где хранйтся кадр информации данного объекта . Вычислительный блок 2 через ис. полнитель.ный блок 5 выдает управляю . щее воздействие или scnOMbsraf bHyro -.комМн лУ на исполнйгельнь й мвханизм объекта и подготавливает следующее приращение или команду. При этом величина ступени пути, которуй объект должен отработать с текущей, :скоростью, сравнивается с ,валичйно доставшегося перемещения по коорди нате, конечная которой задает ся, в кадре. Информация о з.элй-шнак ступеней пути, по которым проходит набор и сброс скорости разгоне и замедлении, для. кW5orp. объекта хранится в блоке 4 МёстногО управлё 1}йя. Если ступень Текущейскорости не отработана ;и анализ остaBaiefpCH (тути, заданного в каДре, не указыдаа.ет на необходимость перехода на р жим замедления, то вычислит сальный блок 2 освобоадается и пйдготайли ваётШ к абЬтв с к.адаом другого ; ббъекта.. Если Ьт1за6оГйа б 1Пёйй тё кущей скорости закончена, а оставшийся путь позволят уззеличить сКбрость отработки, то вычислительный блок 2 снимав заявку ЯаМогр объе та на обслуживайие с щзёйей часто той и 4РрКда Уёт в друг6Й яЧеЖкв и оперативной памяти 3 заявку обг ёкта на работу на более высокой ступени скорости. Если требуется перейти на режим замедления, то производится формирование заявки объекта на боле.е низкую частоту отработки перемещений. При переходе объекта с одной ступени скорости на другую произво цитея анализ содержимого обеих ячеек, освобождаемой и занимаемой заяв;Кой .данного объекта/ на наличие заявок других объектов, после чего формируется команда, которая по числовому входу блока б формирования запросов изменяет содержимое регистра 1€ номеров скоростей. После окончания обслуживания заявкй объекта и освобождения вычислительно Р 2 блок 4 местного управления выдает на блок б формирования запррсрв сигнал конец шага , который поступает на вхрды первого элемента И 17, управляемого коммутатором заявок 9, и сбра:сывает в нуль соответствующий разряд регистра заявок 10 .Затем из блока 4 «лестнрго управ.ления на коммутатор заявок 9прстуйает сигнал, по которому йредосзтаЩляется приоритет следующеfvsy по номеру объекту. . . Крг.да брдержимое регистра заявок 10станет разным нулю, т.е. обслуживч1ние будет предоставлено всем рбъе15Там, работающим с данной частотой, коммутатор 9 заявок через :формиррватель адреса микрокоманд 8 :сОЬб1Пит об. этом в блок 4 местного управ.г1ения. Из блока 4 местного управления на третий элемент И 20 управляемый кoм лyтaтopoм запросов 13, п.оступит сигнал, который установит в нуль соответствующий разряд регистра запросов 14, после чего крг.муТатор запррсов 13 предо.ставит приоритет следующему по номеру запросу на обслуживание заявок очередной ступени скорости. Если в момент обслуживания заявок какогр-.пибР номера скорости в регистр запросов 11 с генератора дискретных частот 7 поступит запрос бо.леё высокого приоритета, тр на выхо-, де схемы сравнения 15 появится скгиал р несоответствии номера поступившего запроса в регистре запррсов 14 тфгй рриТвту, сформированному коммутатр|5ом эапросрв 13. Этот сигнал через формйрЬватель адреса микроКоманд 8 сробдает в блок 4 местнрго у травлений р необходимости перехода на рбйлуживани более высокого но|мара скорости. Блок 4 местного управяения ожидает окончания обслуживания йЫчиСйительнргр блока 2 очереднрй заявки предаадущёй ступени скррости, прсле чего формирует команду, по КРгрррй Ъставшиеся заявки из регистра заявок 10 через чятвертый элемент И 19 переписываются в регистр сосгряння рбъектрв 12. Эти заявки лашифрируются крммутатрром заяврк 9 как находящиеся в режиме ожидания. По сигналам из блока 4 местного управ ния регистр заявок 10 очищается, а коммутатор запросов 13 формирует приоритет поступившего номера скор ти, который через формирователь адреса микрокоманд 8 инициирует в блоке 4 местного управления команду управления чтением заявок новой ступени скорости из оперативной па мяти 3 в регистр заявок 10, После этого производится обслуживание за Когда имеются заявки, находящие . ся в режиме ожидания в регистре со тояния объектов 12, то работа блок 6 формирования запросов протекает следующим образом. После чтения за вок очередной ступени скорости в регистре заявок 10 коммутатор 9 заявок сравнивает номера заявок в регистре заявок 10 и в регистре сос тояния объектов 12. Если имеются совпадающие номера, то приоритет предоставляется старшему изних. После окончания обслуживания заявки сигнал из блока 4 местного управления через первый элемент И 17 сбрасывает соответствующие разряда В регистре заявок 10 ив регистре состояния объектов 12. Дешифратор анализа скоростей 11 отслеживает число заявок, находящин ся в ожидании в регистре сосФЬйнйя объектов 12, и величину номеров в регистре номеров .скоростей 16 и, при необходимости, организует net eход на более низкие ступени ckop тей. При этом происходит форшров ние адреса ячейки старшего номера скорости, и содержимое этой ячейки по командам блока 4 местного управ-ленйя добавляется к содержимому, соседней ячейки, соответствующей на единицу меньшему номеру скорости, ав регистре номеров;скоростей 16 производится изменение номеров. Затем дешифратор анализа скороотей 11 анализирует новое распределение заявок. Когда кадр,информации для Данцого объекта отработан, блок 4 местного управления выдает сигнал VP нёц кадра , который через вторЪй элемент 18, управляеьвай коммутатор заявок 9, устанавливает в;единицу соответствующий разряд регистра .сое тояния объектов 12. Этот объект, . тем самым, ставится в очередь й& получение из блока 1 ввода программы следующего кадра. Результат моделирования работы устройства на ,ЭВМ при различных загрузках и распределениях объектов по быстродействию показали, что предлагавмое устройство допускает подключиние объектов примерно вдвое большего, по сравнений с известным быстродействия. Псэложительный эффект заключается в увеличении нагрузочной способности, что дойтигается за счет учета распределения запросов по номерам скорост ей, фиксации момента насыщения системы дйспетгеризации заявок на обслуживание и использование возможности перевода заявок на более низкие частоты обслуживания путем определения требуемой ступени скорости по известным пар-аметрам, хранимым внутри устройства. Формула изобретения 1. Устройство для программного управления, содержащее блок местного управления, блок ввода программы, оперативную память, исполнительный блок и. вычислительный блок, причем первый и второй информационные входы вычислительного блоки подключены соответственно к выходу блока В1вода программы и первому выходу оперативной .памяти,информационный вход которой соединен с пёрвйм информационным выходом вычислительного блока, управляющий И ;адресный выходы которого соединены соответственно с первым управляющим входом Исполнительного блока и деШШШресйым входом блока местного упраЁ Яенйя, первый, второй, :трётий.и четзвертый. управляющие вы;ХОды которого подключены к управляюьщм вхЬдам соОтветственно. вычислительного ёлока, блока ввода программы, оперативной памяти и второму З/прайляющему входу исполнительного блока, адресный.выход блока местногО управления подключен к адресному входу оперативной памяти, информационный вход блока ввода программы соединен сО вхОдОм устройства, выход которого соединен с выходом исполнительного блока, о .т л и ч аto щ ее с. я тем, что, с целью увеличения нагрузочной способности, в устройство введена генератор дискретных частот и блок формирования запросов, причем первый и второй информационные вхОдел блока формирования запросов соединены соответстьенйо со вторым информационным выходом вычислительного бдока и ;выходои Оперативной памяти, пятый управляющий выход блока местного управления подключен к управляющему входу блока формирования запросов, запросный вход которого соединен с выходом генератора дискретных частот, выход блока формирования запросов подключен ко второму адресному вхоу блока местного управления. 2. Устройство по П.1, о т л и ай щ е е тем, что блок форирования запросов содержит форми

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

Авторы

Даты

1979-07-15—Публикация

1976-06-03—Подача