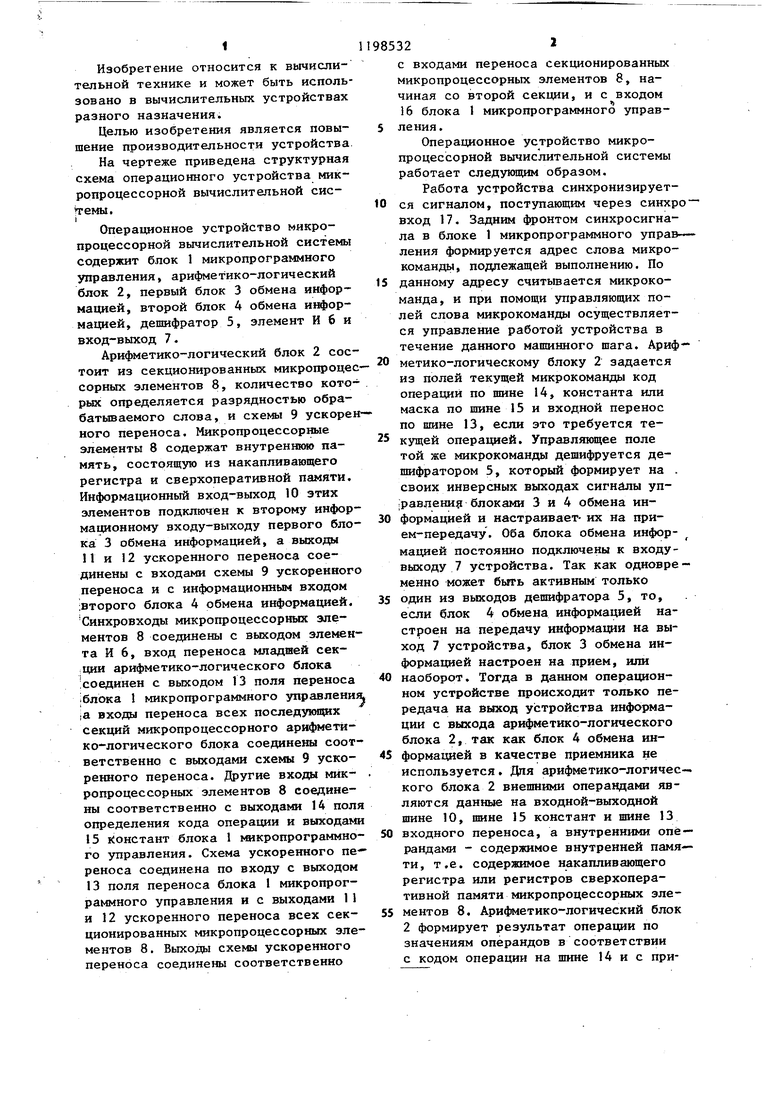

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах разного назначения. Целью изобретения является повышение производительности устройства На чертеже приведена структурная схема операционного устройства микропроцессорной вычислительной сисОперационное устройство микропроцессорной вычислительной системы содержит блок 1 микропрограммного управления, арифметико-логический блок 2, первый блок 3 обмена информацией, второй блок 4 обмена информацией, дешифратор 5, элемент И 6 и вход-выход 7. Арифметико-логический блок 2 состоит из секционированных микропроцес сорных элементов 8, количество которых определяется разрядностью обрабатываемого слова, и схемы 9 ускорен ного переноса. Микропроцессорные элементы 8 содержат внутреннюю память, состоящую из накапливающего регистра и сверхоперативной памяти. Информационный вход-выход 10 этих элементов подключен к второму информационному входу-выходу первого блока 3 обмена информацией, а выходы 11 и 12 ускоренного переноса соединены с входами схемы 9 ускоренного переноса и с информационным входом ;второго блока 4 обмена информацией. Синхровходы микропроцессорных элементов 8 соединены с выходом элемента И 6, вход переноса младшей секции арифметико-логического блока ;соединен с выходом 13 поля переноса Яблока 1 микропрограммного управление |а входы переноса всех последующих секций микропроцессорного арифметико-логического блока соединены соответственно с выходами схемы 9 ускоренного переноса. Другие входы микропроцессорных элементов 8 соединены соответственно с выходами 14 поля определения кода операции и выходами 15 констант блока 1 ьшкропрограммного управления. Схема ускоренного переноса соединена по входу с выходом 13 поля переноса блока 1 микропрограммного управления и с выходами 11 и 12 ускоренного переноса всех секционированных микропроцессорных элементов 8. Выходы схемы ускоренного переноса соединены соответственно 322 с входами переноса секционированных микропроцессорных элементов 8, начиная со второй секции, и с входом J6 блока 1 микропрограммного управления. Операционное устройство микропроцессорной вычислительной системы работает следующим образом. Работа устройства синхронизируется сигналом, поступающим через синхро™ вход 17. Задним фронтом синхросигнала в блоке 1 микропрограммного управления формируется адрес слова микрокоманды, подпежащей выполнению. По данному адресу считывается микрокоманда, и при помощи управляющих полей слова микрокоманды осуществляется управление работой устройства в течение данного мащинного щага. Арифметико-логическому блоку 2 задается из полей текущей микрокоманды код операции по шине 14, константа или маска по шине 15 и входной перенос по шине 13, если это требуется текущей операцией. Управляющее поле той же микрокоманды дешифруется дешифратором 5, который формирует на . своих инверсных выходах сигнйлы уп|равлени9 блоками 3 и 4 обмена информацией и настраивает- их на прием-передачу. Оба блока обмена информацией постоянно подключены к входувыходу 7 устройства. Так как одновре менно может быть активным только один из выходов дешифратора 5, то, если блок 4 обмена информацией настроен на передачу информации на выход 7 устройства, блок 3 обмена информацией настроен на прием, или наоборот. Тогда в данном операционном устройстве происходит только передача на выход устройства информации с выхода арифметико-логического блока 2, так как блок 4 обмена информацией в качестве приемника не используется. Для арифметико-логического блока 2 внешними операндами являются данные на входной-выходной шине 10, шине 15 констант и шине 13 входного переноса, а внутренними операндами - содержимое внутренней памяти, т.е. содержимое накапливающего регистра или регистров сверхоперативной памяти микропроцессорных элементов 8. Арифметико-логический блок 2 формирует результат операции по значениям операндов в соответствии с кодом операции на шине 14 и с приходом синхросигнала запоминает его во внутренней памяти арифметико-логического блока. Для ускорения формирования сигнала полного переноса в арифметико-логическом блоке 2 используется схема 9 ускоренного переноса, принимающая по шинам 1I и 12 вырабатьшаемые микропроцессорными элементами 8 сигналы ускоренного переноса. Сигнал полного переноса на шине 16 запоминается с приходом синхросигнала в блоке 1 микро программного управления. Результат операции может передаваться на выход 7 устройства из накапливающего регистра микропроцессорных элементов 8 через шину 10 и блок 3 обмена информацией. Микропроцессорные элементы 8 выполняют определенный набор операций результаты которых запоминаются в накапливающем регистре или в какомлибо другом регистре сверхоперативной памяти. Вывод результата на выход 7 устройства из любого регистра сверхоперативной памяти требует пересыпки результата в накапливающий регистр микропроцессорных элементов 8 с предварительным запоминанием содержимого накапливающего регистра в свободном регистре сверхоперативной памяти и последующего его восстановления , если данные из накапливающего регистра должны использоваться в последующих шагах микропрограмм 1. Вывод содержимого любого регистра сверхоперативной памяти на выход 7 устройства через блок обмена информацией требует выполнения трех шагов, микропрограммы. Дпя сокращения количества выполняемых шагов введен второй блок 4 обмена информацией и элемент И 6, с помощью которых осуществляется вывод содержимого регистра сверхопера тивной памятн на выход 7 устройства за один машинный шаг без разрушения содержимого накапливающего регистра При вьшолнении арифметических операций над операндами, одним из которых яувляется содержимое регистра внутренней памяти микропроцессорного эле мента 8, а вторым - содержимое шины 15 констант, двухразрядный микропроцессорньй элемент 8 вырабатывает сигналы ускоренного переноса на шинах 11 (сигнал X) и 12 (сигнал Y) 324 ,K, ,; ,R R,K, +К,К„ ,-b ,(2) где R - двоичное значение (О или 1) содержимого младшего разряда внутреннего регистра; R - двоичное значение (О или I) содержимого старшего разряда внутреннего регистра; Кр - двоичное значение (О или 1) содержимого младшего разряда шины 15; К - двоичное значение (О или I) содержимого старшего разряда шины 15. Приняв постоянные значения (И и подставив их в выражения (1) и (2), получим X RO;(3) Y R,(4) Выражения (3))(4| можно расширить для 2д-разрядного арифметикологического блока, построенного на базе микропроцессорных элементов 8; Х„ - RO(5) (6) где ,2,3...п. Следовательно, на выходах совокупности шин И, 12 для п микропроцессорных элементов 8 формируется со держимое внутреннего регистра следующего формата: R R R в R ч в 4 О Цикл вывода содержимого регистра сверхоперативной памяти на выход 7 устройства осуществляется мшсрокоман дои, которая формирует на шине 14 код операции, использующий в качестве первого операнда выбранный регистр сверхоперативной памяти, а в качестве второго операнда - содержимое шины i5 в виде константы 01...0101. При этом на вход дешифратора 5 из управляющего поля микрокоманды подается код, в соответствии с которым дешифратор вырабатывает на втором инверсном выходе сигнал запрета работы элемента И 6 н одновременно настраивает работу второго блока 4 обмена информацией на передачу содержимого выбранного внутреннего регистра сверхоперативной памяти на выход 7 устройства. Синхросигнал на входе арифметико- v логического блока в данном машинном шаге отсутствует из-за запрета работы элемента И 6, и содержимое

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор микро-ЭВМ | 1979 |

|

SU1042026A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Микропрограммное вычислительное устройство | 1984 |

|

SU1229761A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

ОПЕРАЦИОННОЕ УСТРОЙСТВО МИКРОПРОГСЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее первый блок обмена информацией, первый информационный вход-выход которого подключен к входу-выходу устройства, а второй информационный вход-выход и управляющий вход - соответственно, к информационному входу-выходу арифметикологического блока и первому инверсному выходу дешифратора, вход которого соединен с выходом управлякяцего Д1.;и i . V1 поля блока микропрограммного управления, синхровход и вход переноса которого соединены соответственно с синхровходом устройства и выходом переноса арифметико-логического блока, входы констант, кода операции и переноса которого подключены соответственно к выходам блока микропрограммного управления, отличающееся тем, что, с целью повышения производительности, оно содержит элемент И и второй блок обмена информацией, причем первый и второй входы и выход элемента И § подключены соответственно к синхровходу устройства, второму инверсному выходу дешифратора и синхровходу арифметико-логического блока, управляющий вход, информационные вход и выход второго блока обмена информацией подключены соответственно к второму инверснсжу выходу дешифратора, выходу ускоренного .переноса арифСО метико-логического блока и выхо00 ду устройства. ел со 1C

| Микропроцессорная вычислительная система | 1975 |

|

SU674025A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Intel | |||

| Series | |||

| Приспособление к трепальному колесу или барабану для трепания льна или пеньки | 1925 |

|

SU3000A1 |

| Corporation, California, 1977. | |||

Авторы

Даты

1985-12-15—Публикация

1982-01-04—Подача