Изобретение относится к вычислительной технике и может найти применение в контроллерах микропроцессорных системах, блоках арбитров, коммутаторах магистралей, интерфейсных блоках микропроцессоров и т.п.

Известны устройства для обмена информацией микропроцессорной вычислительной системы, .содержащее три блока обмена информацией, многоканальные входы и выходы которых соединены с двунаправленной шиной, регистр состояний, регистр направления передачи данных, управляющий регистр, блок управления и регистры хранения информации, входы-выходы регистров подключены через двунаправленные информационные шины к блокам обмена информацией, вход запуска блока управления подключен к внешней информационной шине 1.

Недостатки этих устройств состоят в их малой пропускной способности.

Наиболее близким к данному по сущности технического решения является устройство управления обменом информации, содержащее блоки связи с абонентами, соединенные первыми входами-выходами коммутатора, блок выделения paspemeHiib ;-: обращений регистры адресов, блок приоритета и блок управления и обеспечивающее управление обменом данных между двумя произвольными абонентами 2.

Недостаток указанного устройства заключается в его малой пропускной способности.

Цель изобретения - повышение пропускной способности.

10

Поставленная цель достигается тем, что устройство для обмена информацией, содержащее; три блока связи с каналом, первые входы-выходы которых являются соответствующими

15 информационными входами-выходами устройства, а вторые входы-выходы подк.пючены к соответствующим информационным входам-выходам ког 1утатора, и блок управления, введены блок

20 регистров, счетчик, операционный блок и блок задания условных операций, причем вторые входы-выходы первого и второго блоков связи с каналом .оединены соответственно с пер25выми и вторыми .информационными входами-выходами блока регистров, счетчика операционного блока и блока задания условных операций, первый вход управления которого соединен

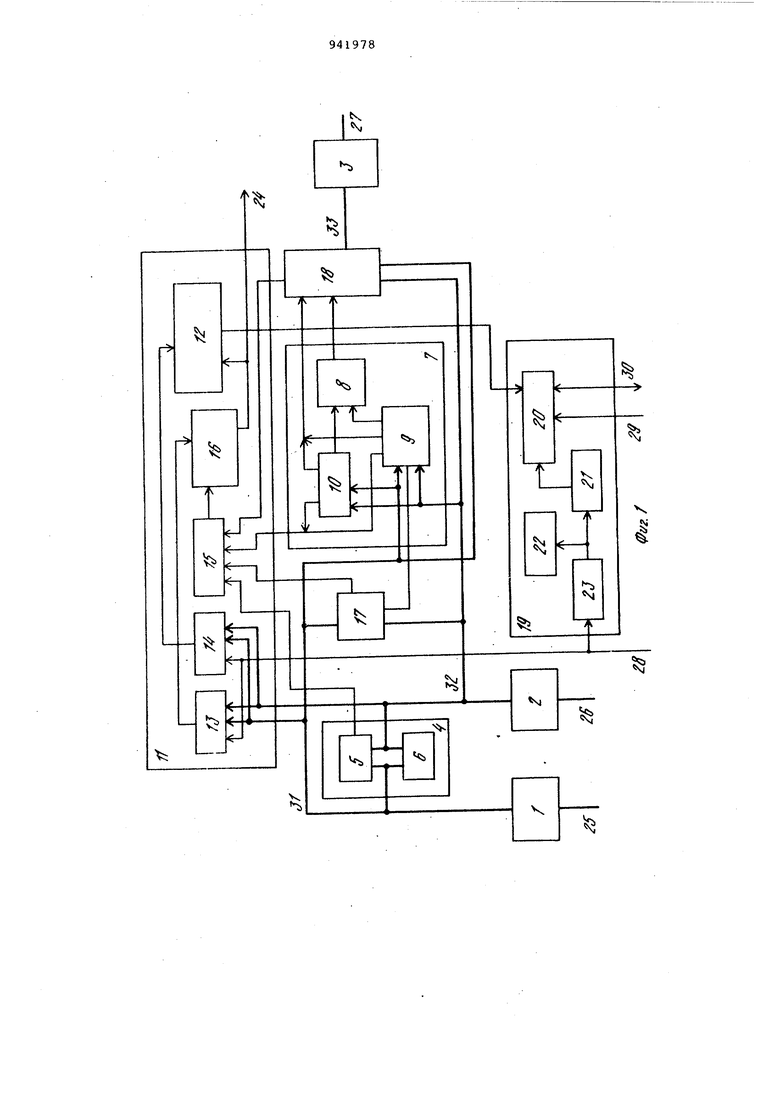

30 с входом микрокоманд устройства и входом команды блока управления,вход запуска и вход-выход синхронизации которого являются соответственно входом запуска и входом-выходом синх ронизации устройства, выходы состоя ния блока регистров операционного блока и коммутатора и выход перенос счетчика соединены соответственно с вторым, третьим, четвертым и пятым входами управления блока условных переходов, вход-выход и выход у ;равления которого подключены соответственно к входу-выходу управления устройства и входу управления блока управления, выход состояния счетчика соединен с входом управления операционного блока, первый и второй выходы управления которого подключены к соответствующим входам управления коммутатора. Кроме того, операционный блок со держит узел приоритета, схему сравнения и узел маскирования, причем первые и вторые узла маскирова ния и схемы сравнения подключены соответственно к первому и второму информационным входом-выходом устрбйства, первые выходы - к выходу состояния блока, вторые выходы - к первому выходу управления блока. третьи выходы - к соответствующим входам узла приоритета, выход которого является вторым выходом управления блока, третий информационный вход схемы сравнения является входом управления блока. Причем блок условных операций содержит регистр маски состояния, регистр полярности кода условий,узел маскирования состояний, регистр состояния и узел формирования «(-эда усло вий, причем первые, вторые и третьи. входы регистра маски состояния и регистра полярности кода условий соединены соответственно-с первым и вторым информационными входами-выходами блока и первым входом управлени блока, выход регистра маски состояни соединен с первым входом узла маскирования состояния, выход которого соединен с входом-выходом управления блока, а второй вход - с выходом регнстра состояния, входам которого являются соответственно втopы ;, третьи четвертым и пятым входами управления блока, выход регистра полярности кода условий подключен к первому входу узла формирования кода условий, вторым входом соединенного с входом-выходом управления блока, а выходсм с выходом управления блока. При этом блок управления содержи регистр микрокоманд, дешифратор мик роопераций, регистр режима и узел формирования внутреннего рабочего цикла, причем вход регистра микроко манд является входом команды блока, а выход - соединен со входами дешифратора микроопераций и регистра режима, выходом соединенный с первым входом узла формирований внутреннего рабочего цикла, второй и третий входы и вход-выход которого являются соответственно входом запуска, входом управления и входом-выходом блока. На фиг.1 представлена блок-схема устройства; на фиг.2 - пример объединения устройств при построении развитой системы обмена. Устройство (фиг.1) содержит блоки 1, 2 и 3 связи с каналом, блок 4 регистров, включающий регистр 5 сдвига и регистры б общего назначения операционный блок 7, включающий узел 8 приоритета, схему 9 сравнения и узел 10 маскирования, блок 11 задания условных операций, состоящий из узла 12 формирования кода условий, регистра 13 маски состояния, регистра 14 полярности кода условий, ре- гистра 15 состояния и узла 16 маскирования состояний, счетчик 17, коммутатор 18, блок 19 управления,включающий узел 20 формирования внутреннего рабочего цикла, регистр 21 режима, дешифратор 22 микроопераций и регистр 23 микрокоманд, управляющий вход-выход 24 устройства, информационные входы-выходы 25, 26 и 27устройства/ вход 28 микрокоманд устройства, вход 29 запуска, входвыход 30 синхронизации устройства и информационные шины 31, 32 и 33 устройства. , Устройство обмена информации микропроцессорной системы может быть выполнено в виде одной большой интегральной схемы на К-МДП технологии и помещено в 42тх выводной корпус. Считается, что внешние выводы устройства 25,26 и 27 - восьмиразрядные, микрокоманда, поступающая на вход. 28- пятиразрядная. Несмотря на малую разрядность микрокоманды, система микрокоманд может йлть достаточн9,. широка, что объясняется наличием регистра 21, в состав которого, например, входят: триггер группы микрокоманд, триггер сдв 1говых операций, триггер асинхронной иадачи информации, триггер повторения микрокоманды, триггер условных операций и триггер загрузки служебных регистров (регистра 13, регистра 14 и регистра 21) из микрокоманды. При выполнении различных микрокоманд, устройство работа.ет следующим образом. В начале работы устройства обмена информацией микропроцессорной системы на вход 28 в регистр 23 подается управляющая информация, соответствующая загрузке регистра 21 регистра 13 и регистра 14 информацией

из микрокоманды либо из одного из внешних каналов 1,2 и 3. Управляющая информация (микрокоманда) сопровождается сигналом запуска, поступающим на вход 29 в узел 20. Информация запоминается в регистре 23 и дешифруется в дешифраторе 22. Если код микрокоманды соответствует загрузке служебных регистров из одного из внешних каналов через блоки 1, 2 и 3 осуществляется прием информации из канала и запись в служебные регистры. Если код микрокоманды соответствует загрузке служебных регистров из микрокоманды, то устанавливается в 1 триггер загрузк служебных регистров, входящий в состав регистра 21. Следующая микрокоманда, которая также сопровождается сигналом запуска в зависимости от кода поступает либо в регистр 14 регистр 13, либо в регистр 21. Загрузка этих регистров задает режимл работы устройства обмена информацие микропроцессорной системы.

Следует отметить, что после выполнения каждой микрокоманды на входе-выходе 30 из блока 20 появляется сигнал, свидетельствующий об исполнении микрокоманды, причем до появления этого сигнала/ даже при наличии сигнала запуска, поступающего на вход 29, новая микрокоманда, поступающая через вход 28 блоком 19 не воспринимается..

В зависимости от кода микроког в.нды возможно выполнение различных операций обмена информации.

Пусть, например, необходимо осуществить операцию массива информации размерности К слов из одного внешнего канала в другой внешний канал (из входа-выхода 27 на .вход-выход 25). Операция осуществляется следующим образом.

Сначала осуществляется загрузка в счетчик размерности массива. Информация о размерности массива поступает через блок 3 на информационную шину 33, затем происходит коммутация информации через коммутатор 18 на информационную шину 31, по которой она поступает на информационные входы счетчика 17 и запоминаетс Информация о размерности массива вводится в счетчик обратным кодом так, что если к этому коду добавить К все разряды счетчика окажутся в единичном состоянии. Затем выполняется загрузка регистра 21, регистров 13 и 14 кодом, соответствующим режиму первой группы повторяющихся микрокоманд, размаскированному сиг налу с выхода переноса счетчика 17 и положительной полярности условия После этого подается микрокоманда коммутации информации из входа-выхода 33 на вход-выход 31, по которой Н11 юрмация из блока 3 поступает в блок 1, Параллельно с этим происходит выполнение операции +1 в счетчике 17, который формирует сигнал переноса, поступающий в блок 11.

Так как в регистре 13 содержится код, соответствующий размаскированию сигнала переноса счетчика 17, то на управляющем входе-выходе 24 это состояние соответствует переполнению (не переполнению) счетчика. В случае не переполнения счетчика нулевой сигнал от старшего разряда счетчика через узел 12 поступает на вход узла 20. Так как при этом

код регистра 14 соответствует положительной полярности условия, то сигнал на входе управления блока 19 соответствует невыполнению условия. Это приводит к многократному повторению микрокоманды до тех пор, пока сигнал на этом входе не станет соответствовать выполнению условия, т.е. до тех пор, пока не осуществляется передача массива информации.

После этого.в узле 20 формируется . сигнал, выдаваемый на выход 30 и свидетельствующий об окончании выполнения микрокоманды. Во время выполнения микрокоманды индикация перехода от 1 микроцикла к другому

осуществляется импульс-ами на входевыходе 30 .

Рассмотрим пример выполнения операций обмена с арбитражем.

Причем для определенности описания информация (запросы на арбитраж) поступают по входу-выходу, загрузка маски происходит из входа-выхода 26, а выдача результата операции (разрешение) производится на вход0 выход 27.

Сначала осуществляется загрузка маски запросов на арбитраж.. По входу 28 вместе с сигналом запуска (вход 29) подается код соответствующей. 5 микрокоманды). Информация поступает через блок 2 на информационную шину 32, заносится в регистры блока 4. В узле 20 на входе-выходе 30 возникает сигнал синхронизации, свидетельствующий об окончании выполнения микрокоманды.

После этого производится заг эузка регистров 21, регистра 13 и 14 кодом, который соответствует второй группе повторяющихся условных микрокоманд, размаскированному сигналу , на выходе .состояния блока 7 и отрицательной полярности кода условия.

Затем подается микрокоманда передачи информации из входа-выхода 25 с маскированием и арбитражем в вход-выход 27, при этом осуществляется прием информации в блок 1, которая по шине 31 поступает в узел 10, на второйвход которого, поступает по информационной шине 32 маска С выхода узла 10 информация поступает на вход узла 8, где осуществляется выделение старшего по приоритету незамаскированного единичного сигнала. С выхода узла В индикация поступает на первый управляющий вход коммутатора 18, с выхода которого по информационной шине 33 она пере.дается в блок 3. Параллельно с этим ригнал с выхода состояния блока 7

(сигнал сравнения с ) поступает в блок 11. Так как в регистре 13 содержится код, соответствующий размаскированию сигнала состояния блока 7, то на шинах входа-выхода 24 эт .состояниесоответствует отсутствию (наличию) незамаскированных запросов Причем, в случае отсутствия незамаскированных за.просов (сравнение с О ) на соответствующей шине управляющего входа-выхода 24 - высокий уровень. Этот сигнал через узел 12 поступает на вход управления блока 19. Так как код регистра 14 соответствует отрицательной полярности кода условия, а на управляющем входе-выходе 24 - высокий уровень, то сигнал на входе управления блока 19 соответствует невыполнению условия. Поскольку микрокоманда условная,это приводит к запрету вьвдаЧ|И информации в блок 3, а так как микрокоманда повторяющаяся - невыполнение условия приводит к ее повторению до тех пор, пока сигнал на управляющем входе бло ка 19 не станет соответствовать выполнени условия. При этом произойдет выдача результата операции в блок 3 и в узле 20 сформируется на одной из шин входа-выхода 30 сигнал окончания выполнения микрокоманды. Во время выполнения микрокоманды индикация перехода от одного микроцикла к другому осуществляется импульсами на шинах входа-выхода 30 узла 20.

При выполнении операции преобразования из последовательного кода в параллельный (информация в последовательном коде подается из входавыхода 25) сначала производится загрузка регистра 21, в частности,уста1

триггера сдвиговых

новка в

операций, а после этого осуществляется преобразование информации из последовательного кода в параллельный. При этом информация в последовательном коде поступает через блок 1 на младший разряд информационной шины 31 и заносится в младший разря регистра 5. Сдвиги в регистре 5 повторяются до заполнения информацией регистра, после чего на одной из шин входа-выхода 30 появляется сигнал окончания выполнения микрокоманды. Во время выполнения микрокоманды информация перехода от од- . ного микроцикла к другому осуществляется импульсами на входе-выходе 30.

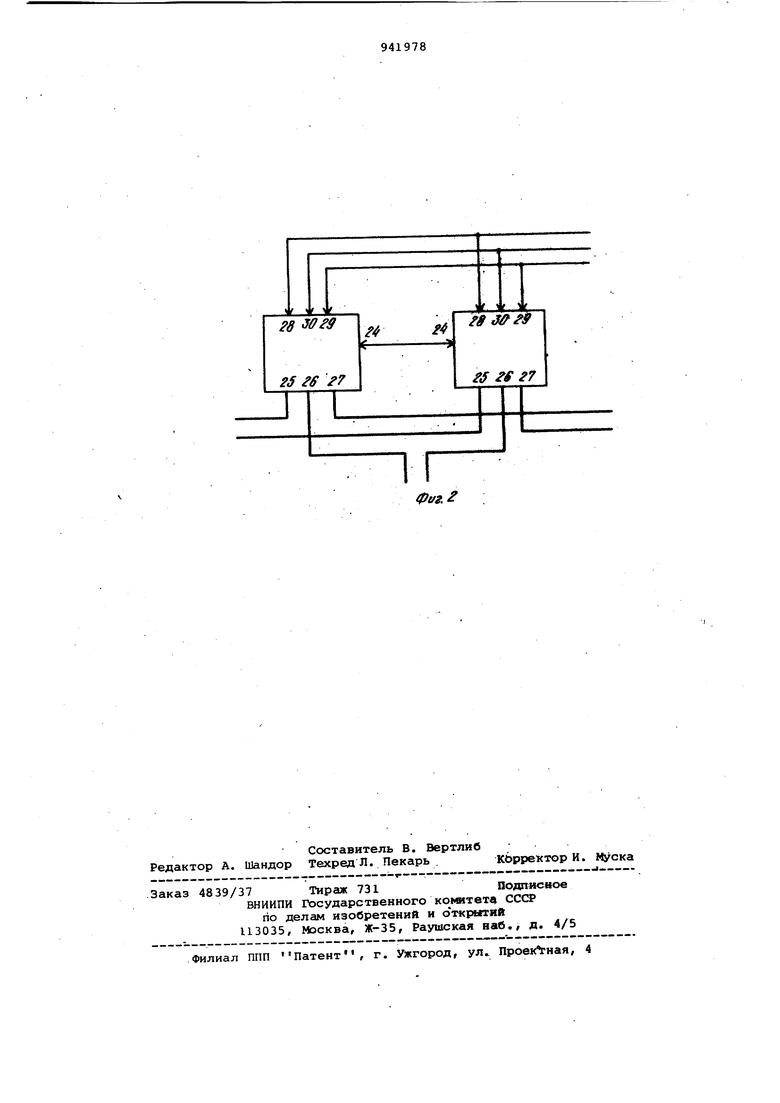

Устройство обмена информации микропроцессорной системы может также выполнять двухтактные как одиночные, так и повторяющиеся микрокоманды - это микрокоманды преобразования форматов байт-слово (8 разрядов 16 разрядов) и слово-байт, а также микрокоманды чтения и записи, микрокоманды ассоциативного доступа и др. Возможно наращивание разрядности информации при выполнении операций обмена путем объединения нескольких устройств в группу (фиг.2). Взаимная синхронизация устройств осуществляется объединением входов 29 и входов-выходов 30, а однотипная реакцияна условия - объединением входоввыходов 24.

Таким образом, возможность обработки и анализа информации, вместе с возможностью наращивания разрядности и оперативной реакции устройства на различные состояния, возникающие в процессе обмена позволяют повысить быстродействие устройства и расширить область его применения.

Формула изобретения

1. Устройство для обмена информацией, содержащее три блока связи с :каналом, первые входы-выходы которых являются соответствующими информационными входами-выходами устройства, а вторые входы-.выходы подключены к соответствующим информационным входам-выходам коммутатора, и блок управления, отличающееся тем, что, с целью повышения быстродействия, в него введены блок регистров, счетчик, операционный блок и блок задания условных операций, причем вторые входы-выходы первого и второго блоков связи с каналом соединены соответственно с первым и вторыми информационными входами-выходами блока регистров, счетчика, операционного блока и блока задания условных операций, первый вход управления которого соединен с входом микрокоманд устройства и входом ко манды блока управления, вход запуска и вход-выход- синхронизации которого являются соответственно входом запуска и входом-выходом синхронизации устройства, выходы состояния блока регистров операционного блока и коммутатора и йыход переноса счетчика соединены соответственно с вторым, третьим, четвертым и пятым входами управления блока условных переходов, вход-выход и выход управления которого подключены соответственно к входу-выходу управления устройства и входу управления блока управленияJ выход состояния счетчика соединен с входом управления операционного блока, первый и второй выходы управления которого подключены к соответствующим входам управления коммутатора.

2.Устройство по п. 1/ отличающееся тем, что операционный блок содержит узел приоритета, схему сравнения и узел маскирования, причем первые и вторые входы узла маскирования и схемы сравнения подключены соответственно к первому и второму информационным входам-выходам устройства, первые выходы - к выходу состояния блока, вторые выходы, --к первому выходууправления блока, третьи . выходы - к соответствующим входам узла приоритета,выход которого является вторым выходом управления блока, третий информационный вход схемы сравнения является входом управления блока.

3.Устройство - по п. 1, о т л ичающееся тем, что блок задания условных операций содержит ре.гистр маски состояния, регистра полярности кода условий, узел.маскирования состояний, регистр состояния и узел формирования кода условий, причем первые, вторые и третьи входы регистра маски состояния и регистра полярности кода условий соединены соответственно с первым и вторым информационными входами-выходами блока и первым входом- управления блока.

выход регистра маски состояния соединен с первым, входом узла маскиро1вания состояния, выход которого соединен с входом-выходом управления блока, а второй вход - с выходом

регистра состояния, входы которого

являются соответственно вторым,третьим, четвертым и пятым входами управления блока, выход регистра полярности кода условий подключен к первому

входу узла формирования кода условий,

вторым входом соединенного с входомвыходом управления блока, а выходом - с выходом управления блока. 4. Устройство по п. 1, о т л ичающееся тем, что блок управления содержит регистр микрокоманд, дешифратор микроопераций, регистр режима и узел формирования внутреннего рабочего цикла, причем вход регистра

микрокоманд является входом команды блока, а выход соединен с входами дешифратора микроопераций и регистра режима, выходом соединенного с первым входом узла формирования внутреннего

рабочего цикла, второй и третий

входы и вход-выход которого являются соответственно входом запуска,входом управления и входом-выходом блока.

Источники информации,

принятые во внимание при экспертизе

1.Патент СЗНА 4020472, кл. 340-172.5, 1976.

2.Авторскоесвидетельство СССР 444062,. кл. G 06 F 9/00, 1972

(прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорная вычислительная система | 1975 |

|

SU674025A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Процессор | 1985 |

|

SU1280378A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство управления обменом | 1977 |

|

SU732842A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

Авторы

Даты

1982-07-07—Публикация

1978-07-14—Подача