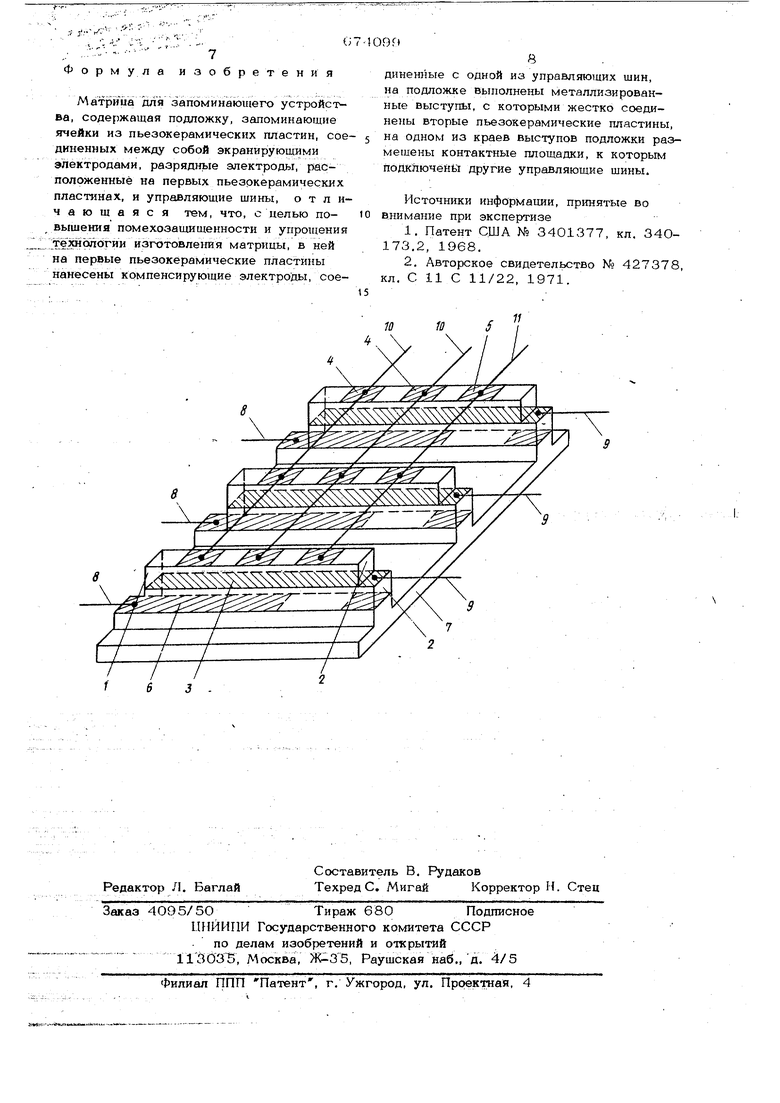

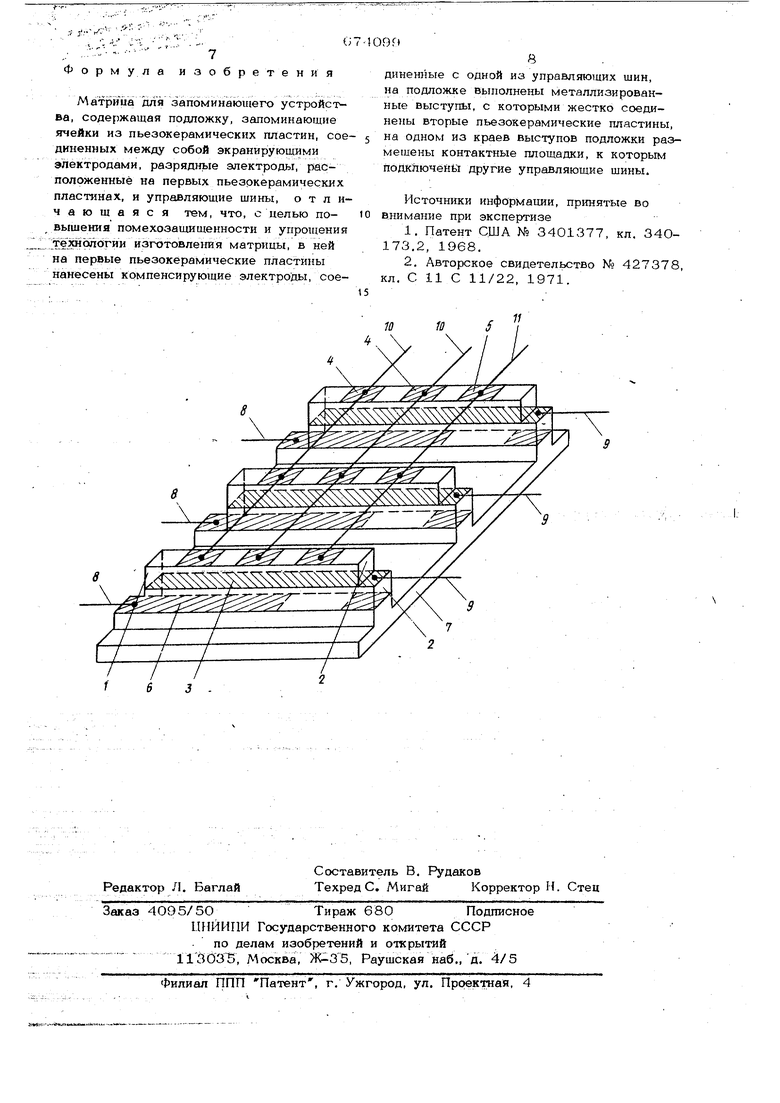

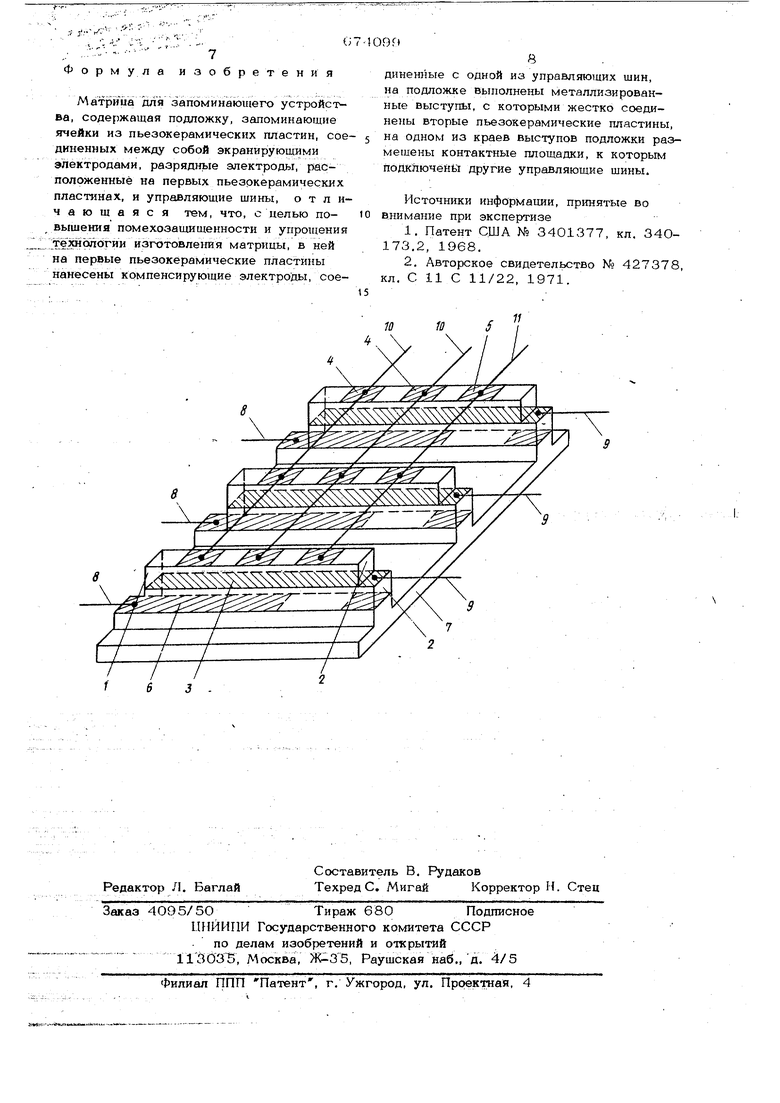

(54) МАТРИЦАДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА чины информационных сигналов с одно врёмвнным снижением уровня сйгнал6в помех, а также упрощение технологии изготовления матрицы. Цель достигается тем, что в матрице на первые пьезокерамические пластины нанесены компенсирующие электроды, соединенные с одной из управляющих шин, на подложке выполнены металлизированные выступы, с которыми жестко соединены вторые пьезокерамические пластины, на одном из краев выступов подложки размещены контактные площадаи, к которым подключены другие управляющие шины. На чертеже изображена матрица, содержащая, например, три двухразрядные запо минающие йчейки. Описываемая матрица содержит запоминающие ячейки 1, количество и разрядность которых определяется объёмом памяти. Ячейки 1 представляют собой многослойную, акустически монолитную конструкцию, в котО1Чю объединейы пьезокерамические пластины 2 по экранирующему электроду 3. На первых пластинах 2 (верх ние на черт.) расположены разрядные электроды 4, где в одной плоскости с ра рядаыми электродами на одном из концов ячеек 1 расположены компенсирующие электроды S. На вторых пластинах 2 (ни ние на черт.) расположен общий электрод 6 такой конфигурации, что под компенсирующим электродом 5 общий электрод отсутствует. Ячейки 1 расположены на Металлизированных выступах подложки 7, а общим электродом 6 электрически и механически жестко соединены с поверхностью выступов. Выступы и ячейки имеют равную ширину. С одного края ячеек, йротивоположного краю, где расположены электроды 5, выступы подложки выходят из-под ячеек 1, а нанесенная на них металлизация соединена с общими электродами 6 и являются контактными площадками общих электродов. С другогокрай ячеек BTopbie пластины 2 (пластины между электродами 3 и 6) выступают из-под первых пластщ на которые йанесёны электроды 4, а расположёйные на выступах вторьис пластин участки электродов ШёШйёйЫ с экранйр|ующими электродами 3 и являются кбнтакТяыми площадками. К контактным площадкам общи электродов и экранирующих электродов подсоединены управляющие шийы, которые являются, соответстЬенно, разрядными 8 и общими разрядными 9 шинами матрицы. Одпоименные разрядные электроды ячеек 1 электрически объединены в управляющие числовые шины 1О матрицы, а электроды 5 электрически объединены в управляющую шину 11, Пъезокерамические пластины 2, расположенные между экранирующими 3 и общими 6 электродами поляризованы в одном направлении до насыщения, причем поляризация им задается при изготовлении матрицы. Поляризованньхми до насыщения являются и участки пьезокерамических пластин 2, расположенные между экранирующими электродами 3 и электродами 5, и поляризация им задается также при изготовлении. Следует отметить, что для птастин между электродами 3 и 6 и участкоб пластин между электродами 3 и 5 достаточно, чтобы они обладапи пьезосвойствами (деформация пластины при приложений электрического поля и возникновение электрического поля при деформации пластины) и для них не является обязательным наличие сегнетосвойств (изменение спонтанной поляризации при приложении электрического поля). Сегнетосвойствами должны обладать участки пластин между электродами 3 и 4. Каждому из этих участков при записи, в зависимости от записьшаемой информации (1 или О), задается одно или другое значение спонтанной поляризации. При изготовлении гатриц могут быть использованы различные пьезоэлектрические материалы. Для этой цели хорошими электрическими свойствами характеризуется пьезокерамика типа ЦТС-19, на основе которой были изготовлены экспериментальные образцы. Закись информации в предложенной матрице осуществляется путем приложения разности напряжения к участкам пластины Кежду электродами 4 и 3, преё)1шающей напряжение перёполяризации пластины, одной или другоЙЕ полярности, в зависимости от записьшаемой информации 1 или О . Прд действием напряжения участки пластаны поляризуются до насыщений. Приложение соответствующих разностей напряжения к выбранным участкам пластин (запоминающим элементам матрицы) выполняется подачей необходимых напряжений на числовые 10 и общие разрядные 9 шины. При считывании информации матрица допускает два включения по отношенньа к подаче сигналов опроса и сигнала снятая янформационньис сигналов. В первом включении сигнал опроса (импульс напряжения возбуждения) прикладывается к одной из выбранных шин 10,длительность и амплитуда которого являются значительно меньшими длительности и амплитуды импульса напряжения необходимого для переполяризации участ ков пластин между электродами 4 и 3. Одновременно с этим к шине 11 прикладывается импульс напряжения противоположной полярнос-ш и равный по амплитуде и длительности импульсу, прикладываемому к выбранной шине 10. Прикладываемые импульсы напр5шения вызывают импульсную деформаш1ю участков первых пластин между электродами 4 и 3, а так же 3 и 3 и одновременно с этим импуль сную деформацию участков вторых пластин, расположенных против электродов 4 и 5. В результате на шинах 8 появляются импульсы напряжения, полярность которых определяется направлением деф(ч мации, а соответственно и направлеШем поляризации (записанис ивформащей) участков пластин меж;} выбршгными разрядными 4 и экрани иицими 3 электродами. Электроды 6 не перекрывают участ ков нижних пластин, расположенных против электродов 5, поэтому статическая деформация, передаваемая вто1ялм пластинам от учас-гаов первых пластин 2 меж ду электродами 5 и 3, не приводит к появлению дополнительньис сигналов на шинах 8, которыэ могли бы накладываться на импульсы напряжения (информационные сигналы), обусловленные деформацией участков пластин под ектродами 4 В процессе приложения электрическое го напряжения к шинам lO и 11 и его снятии протекают токи заряда, а затем токи разряда входных емкостей. Причем теиси заряда и разряда про гекйют и после приложения и снятая напряжения, так как на электродах появляются электрические зарйды, обусловленные деформацией (изменением поляризации) участков, которая iio отношению к прикладьшаемому электрическому напряжению происходит с запаздыванием, определяемым rec MeTpj4ec кими размерами участков. Участки пластин 2 под электродами 4 и 5 являются эквивалентньхми по электрическим и эпек ромеханическим параметрам. В связи с этим токи, протекающие по шинам Юн 11,являются равными по величине и вза имно противоположными по направлению и знаку и, наводимые ими электромагнит ные сишалы помех на шинах 8, являютс взаимно противоположными и компенсируются. При эгам взаимноскомпенсированы и эЛектроятатиЧеские сигналы помех. В предложенной матрице, при первом включении, считьюание информации можно производить без обязательного, как для од)угих типов матриц, подключения шин 9 к обшей точке, так как замкнутая цепь для протекания заряда и разряда входных емкостей запоминающих элементов образована одаой из выбранных шин 10 и шиной 11. Во втором включении импульс напряжения возбуждения прикладьшается к одной из выбрш1ных шин 8, информационные сигналы снимают с шин 10, а шина 11 используется щ качестве общей для определения по отаошени1р к ней информациошшх сигнале на шинах 1О и уменьшения сигналов помех передаваемых от шин 8 на шины 1О, а соответственно и на шину 11. Пегфое включение матрицы более приемлемо, так Еак оно позволяет использовать ряд ее важных преимуществ, а именно более высокое бьютродействие и более высокие уровни и лучшую форму информационных «сигаалов на шинах 8 пря приложении импульса возбуждения к шинам 10, чем при п}жложенпи импульса возбуждения к шинам 8 и ПС сравнению с известными мат жцами, В матрице при первом включении быстродействие запоминающих элементов не зависит от ее бщих геометрических размеров, и определяется геометрическими размерами электрО{к в 4 и технологическим моЖет быть обеспечено десятжи и даже единицы наносекунд. Наряду с этим параметры информашонных сигналов не зависят от места раэмещейия запоминающих элементов, а определяются в основном геометричесKBivfH размерами электродов 4, Это позволяет технологически просто обеспечить хорошую одно-гапность элементов в матрице и повьюить ее надежность. Кроме того, выступы подложки и сама подложка, fi особенности в конструкции матрицы, когда толщина вторых пластин превышает толщину первых пластин, практически не оказывают влияния на величину передаваемой деформации от участков верхних Щ1:ш:тин к нижним и не приводят к уменышению информационных сигналов и, вместе с тем, обеспечиаают хорошее поглощенве энергии и демпфирование резонансных колебаний участков. Формула изобретен и Матрица для запоминающего устройства, содержащая подложку, запоминающие ячейки из пьезокерамических пластин, сое диненных между собой экранирующими электродами, разрядньге электроды, расположенные на первых пьезокерамических пластинах, и управляющие шины, отличающаяся тем, что, с целью по, вышения помехозащищенности и упрощения 1Т§.нологии изготовлешя матрицы, в ней на первые пьезокерамические пластины нанесены компенсирующие электроды, соел / Х| 7А /-7-/ / / / / диненные с одной из управляющих шин, на подложке выполнены металлизированные выступы, с которыми жестко соединены вторые пьезокерамические пластины, на одном из краев выступов подложки размешены контактные площадки, к которым подкпюченй другие управляющие шины. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3401377, кл 34О173.2, 1968. 2.Авторское свидетельство № 427378 л. С 11 С 11/22, 1971. :

| название | год | авторы | номер документа |

|---|---|---|---|

| МАТРИЦА ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1971 |

|

SU427378A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОЦП•'t-li | 1971 |

|

SU419982A1 |

| АССОЦИАТИВНЫЙ НАКОПИТЕЛЬ | 1973 |

|

SU374662A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| ВСЕСОЮЗНАЯ ' | 1973 |

|

SU368645A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU934554A1 |

| Запоминающее устройство | 1973 |

|

SU447757A1 |

Авторы

Даты

1979-07-15—Публикация

1975-10-07—Подача