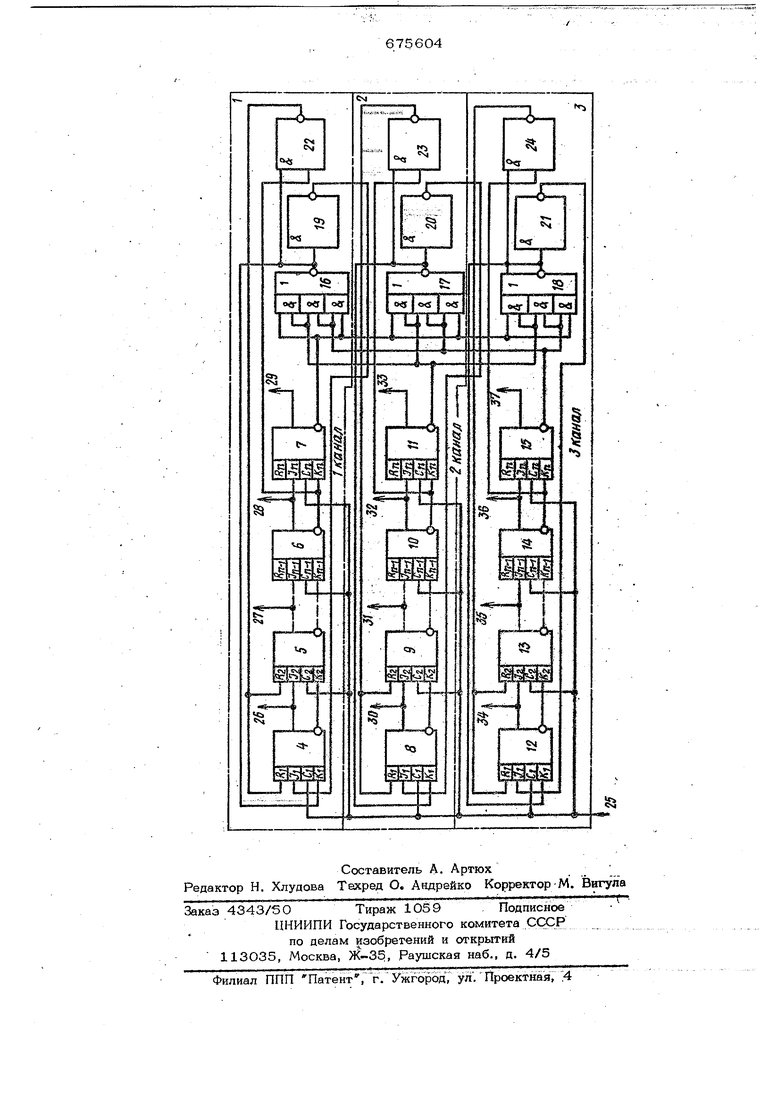

(54) РЕЖРВИРОВАННЫЙ КОЛЬЦЕВОЙ ДЕЛИТЕЛЬ ЧАСТОТЫ К-входом первого 5И -триггера данного канала, в каждый канал делителя введён дополнительный логический элемент НЕ, один вход Которого соединен с инверс ным выходом предпоследнегхл. JK-триг. гера данного канала, второй вход - с выходом логического элемента ЗИ-ЛЛИ-НЕ, а выход подключен -входам первых двух риг герое данного канала, причем выход логического эле-мента НЕ соединен с jf -«ходом первого 3 К-триггера данного канала. На чертеже приведена структурная электрическая схема делителя частоты. Делитель частоты состоит из трех каналов 1-3, каждый из которых содержит J К-триггеры 4-15, логические отег MisHTH ЗИ-ИЛИ-НЕ 16-18 и яоТйШские элементы НЕ 19-24, Входной сигнал . подан.на входную шину 25. Выходнью . сигналы снимаются с выходов 26-37. Принцип работы счетчика заключает. он в следующем. . При поступлении импульсов на входную шину 25 происходит последоёательное переключение ЗК-триггеров 4-7, 8-11, 12-15 каждого канала делителя частоты При просчёте соотватствутощего количества входных импульсов за бчёт соответствующего сложения сигналов на логи ческих элементах ЗЙ-ИЛИ НЕ происходит возвращение делителей частоты в исходнов состояние, как это происходит в обы ных кольцевых делителях . - . ...-....., Благодаря налиящо сигналов на входа логических элементов ЗИ 41ЛИ-НЕ с вых дов последних триггеров каждого канала происходит фазирование каналов. При поступлении определенного числа импульсов на входнуто шину 25 каналы будут сфааированы, однако при этры могут ока&аться ложные состояния Включение логических элементов НЕ в каждом канале позволяет при различных начальных состояниях триггеров каждого канала сохранять работоспособность делителя за счет подачи сигнала обратной связи с выхода.логического элемента НЕ в каждом канале на Jt -iaxo ды первых двух триггеров данного канала, что вызывает запрещение работы, этих триггеров при определенных coctoHниях. Формул а изобретения Резервированный кольцевой делитель частоты 1мпулъсов, содержащий в каждом канале 5 ЭК-триггеров, счетные всходь которых Соединены с входной шиной, а прямой и инверсный, выходы каждого из которых соединены с соответствующими входами последующего, логический анемент ЗИ-ИЛИ-НЕ, входы каждого из логических элементов И которого соедине- ны соответственно с инверсньгми выходами последних Jt - риггеров каждого канала, а выход л(гвческбго элемента ЗИ-ИЛИ-НЕ ка ждого канала соединен с входом логического элемента НЕ и К-вхрДом первого JK -триггера данного ;Канала, ;о т л и ч аю щ и И с я тем, . что, с целью повь1шения надежности и умёнШения вероятности ложных срабатываний в каждый канал делители введен дополнительный логический элемент НЕ, один вход которого соединен с инверсным выходом предпоследнего Jftf -триггера данного какала, второй вход - с выходом логического элемента ЗИ-ИЛИ- ffi, а выход йодключён кТ -входам первых двух Jtf -триггеров данного канала, причем выход логического элемента НЕ соединен-с У -входом первого ЗК- григ- гера данного канала. Источники информации, принятые во внимание при экспертизе 1.Лейнов М. Л. и др. Цифровые делйТёЛн частоты на логических элементах, М., Энергия, 1975, с. 73. 2. № 2096729/21, кл. И 03 К 23/р2д 31.01.75, по которой принято решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Резервированный делитель частоты импульсов | 1977 |

|

SU698130A2 |

| Цифровой преобразователь частоты | 1988 |

|

SU1557669A1 |

| Устройство для вычитания частот двух независимых сигналов | 1976 |

|

SU599227A1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Синхронный делитель частоты на 16 | 1984 |

|

SU1225010A1 |

| Устройство для синхронизации резервированного делителя частоты | 1981 |

|

SU1001104A1 |

| Устройство для дискретной регулировки фазы | 1982 |

|

SU1027639A1 |

| Кольцевой делитель частоты | 1979 |

|

SU784006A1 |

| Трехканальный резервированныйРАСпРЕдЕлиТЕль иМпульСОВ | 1978 |

|

SU798848A1 |

Авторы

Даты

1979-07-25—Публикация

1978-02-24—Подача