74

сл ел ч

о

О5 QD

Изобретение относится к импульсной технике и может применяться для построения синтезаторов частоты.

Цель изобретения - повышение на- дежности работы цифрового преобразователя частоты при одновременном улучшении спектра выходного сигнала.

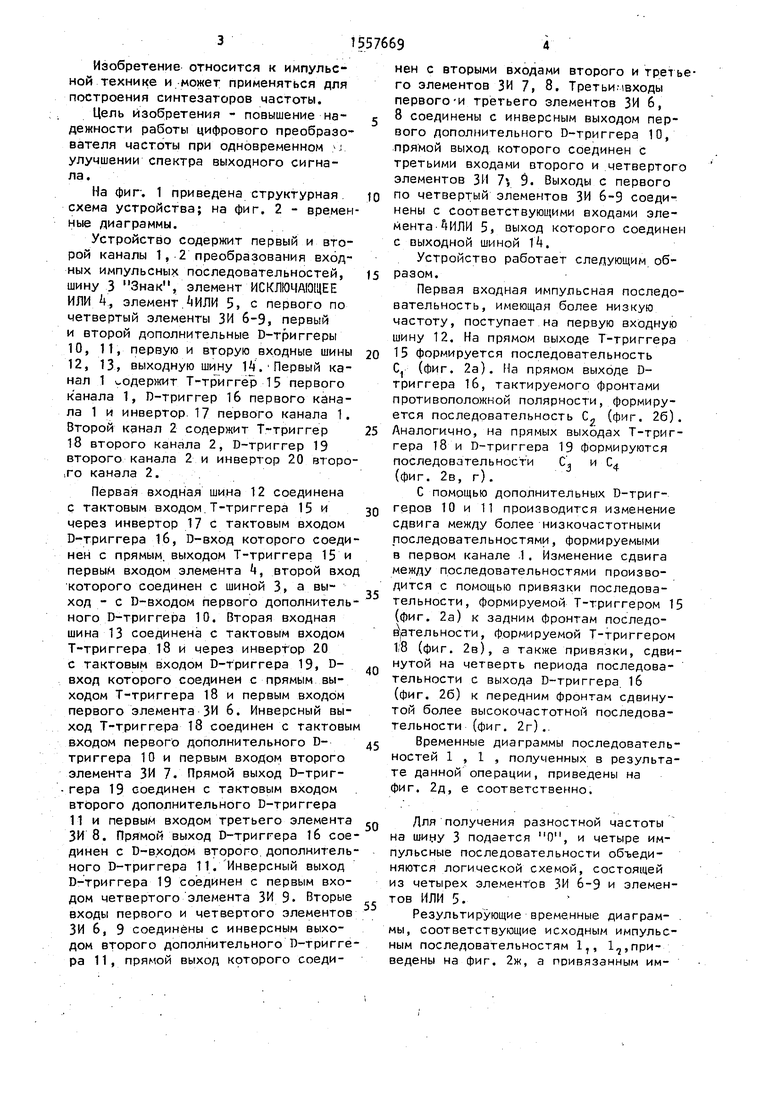

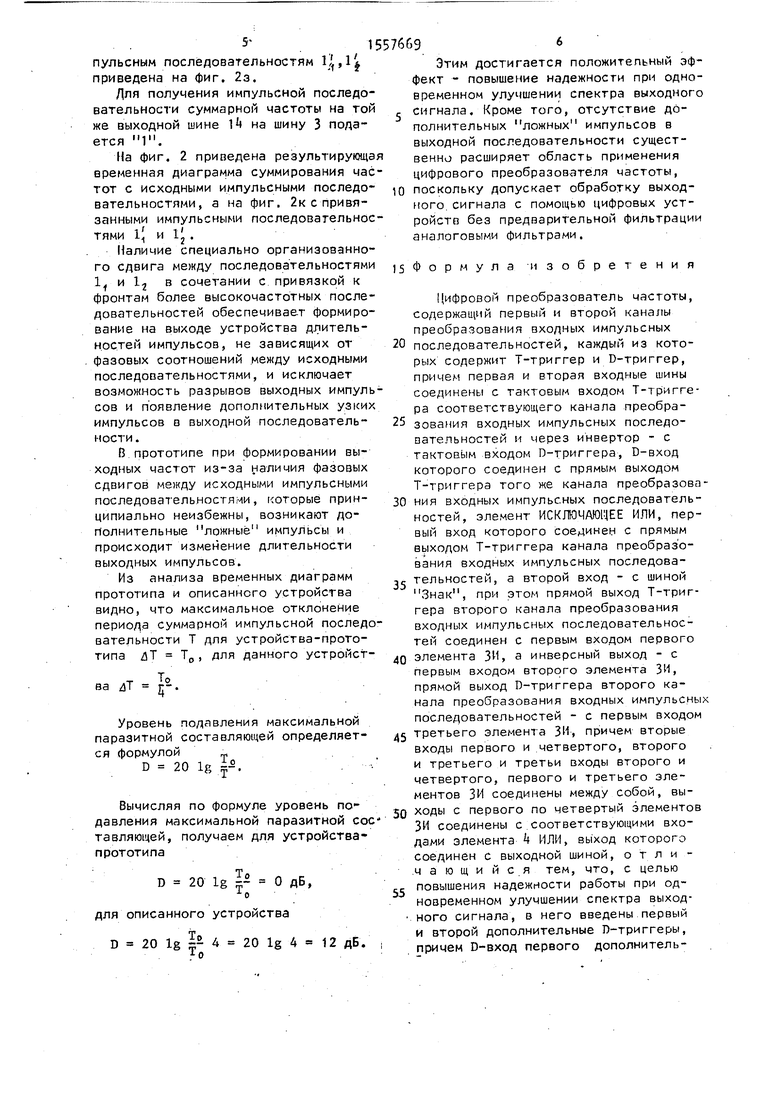

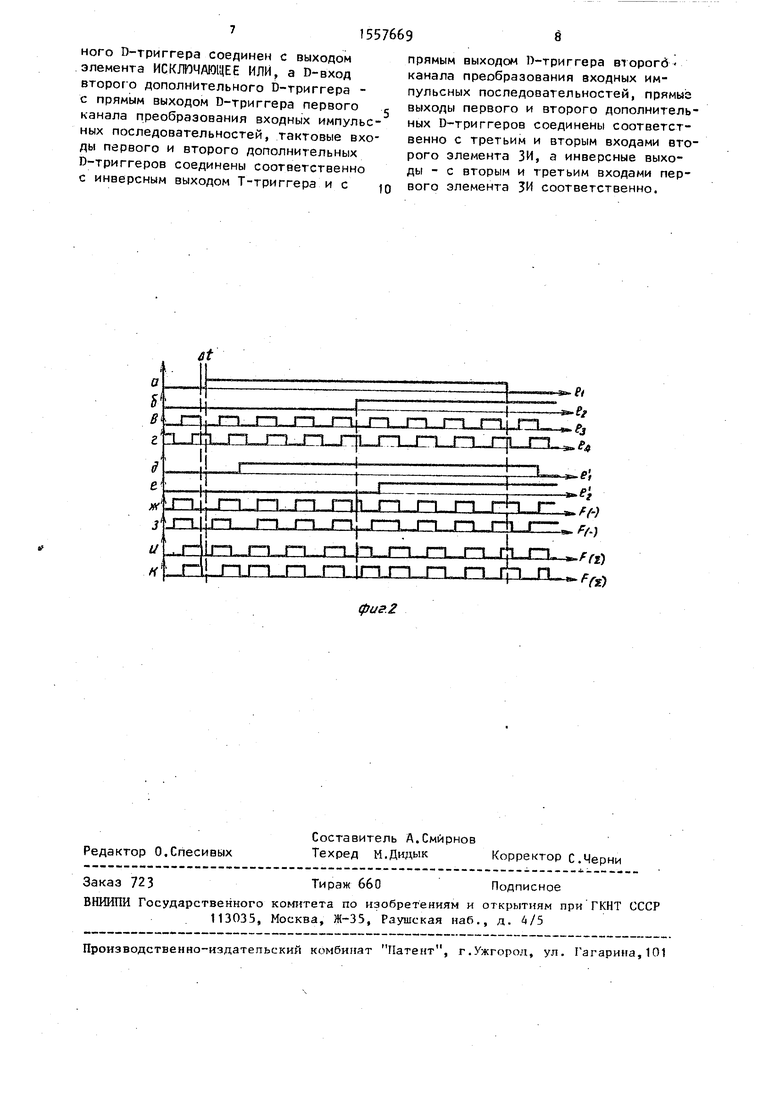

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы.

Устройство содержит первый и второй каналы 1, 2 преобразования входных импульсных последовательностей, шину 3 Знак, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элемент ИЛИ 5, с первого по четвертый элементы ЗИ 6-9, первый и второй дополнительные D-триггеры 10, 11, первую и вторую входные шины 12, 13, выходную шину 1Ц. Первый канал 1 одержит Т-триггер 15 первого канала 1, D-триггер 16 первого канала 1 и инвертор 17 первого канала 1. Второй канал 2 содержит Т-триггер 18 второго канала 2, D-триггер 19 второго канала 2 и инвертор 20 второ- ,го канала 2.

Первая входная шина 12 соединена с тактовым входом Т-триггера 15 и через инвертор 17 с тактовым входом D-триггера 1б, D-вход которого соединен с прямым, выходом Т-триггера 15 и первым входом элемента , второй вход которого соединен с шиной 3, а вы- ход - с D-входом первого дополнительного D-триггера 10. Вторая входная шина 13 соединена с тактовым входом Т-триггера 18 и через инвертор 20 с тактовым входом D-триггера 19 D- вход которого соединен с прямым выходом Т-триггера 18 и первым входом первого элемента ЗИ 6. Инверсный выход Т-триггера 18 соединен с тактовы входом первого дополнительного D- триггера 10 и первым входом второго элемента ЗИ 7. Прямой выход D-триг- гера 19 соединен с тактовым входом второго дополнительного D-триггера 11 и первым входом третьего элемента ЗИ 8. Прямой выход D-триггера 1б соединен с D-входом второго дополнительного D-триггера 11. Инверсный выход D-триггера 19 соединен с первым входом четвертого элемента ЗИ 9. Вторые входы первого и четвертого элементов ЗИ 6, 9 соединены с инверсным выходом второго дополнительного D-триггера 1 1 , прямой выход которого соедиС3 и С4

нен с вторыми входами второго и третьго элементов ЗИ 7, 8. Третьи.мвходы первого-и третьего элементов ЗИ 6, 8 соединены с инверсным выходом первого дополнительного D-триггера 10, прямой выход которого соединен с третьими входами второго и четвертого элементов ЗИ 1 9. Выходы с первого по четвертый элементов ЗИ 6-9 соединены с соответствующими входами элемента $ИЛИ 5, выход которого соединен с выходной шиной 14.

Устройство работает следующим образом.

Первая входная импульсная последовательность, имеющая более низкую частоту, поступает на первую входную шину 12. На прямом выходе Т-триггера 15 формируется последовательность С1 (фиг. 2а). На прямом выходе D- триггера 16, тактируемого фронтами противоположной полярности, формируется последовательность С„ (фиг. 26). Аналогично, на прямых выходах Т-триггера 18 и D-триггера 19 формируются последовательности (фиг. 2в, г).

С помощью дополнительных D-триг- геров 10 и 11 производится изменение сдвига между более низкочастотными последовательностями, формируемыми в первом канале 1. Изменение сдвига между последовательностями производится с помощью привязки последовательности, формируемой Т-триггером 15 (фиг. 2а) к задним фронтам последовательности, формируемой Т-триггером 1.8 (фиг. 2в), а также привязки, сдвинутой на четверть периода последовательности с выхода D-триггера 16 (фиг. 26) к передним фронтам сдвинутой более высокочастотной последовательности (фиг. 2г).

Временные диаграммы последовательностей 1,1, полученных в результате данной операции, приведены на фиг. 2д, е соответственно.

Для получения разностной частоты на шину 3 подается О, и четыре импульсные последовательности объединяются логической схемой, состоящей из четырех элементов ЗИ 6-9 и элементов ИЛИ 5.

Результирующие временные диаграммы, соответствующие исходным импульсным последовательностям 1,, 1,приведены на фиг. 2ж, а привязанным импульсным последовательностям H,li приведена на фиг. 2з.

Для получения импульсной последовательности суммарной частоты на той же выходной шине 1 на шину 3 подается 1.

На фиг. 2 приведена результирующа временная диаграмма суммирования частот с исходными импульсными последовательностями, а на фиг. 2кс привязанными импульсными последовагельностями

i; и ii

Наличие специально организоаанно- го сдвига между последовательностями I,, и 12 в сочетании с привязкой к фронтам более высокочастотных последовательностей обеспечивает формирование на выходе устройства длительностей импульсов, не зависящих от фазовых соотношений между исходными последовательностями, и исключает возможность разрывов выходных импульсов и появление дополнительных узких импульсов в выходной последовательности.

В прототипе при формировании выходных частот из-за наличия фазовых сдвигов между исходными импульсными последовательностями, которые принципиально неизбежны, возникают дополнительные ложные импульсы и происходит изменение длительности выходных импульсов.

Из анализа временных диаграмм прототипа и описанного устройства видно, что максимальное отклонение периода суммарной импульсной последовательности Т для устройства-прототипа ДТ Т0, для данного устройства

4Т ,

Уровень подавления максимальной паразитной составляющей определяется формулой т D 20 lg i.

Вычисляя по формуле уровень подавления максимальной паразитной сотавляющей, получаем для устройства- прототипа

D 20 lg 0 дБ, io

описанного устройства

20 lg 4

20 lg jk 4 lo

12 дБ.

1557669

0

5

Этим достигается положительный эффект - повышение надежности при одновременном улучшении спектра выходного сигнала. Кроме того, отсутствие дополнительных ложных импульсов в выходной последовательности существенно расширяет область применения цифрового преобразователя частоты, Ю поскольку допускает обработку выходного сигнала с помощью цифровых устройств без предварительной фильтрации аналоговыми фильтрами.

5Формула изобретения

Цифровой преобразователь частоты, содержащий первый и второй каналы преобразования входных импульсных последовательностей, каждый из которых содержит Т-триггер и D-триггер, причем первая и вторая входные шины соединены с тактовым входом Т-тригге- ра соответствующего канала преобразования входных импульсных последовательностей и через инвертор - с тактовым входом D-триггера, В-вход которого соединен с прямым выходом Т-триггера того же канала преобразования входных импульсных последовательностей, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с прямым выходом Т-триггера канала преобразования входных импульсных последовательностей, а второй вход - с шиной Знак, при этом прямой выход Т-триггера второго канала преобразования входных импульсных последовательностей соединен с первым входом первого элемента ЗИ, а инверсный выход - с первым входом второго элемента ЗИ, прямой выход D-триггера второго канала преобразования входных импульсных последовательностей - с первым входом третьего элемента ЗИ, причем вторые входы первого и четвертого, второго и третьего и третьи входы второго и четвертого, первого и третьего элементов ЗИ соединены между собой, вы- о ходы с первого по четвертый элементов ЗИ соединены с соответствующими входами элемента k ИЛИ, выход которого соединен с выходной шиной, отличающийся тем, что, с целью повышения надежности работы при одновременном улучшении спектра выходного сигнала, в него введены первый и второй дополнительные П-триггеры, причем D-вход первого дополнитель0

5

0

5

715576

ного D-триггера соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а D-вход второго дополнительного D-триггера - с прямым выходом D-триггера первого канала преобразования входных импульсных последовательностей, тактовые входы первого и второго дополнительных D-триггеров соединены соответственно с инверсным выходом Т-триггера и с

10

8

прямым выходом D-триггера вюрогб- канала преобразования входных импульсных последовательностей, прямые выходы первого и второго дополнительных D-триггеров соединены соответственно с третьим и вторым входами второго элемента ЗИ, а инверсные выходы - с вторым и третьим входами первого элемента ЗИ соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство регулируемой задержки | 1984 |

|

SU1175020A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для контроля резервированного генератора | 1987 |

|

SU1457147A1 |

| Цифровой фазовращатель | 1984 |

|

SU1213434A1 |

| Синхронизатор импульсов | 1985 |

|

SU1347172A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1988 |

|

SU1737731A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

Изобретение относится к импульсной технике и может быть использовано в синтезаторах частоты. Цель изобретения - повышение надежности работы при одновременном улучшении спектра выходного сигнала. С этой целью в преобразователь, содержащий каналы 1 и 2 преобразования входных импульсных последовательностей, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элемент 4ИЛИ 5, элементы 3И 6, 7, 8, 9, введены D-триггеры 10, 11. При подаче на шину 3 логического "О" на выходе преобразователя формируется разностная частота, а при подаче логической "1" - суммарная частота, причем частота входных импульсов на шине 12 должна быть меньше, чем на шине 13. D-триггеры 10, 11 обеспечивают привязку фазы преобразованных низкочастотных последовательностей к фазе преобразованных высокочастотных последовательностей. Благодаря этому в выходном сигнале устраняются ложные импульсы. 2 ил.

| Устройство для получения суммы и разности частот двух импульсных последовательностей | 1983 |

|

SU1109764A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Васильев В.И | |||

| Расчет спектра выходного сигнала двухканального импульсного формирователя | |||

| // - Вопросы радиоэлектроники | |||

| Сер | |||

| ПРВ, 1984, вып | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

Авторы

Даты

1990-04-15—Публикация

1988-06-15—Подача