1

Изобретение относится к радио- технике и предназначено для использования в спектрометрии ионизирующих измерений.

Известен аналого-цифровой преобразователь , содержащий дискриминатор уровня, генератор эталонов, устройство выборки и хранения flj .

Недостатком устройства является низкое быстродействие.

Известен аналого-цифровой преобразователь, содержащий входное устройство, соединенное с первым входом коь 4утатора, выход которого через последовательно соединенные сумматор две ячейки памяти соединен со своим ВТ9РЫМ входом, второй вход сумматора через генератор эталонов, блок управления генератором эталонов соединен с выходом задающего генератора, выход сумматора через дискриминатор уровня соединен с входом регистра сдвига, выход которого соединен с входом блока вывода кода, логические входы и выходы входного устройства, коммутатора, ячеек памяти, дискриминатора уровня, регистра сдвига, блока вывода кода и задающего генератора соединены с блоком управления 2.

Недостатком устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия.

Указанная цель достигается тем, что в аналого-цифровой преобразователь , содержащий входное устройство, две.ячейки памяти, коммутатор, сум0матор, дискриминатор уровня, задающий генератор, блок синхронизации, блок эталонных генераторов, блок распределения, счетчик импульсов, арифметическое устройство, блок вывода

5 кода и блок управления, введены интегратор, разрядное устройство, блок эталонной длительности и дополнительный дискриминатор уровня, причем вход дополнительного дискримина0тора уровня соединен со входом входного устройства, а выход подключен к третьему входу блока управления, вход интегратора соединен с выходом разрядного устройства и через генера5тор эталонного тока блок -эталонной длительности подключен к выходу блока синхронизации, а выход соединен со вторым входом сумматора и входом разрядного устройства, логический

0 выход которого соединен с соответтвующим логическим выходом блока правления.

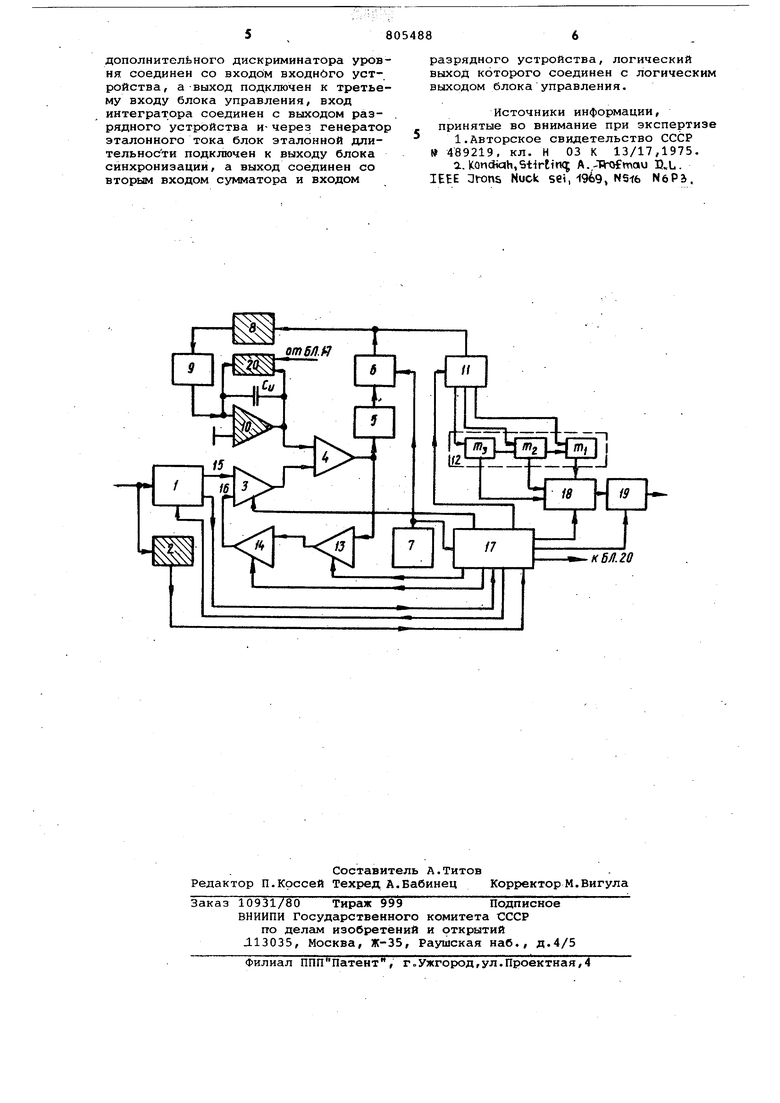

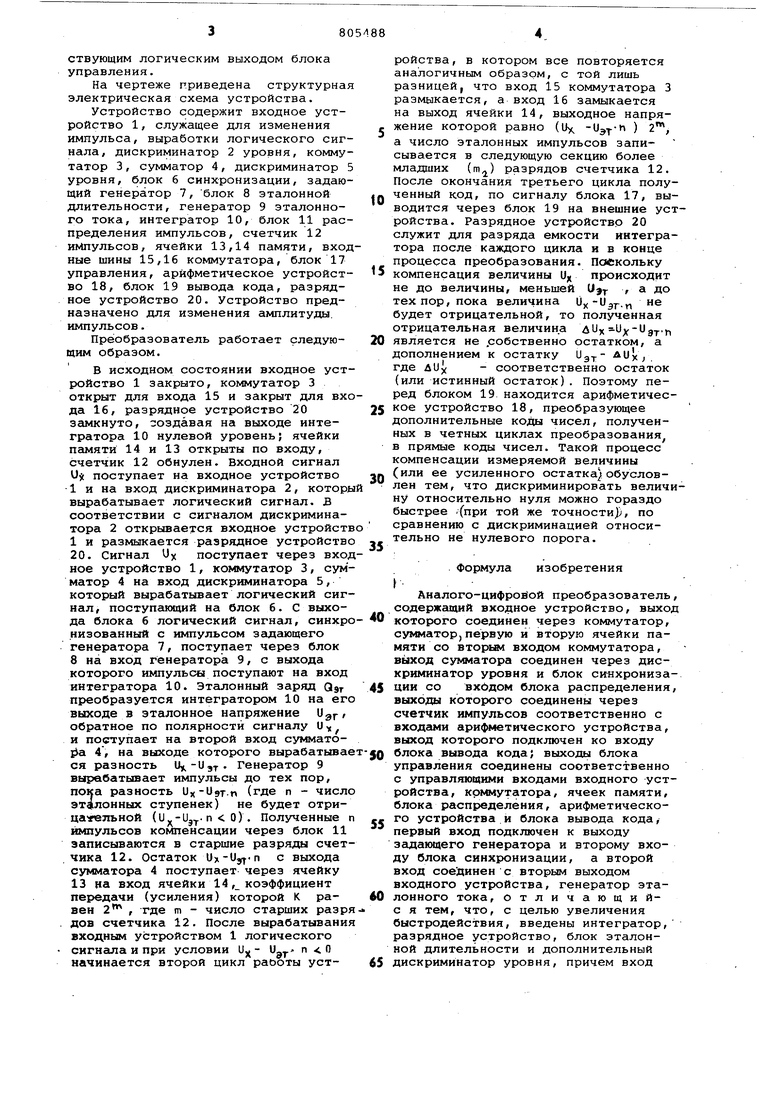

На чертеже приведена структурная электрическая схема устройства.

Устройство содержит входное устойство 1, служащее для изменения мпульса, выработки логического сигнала, дискриминатор 2 уровня, коммутатор 3, сумматор 4, дискриминатор 5 ровня, блок 6 синхронизации, задаюий генератор 7, блок 8 эталонной .лительности, генератор 9 эталонноо тока, интегратор 10, блок 11 расределения импульсов, счетчик 12 импульсов, ячейки 13,14 памяти, входные шины 15,16 коммутатора, блок 17 правления, арифметическое устройст- 5 во 18, блок 19 вывода кода, разрядное устройство 20. Устройство предназначено для изменения амплитуды, мпульсов.

Преобразователь работает следую- 20 им образом.

В исходном состоянии входное устройство 1 закрыто, коммутатор 3 открыт для входа 15 и закрыт для входа 16, разрядное устройство 20 25 замкнуто, создавая на выходе интегратора 10 нулевой уровень; ячейки памяти 14 и 13 открыты по входу, счетчик 12 обнулен. Входной сигнал и поступает на входное устройство JQ 1 и на вход дискриминатора 2, который вырабатывает логический сигнал. В соответствии с сигналом дискриминатора 2 открывается входное устройство 1 и размыкается разрядное устройство j 20. Сигнал Uy поступает через входное устройство 1, коммутатор 3, сумматор 4 на вход дискриминатора 5, который вырабатывает логический сигнал, поступающий на блок 6. С выхода блока б логический сигнал, синхро- « низованный с импульсом задающего генератора 7, поступает через блок 8 на вход генератора 9, с выхода которюго импульсы поступают на вход интегратора 10. Эталонный заряд Qj 4S преобразуется интегратором 10 на его выходе в эталонное напряжение Ugr/ обратное по полярности сигналу U и поступает на второй вход суммато а 4, на выходе которого вырабатывает-JQ ся разность ,T- Генератор 9 вырабатывает импульсы до тех пор/ пока разность UxUgr-n (где п - число эталонных ступенек) не будет отрицагетп.ной ( 0) . Полученные п ,. импульсов компенсации через блок 11 записываются в старшие разряды счетчика 12. Остаток Ux-Uy|-n с выхода сумматора 4 поступает- через ячейку 13 на вход ячейки 14, коэффициент передачи (усиления) которой К ра- 60 вен 2 , где m - число старших разрядов счетчика 12. После вырабатывания входным устройством 1 логического сигнала и при условии U - U. n 0 начинается второй цикл раьоты уст- 65

ройства, в котором все повторяется аналогичным образом, с той лишь разницей, что вход 15 коммутатора 3 размыкается, а вход 16 замыкается на выход ячейки 14, выходное напряжение которой равно (Ux ) 2, а число эталонных импульсов записывается в следующую секцию более младших (т) разрядов счетчика 12. После окончания третьего цикла полученный код, по сигналу блока 17, выводится через блок 19 на внешние усройства. Разрядное устройство 20 служит для разряда емкости интегратора после каждого цикла и в конце процесса преобразования. Поскольку компенсация величины U происходит не до величины, меньшей Uj , а до тех пор, пока величина ..„ не будет отрицательной, то полученная отрицательная величина ди -Uif-Ug.j является не .собственно остатком, а дополнением к остатку зг У t . где uUJ( - соответственно остаток (или истинный остаток). Поэтому перед блоком 19 находится арифметическое устройство 18, преобразующее дополнительные коды чисел, полученных в четных циклах преобразования, в прямые коды чисел. Такой процесс компенсации измеряемой величины (или ее усиленного остатка)обусловлен тем, что дискриминировать величну относительно нуля можно гораздо быстрее .{при той же точности};, по сравнению с дискриминацией относительно не нулевого порога.

Формула изобретения

-

Аналого-цифровой преобразователь содержащий входное устройство, выхо которого соединен через коммутатор, сумматор,первую и вторую ячейки памяти со sTOptof входом коммутатора, выход сумматора соединен через дискриминат-ор уровня и блок синхронизации со входом блока распределения выходы которого соединены через счетчик импульсов соответственно с входами арифметического устройства, выход которого подключен ко входу блока вывода кода; выходы блока управления соединены соответственно с управляющими входами входного устройства, коммутатора, ячеек памяти, блока распределения, арифметического устройства и блока вывода кода, первый вход подключен к выходу згщающего генератора и второму входу блока синхронизации, а второй вход соединен с вторым выходом входного устройства, генератор эталонного тока, отличающийс я тем, что, с целью увеличения быстродействия, введены интегратор, разрядное устройство, блок эталонной длительности и дополнительный дискриминатор уровня, причем вход

дополнительного дискриминатора уровня соединен со входом входного устройства, а-выход подключен к третьему входу блока управления, вход интегратора соединен с выходом разрядного устройства и- через генератор эталонного тока блок эталонной длительности подключен к выходу блока синхронизации, а выход соединен со вторым входом сумматора и входом

разрядного устройства, логический выход которого соединен с логическим выходом блока управления.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 489219, кл. Н 03 К 13/17,1975,

а. lConcHcih,StirtirK5 A.-fl-ofmau D,L. IEEE Nuck sei,-1969, Ns-(6 NePa.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU805487A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU1170606A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU894860A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство измерения параметров дисбаланса | 1990 |

|

SU1795318A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU664293A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU683017A1 |

| Устройство формирования сигнала для коррекции искажений телевизионного изображения | 1985 |

|

SU1317687A2 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Устройство для измерения ошибок позиционирования шагового электродвигателя | 1990 |

|

SU1697254A1 |

Авторы

Даты

1981-02-15—Публикация

1979-02-05—Подача