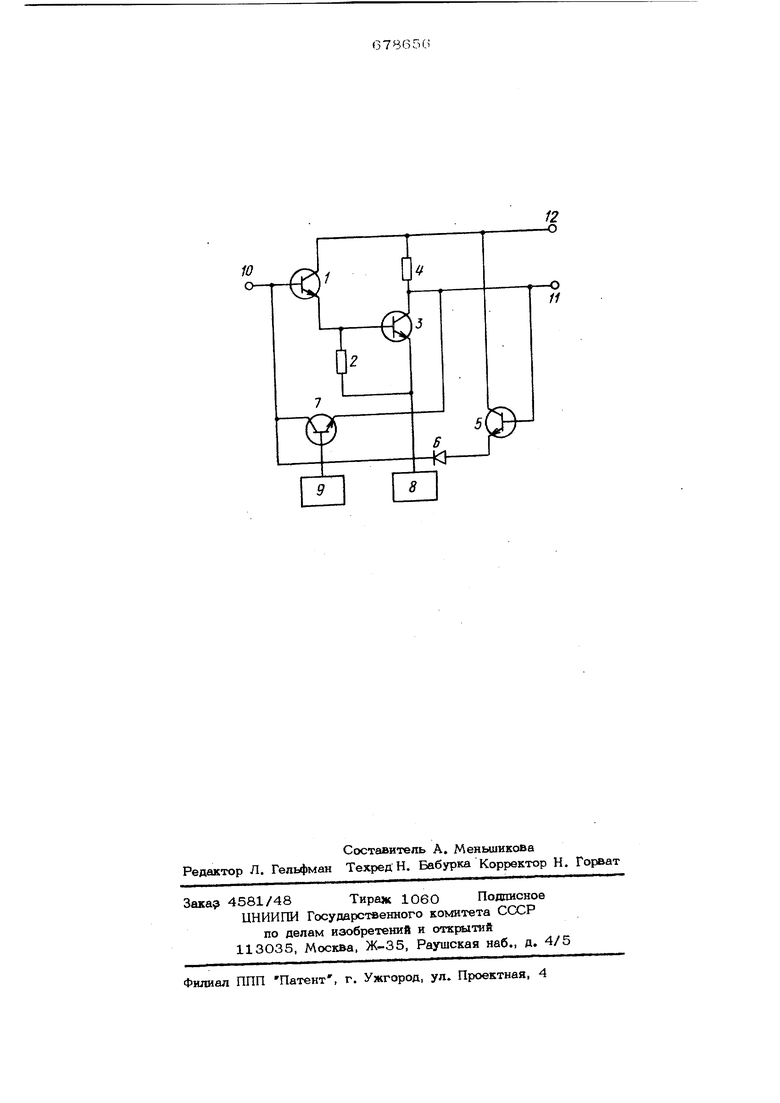

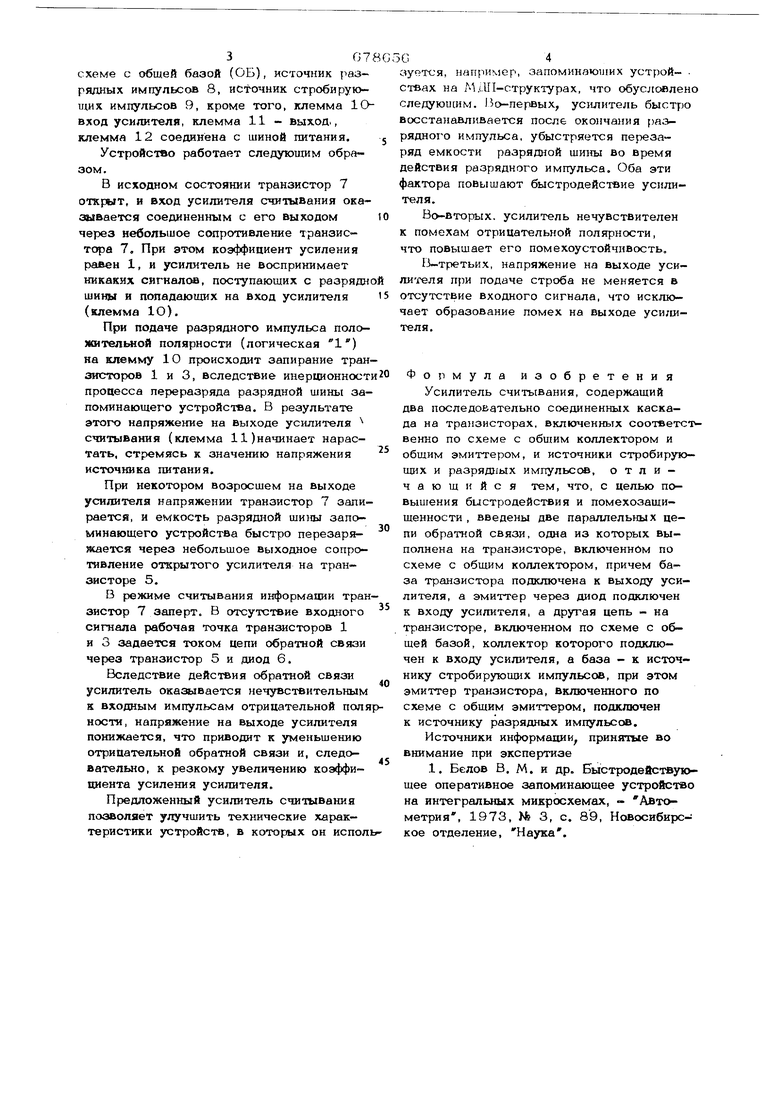

Изобретение относится к вычислительной технике и может использоваться в запоминающюс устройствах на МДП-струкоурах. Известен усилитель считывания, содер жащий два последовательно соединенных каскада на транзисторах, включенных соответственно по схема с общим коллектором и общим эмиттером, и источники стробирующих и разрядных импульсов .1 Однако известный усилитель считывания имеет низкое быстродействие и ннэкую помехозащищенность. Цель изобретения - повышение быстродействия и помехозащищенности. Для этого в усилитель считывания, содержащий два последовательно соединенных каскада на транзисторах, включенных соответственно по схеме с общим кол лектором и общим эмиттером, и источни ки стробирующих и разрядных импульсов, введены две параллельных цепи обратной свази, одна из которых выполнена на транзисторе, включенном по схеме с общим коллектором, причем база транзисгора подключена к выходу усилителя, а эмиттер через диод подключен к входу усилителя, а другая цепь - на транзисторе , включенном по схеме с общей ба1зой, коллектор которого подключен к входу усилителя, а база - к источнику стробирующих импульсов, при этом эмиттер транзистора, включенного по схеме с общим эмиттером, подключен к источнику разрядных импульсов. На чертеже приведена электрическая принципиальная схема предложенного усилителя. Усилитель считывания содержит усилитель, выполненный на транзисторе 1 и резисторе 2 по схеме с общим коллектором (ОК), усилитель, выполненный на транзисторе 3 с резистором 4 по схеме с общим эмиттером (ОЭ) ,цепь обратной свази, выполненную на транзисторе 5, ченном по схеме с общим коллектором, лиод 6, цепь обратной связи, выполненную на транзисторе 7, включенном по 3G7 схеме с общей базой (ОБ), источник разрядных импульсов 8, источник стробирующих импульсов 9, кроме того, клемма 1О вход усилителя, клемма 11 - выход., клемма 12 соединена с шиной питания. Устройство работает следуюишм образом, В исходном состоянии транзистор 7 открыт, и вход усилителя считывания оказывается соединенным с его выходом через небольшое сопротивление транзистора 7, При этом коэффициент усиления равен 1, и усилитель не воспринимает никаких сигналов, поступающих с разрядн шины и попадающих на вход усилителя (клемма Ю). При подаче разрядного импульса положительной полярности (логическая 1) на клемму Ю происходит запирание тран зисторов 1 и 3, вследствие инерционност процесса переразряда разрядной шины запоминающего устройства. В результате этого напряжение на выходе усилителя считывания (клемма 11)начинает нарастать, стремясь к значению напряжения источника питания. При некотором возросшем на выходе усилителя напряжении транзистор 7 запирается, и емкость разряд11ой шины запоминающего устройства быстро перезаряжается через небольшое выходное сопротивление открытого усилителя на транзисторе 5. В режиме считывания информации тран зистор 7 заперт. В отсутствие входного сигнала рабочая точка транзисторов 1 и 3 задается током цепи обратной связи через транзистор 5 и диод 6. Вследствие действия обратной связи усилитель оказывается нечувствительным к входным импульсам отрицательной поля ности, напряжение на выходе усилителя понижается, что приводит к уменьшению отрицательной обратной связи и, следовательно, к резкому увеличению коэффициента усиления усилителя. Предложенный усилитель считывания позволяет у; чшить технические характеристики устройств, в которых он испол G4 уется, например, запоминаю1лих устрой- . твах на МДП-структурах, что обусловлено ледующим. 15о-первых, усилитель быстро осстанавливается после окончания разряднот-о импульса, убыстряется перезаряд емкости разрядной шины во время действия разрядного импульса. Оба эти актора повышают быстродействие усилителя. Во-вторых, усилитель нечувствителен к помехам отрицательной полярности, что повышает его помехоустойчивость. 13-третьих, напряжение на выходе усиителя при подаче строба не меняется в отсутствие входного сигнала, что исклюает образование помех на выходе уси;штеля. Формула изобретения Усилитель считывания, содержащий два последовательно соединенных каскада на транзисторах, включенных соответственно по схеме с общим коллектором и общим эмиттером, и источники стробирую- щих и разрядных импульсов, отличающийся тем, что, с целью повышения быстродействия и помехозащищенности , введены две параллельных цепи обратной связи, одна из которых выполнена на транзисторе, включенном по схеме с общим коллектором, причем база транзистора подключена к выходу усилителя, а эмиттер через диод подключен к входу усилителя, а другая цепь - на транзисторе, включенном по схеме с общей базой, коллектор которого подключен к входу усилителя, а база - к источнику стробирующих импульсов, при этом эмиттер транзистора, включенного по схеме с общим эмиттером, подключен к источнику разрядных импульсов. Источники информации принятые во внимание при экспертизе 1. Белов В. М. и др. Быстродействук щее оперативное запоминающее устройство на интегральных микросхемах, - Автометрия, 1973, № 3, с. 89, Новосибирское отделение, Наука.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| Реле времени периодических включений | 1981 |

|

SU980186A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1994 |

|

RU2114500C1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Устройство реверсирования тока | 1985 |

|

SU1246359A1 |

| РАЗРЯДНЫЙ ФОРМИРОВАТЕЛЬ | 1972 |

|

SU327586A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| ФОРМИРОВАТЕЛЬ ТОКА ВЫБОРКИ | 1973 |

|

SU377869A1 |

Авторы

Даты

1979-08-05—Публикация

1976-12-10—Подача