(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Ассоциативное запоминающее устройство | 1977 |

|

SU662972A1 |

| Мультиплексный канал с динамическим распределением памяти | 1977 |

|

SU674010A2 |

| Мультиплексный канал | 1976 |

|

SU590725A2 |

| Мультиплексный канал с динамическим распределением памяти | 1973 |

|

SU526877A1 |

| Мультиплексный канал с косвенной адресацией памяти | 1973 |

|

SU514287A1 |

| Устройство обмена с косвенной адресацией | 1974 |

|

SU526878A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Устройство для связи процессора с запоминающим устройством | 1983 |

|

SU1083196A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в ассоциатив ных запоминающих устройствах. Одно из известных ассоциативных запоминающих устройств на основе обычных запоминающих элементов с адресной выборкой состоит из трех массивов: массива, хранящего инверсную адресную информацию, массива связи и основного массива. В этом устройстве признак опроса, подаваемый на вход памяти используется в качестве адреса: для выборки из первого массива слова, определяющего адрес ячей ки массива связи, в которую записан адрес ячейки основного запоминающегй устройства, содержащий слово с заданным признаком опроса 1. Недостатком известного устройства является его низкое быстродействие. Наиболее близким техническим решением к данному изобретению являет ся запоминающее устройство, содержа щее блок памяти адресов, входы кото рого соединены с выходами первого и второго адресных регистров и адресной шиной, а выход - с входом блока основной памяти, вход первого адрес ного регистра соединен с выходом блока определения- свободной ячейки основной памяти, вход которого подключен к одним из выходов регистра занятости ячейки основной памяти, другие выходы и входы которого соединены соответственно с входами и выходами блока памяти признаков занятости ячеек основной памяти, информационные и выходные шины 2. Недостатком данного устройства является малое быстродействие, обусловленное тем, что в режиме поиска адреса свободной зоны последовательно опрашиваются в блоке памяти адpecoBf- все ячейки таблицы занятости зон блока памяти. Целью данного изобретения является повышение быстродействия запоминающего устройства. Поставленная цель достигается тем, что запоминающее устройство содержит блок определения свободных зон основной памяти, регистр занятости зон основной памяти и элемент И, входы которого соединены с cof- ветствующими выходами регистра занятости ячеек основной памяти, а выходы подключены к входам регистра занятости зон основной памяти, выходы которого соединены с входами блока определения свободных зон основной памяти, выходы которого подключены к входам второго адресного регистра и входам блока памяти признаков занятости ячеек основной памяти.

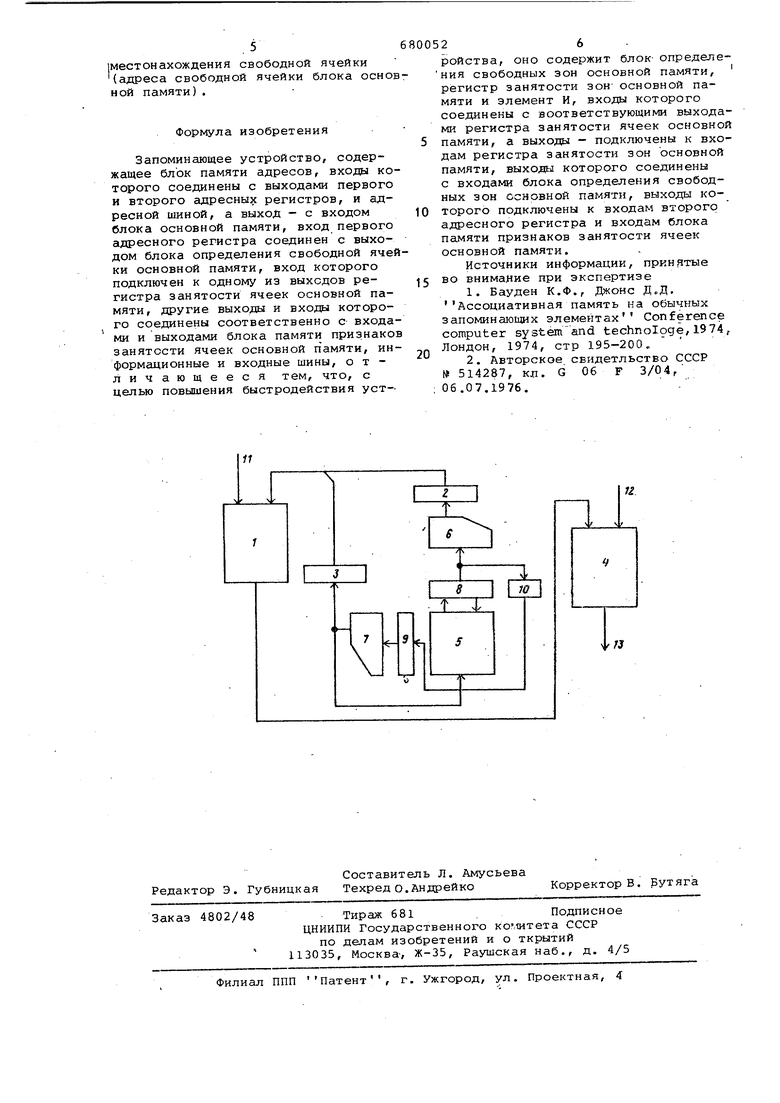

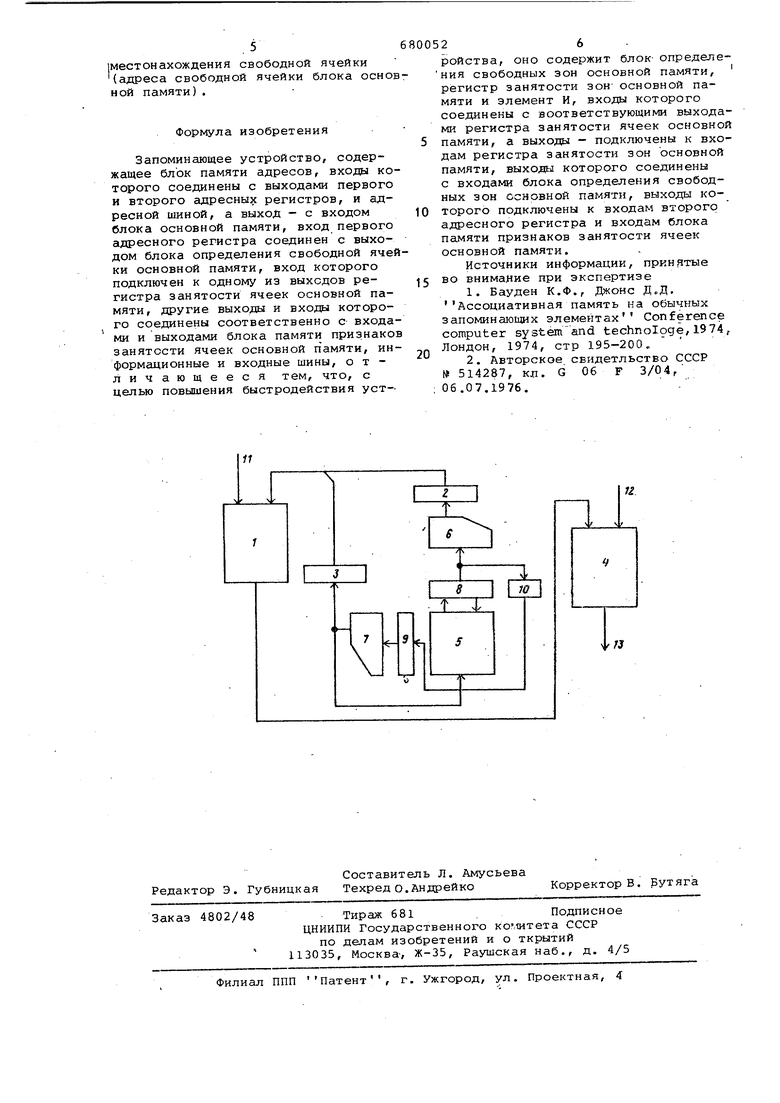

На чертеже представлена функциональная блок-схема запоминающего устройства.

Устройство содержит блок памяти адресов 1, первый адресный регистр 2, второй адресный регистр 3, блок основной памяти 4, блок 5 памяти признаков занятости ячеек основной памяти, блок 6 определения свободной ячейки основной памяти, блок 7 определения свободной зоны основной памяти, регистр 8 занятости ячеек основной памяти, регистр 9 занятости зон основной памяти, элемент И 1 адресные шины 11, информационные 12 и выходные шины 13.

Запоминающее устройство представляет робой запоминающее устройство Ь косвенной адресацией. Адрес обращения к запоминающему устройству .соответствует ячейке в блоке памяти адресов 1, а информация хранится в блоке основной памяти 4 в ячейке, соответствующей адресу обращения к блоку 1. Блок основной памяти 4 условно разбит на зоны. Количество зон равно числу ячеек блока 5 памяти .признаков занятости. Зона блока основной памяти состоит из К ячеек, где К - разрядность ячейки блока 5.« Каждый разряд ячейки блока 5 характеризует состояние соответствующей ячейки блока 4. Занятой ячейке соответствует единичный код.

Количество разрядов регистра занятости зон основной памяти 9 равно количеству ячеек блока 5 и соответственно количеству зон основной памяти. Каждый разряд регистра 9 показывает, имеются ли в соответствующих зонах блока основной памяти свободные ячейки. Свободной зоне основной памяти соответствует нулевое состояние соответствующего разряда регистра 9.

Блок определения свободной ячейк основной памяти 6 формирует адрес свободной ячейки в зоне основной памяти, стоящей первой в зоне в порядке возрастания адресов. о Работа запоминающего устройства (ЗУ) происходит следующим образом.

Начальным сбросом устройство приводится в исходное состояние (сбрасываются все регистры и очищаются ячейки памяти).

После начального сброса устройство переходит в режим поиска свободной ячейки блока основной памяти 4. Блок 7 определения свободной зоны основной памяти анализирует состояние регистра 9 и формирует адрес свободной зоны, расположенной первой в порядке возрастания адресов. Код адреса зоны блока основной памяти 4 записывается на второй адресный регистр 3. По этому же адресу производится считывание содержимого ячейки из блока памяти 5. Состоя5 ние каждого разряда ячейки блока памяти 5 отражает состояние ячеек памяти соответствующей зоны блока основной памяти 4. Блок 6 определения свободной ячейки основной памяти

0 анализирует содержимое регистра 8 занятости ячеек основной памяти, формирует адрес свободной ячейки, первой в порядке возрастания адресов и заносит его на первый адресный ре5 гистр 2. После этого производится перевод соответствующего разряда регистра 8 в состояние занято и элемент И 10 повторяет, иметотс.я ли еще свободные ячейки в данной зоне

Q основной памяти. Если все разряды находятся в состоянии занято, то переводится в состояние зона занята соответствующий разряд регистра 9. Если же элемент И 10 определит наличие свободных ячеек в данной зоне основной памяти, то содержимое регистра 9 не меняется. Далее следует перепись содержимого регистра 8 в блок памяти 5 в ту же ячейку, откуда оно было считано, по адресу,

0 сформированному блоком определения свободной зоны основной памяти 7.

В результате получен адрес свободной ячейки блока основной памяти 4, состоящий из адреса зоны основ5 ной памяти, записанного во втором адресном регистре 3 и адреса ячейки Пс1мяти в данной зоне, записанного в первый адресный регистр 2.

При первом обращении внеинего

0 устройства к ЗУ в режиме записи информации этому устройству предоставляется подготовленный адрес свободной ячейки блока основной памяти 4. Этот адрес заносится в соответствуюc щую ячейку блока памяти адреса 1 и по нему производится запись информации со входных информационных шин 12 в блок основной памяти 4.

При повторном обращении внешнего

устройства к ЗУ из блока памяти адресов 1 выбирается соответству-ющий внешнему устройству адрес обращения к блоку основной памяти 4 и в ависимости от режима работы ЗУ, производится либо запись информации с

входных информационных шин 12 в адресованную ячейку блока основной памяти 4, либо чтение информации из адресованной ячейки блока 4 на выходные информационные шины 13.

Таким образом, предложенное устройство позволяет добиться значительного сокращения времени поиска свободной ячейки основной памяти за счет того, что.одновременно ведется

анализ наличия свободной зоны и 1местонахождения свободной ячейки (адреса свободной ячейки блока осно ной памяти). Формула изобретения Запоминающее устройство, содержащее блок памяти адресов, входы ко торого соединены с выходами первого и второго адресных регистров, и адресной шиной, а выход - с входом блока основной памяти, вход первого адресного регистра соединен с выходом блока определения свободной яче ки основной памяти, вход которого подключен к одному из выходов регистра занятости ячеек основной памяти, другие выходы и входы которого соединены соответственно с входа ми и выходами блока памяти признако занятости ячеек основной памяти, ин формационные и входные шины, отличающееся тем, что, с целью повышения быстродействия уст11

К 26 ройства, оно содержит блок определения свободных зон основной памяти, регистр занятости зон основной па мяти и элемент И, входы которого соединены с воответствующими выходами регистра занятости ячеек основной памяти, а выходы - подключены к входам регистра занятости зон основной памяти, выхода которого соединены с входами блока определения свободных зон основной памяти, выходы которого подключены к входам второго адресного регистра и входам блока памяти признаков занятости ячеек основной памяти. Источники информации, принятые во внимание при экспертизе 1.Бауден К.Ф., Джонс Д.Д, Ассоциативная память на обычных запоминающих элементах Conference computer system and technologe,1974, Лондон, 1974, стр 195-20а„ 2.Авторское свидетльство СССР 1 514287, кл. G 06 F 3/04/ 06.07.1976.

Авторы

Даты

1979-08-15—Публикация

1977-05-10—Подача