Допустим необходимо решить Систему линейных алгебраических уравнений вида:

А . ,

где Л -„матрица постоянных коэффициен тову

к - вектор неизвестных; b - вектор .правых частей, В первом такте работы устройства на вторые входы группы .сумматоров 4 поступают с третьих выходов блока управления

V

значения компонент вектора Ь первых (старших) разрядов компонент вектора правых частей и по сигналам управления, поступающим с четвертых выходов этого блока на управляющие входы группы сумматоров - осуществляется суммирование, компоX

нент вектора Ь с установленными вначале в группе сумма1Х)ров 4 компонентами пулевого вектора (кодом нуля). На выходах группы сумматоров 4 образуются значения компонент ненормализованного вектора

V

л1 (вектора, представленного без учета веса его ком понент в полноразрядных компонентах вектора х пеизвестных) первых разрядов компонент и скомого вежтора х неизвестных, которые поступают па входы блока сдвига информации и на входы блока памяти. По сигналам, поступающим с пятых и первых выходов блока управления на управляющие входы блока сдвига информации п блока памяти соответ1ственно, в блоке сдвига информации, осуществляющем сдвиг величИН входных разрядных векторов в сторону младщих разрядов па Ч:исло разрядов, -пропорцноналы-юе весу ком.понент разрядных векторов, что эквивалентно умножению их на соответствующую степень основания системы счисления, осуществляV

ется сдвиг вектора x па /(0 разрядов, а в блоке памяти осуществляется запомниаV

ние вектора х. На выходах блока сдвига

V

информации образуется величина л;,,, норма

лизованного вектора х, которая поступает на входы группы сумматоров 6, в которой по сигналам, поступающим с щестых выходов блока управления на управляющие входы группы сумматоров 6, суммируется с установленным вначале в группе сумматоров 6 нулевым вектором. На выходах группы сумматоров 6 образуется величина искомого вектора х неизвестных, равная на первом такте работы устройства величина векV

тора X(,|. По сигналам, поступающим с четвертых выходов блока управления на управляющие входы группы сумматоров 4, в последней вновь устанавливается нулевой вектор.

На втором такте работы устройства со вторых выходов блока управлепия па вторые входы блока 2 у.множения поступают величппы компонент матрицы Л2 вторых разрядов компонент матрицы постоянных коэффициентов, а по сигналам, поступающим с первых вьгходов блока управления на управляющие входы блока памяти, осуществляется считывание значений компоY

нент вектора х из блока памяти, которые поступают с выходов блока памяти на первые входы блока у.МНожения.

v

компонент вектора Лд х произведения поступают с выходов блока умножения на входы блока элементов НЕ, величины ко.мV

понент инвертированного вектора (-А Xi троизведения, с выходов которого по.ступаюг на первые входы группы сумматоров 4. На вторые входы этой группы поступают с третьих выходов блока управления величи пы компонепт вектора Ь вторых разрядов ком.понент вектора В. Но сигналам, поступающим с четвертых выходов блока управления на управляющие входы группы сумматоров 4, осуществляется суммирование векторов, .поступающих на первые и вторые входы этой группы. На выходах сумматора образуется величина Xz ненормализированного вектора вторых разрядов компонент вектора х неизвестных, которая поступает на входы блока сдвига информации блока памяти. :По сигналам, поступающим с пятых и первых выходов блока управления на управляющие входы блока сдвига информации и блока памяти соответственно, в блоке сдвига информации осуществляется

сдвиг вектора Xz на разряд вправо, а

V

в блоке памяти - запоминание вектора xzНа выходах блока сдв.ига информации получаются велн-чины компонент нормализоV

ванного вектора х .,„, которые поступают на входы группы сумматоров 6, где суммируются по сигналам, поступающим с щестых выходов блока управления на управляющие входы группы с)мматоров 6, с компонентаV

МИ вектора л:,,,- На выходах группы сумматоров 6 образуется величина искомого вектора X неизвестных, равная на втором такVV

те работы устройства ,, .,„. Но сигналам, поступающим па управляющие входы группы су.мматоров 4 с четвертых выходов блока управления, в сумматоре вновь устанавливается начальное значение - нулевой вектор. Аналогично на третьем такте работы устройства определяются величины

VV

0 Лзл:, и Л2Х2 на блоке умножения, величиVV

ны (-Лзл,) И () па блоке элементов НЕ, величины третьих компонент ненормаVVVV

лизованного вектора Хз Ьз-A Xi-AzXz па группе сумматоров 4, которые нормализуются сдвигом вправо на /(2 разрядов в блоке сдвига информации, а затем формируют величину искомого вектора х неизVVV

вестных (для третьего такта) -Гцгг- - н + лзн и т. д.

Число тактов работы устройства определяется требуемым числом разрядов компонент получаемого вектора хранения.

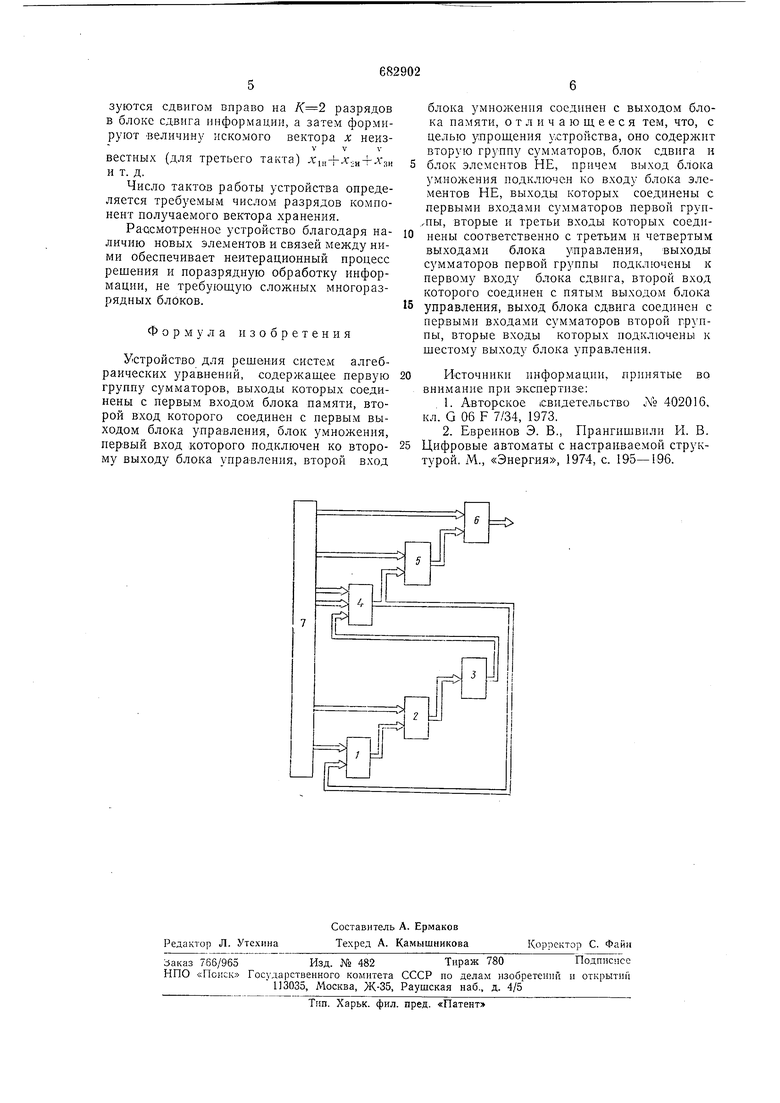

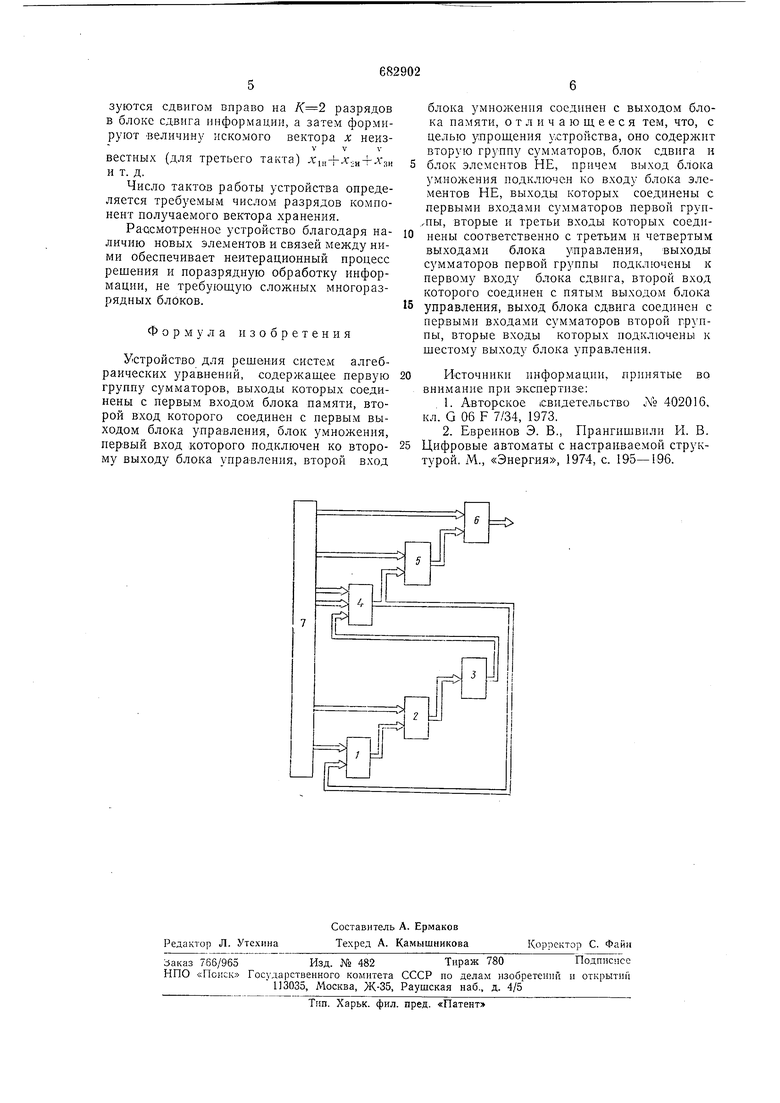

Раасмотренное устройство благодаря наличию новых элементов и связей между ними обеспечивает неитерационный процесс решения и поразрядную обработку информации, не требующую сложных многоразрядных блоков.

Формула изобретения

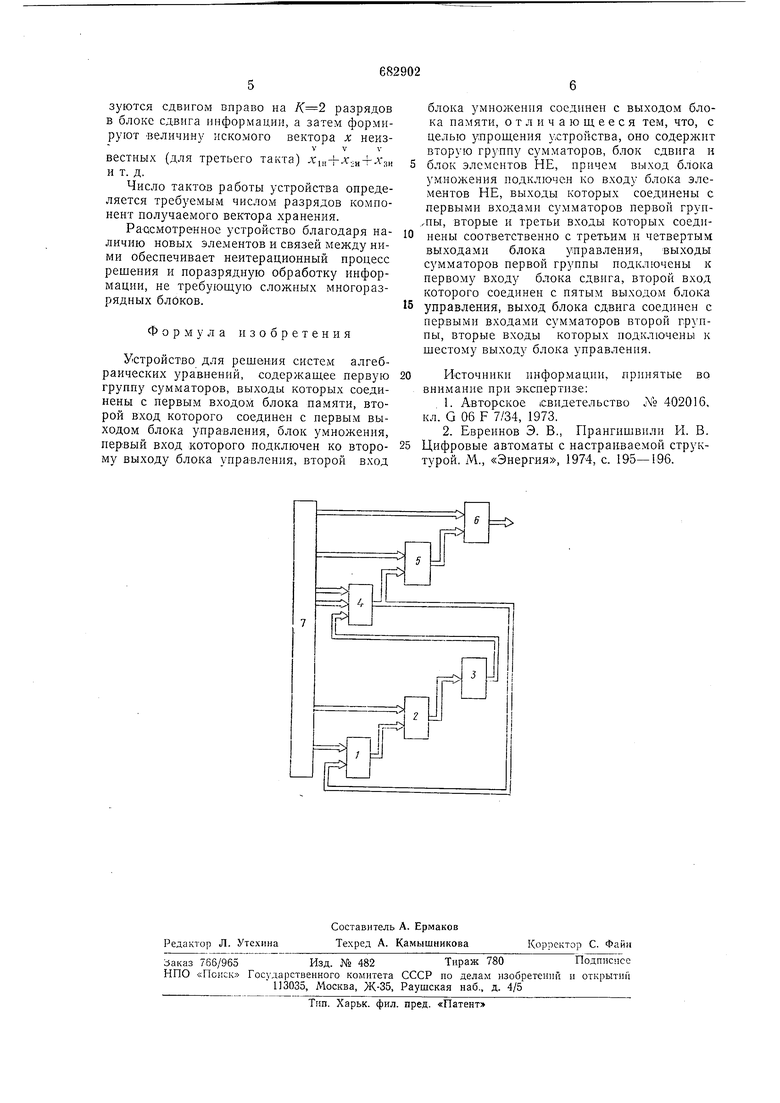

Устройство для решения систем алгебраических уравнений, содержаш,ее первую группу сумматоров, выходы которых соединены с первым входом блока памяти, второй вход которого соединен с первым выходом блока управления, блок умножения, первый вход которого подключен ко второму выходу блока управления, второй вход

блока умнол ения соединен с выходом блока памяти, о т л и ч а ю ш. е е с я тем, что, с целью упрощения устройства, оно содержит вторую группу сумматоров, блок сдвига н блок элементов НЕ, причем выход блока умножения подключен ко входу блока элементов НЕ, выходы которых соединены с первыми входами сумматоров первой группы, вторые и третьи входы которых соединены соответственно с третьим н четвертым выходами блока управления, выходы сумматоров первой группы подключены к первому входу блока сдвига, второй вход которого соединен с пятым выходом блока управления, выход блока сдвига соединен с первыми входами сумматоров второй группы, вторые входы которых подключены к шестому выходу блока управления.

Источники информации, принятые во внимание при экспертизе:

1.Авторское |Свидетельство № 402016, кл. G 06 F 7/34, 1973.

2.Евреинов Э. В., Прангишвилн И. В. Цифровые автоматы с настраиваемой структурой. М., «Энергия, 1974, с. 195-196.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Устройство для решения системы ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811276A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714407A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| ГЕНЕРАТОР СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2016 |

|

RU2615322C1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714406A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

Авторы

Даты

1979-08-30—Публикация

1977-04-08—Подача