(54) СТАБИЛИЗИРОВАННЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Формирователь импульсов управления | 1987 |

|

SU1522387A2 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797043C1 |

| МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ОБРАТНОГО ЦИКЛИЧЕСКОГО СДВИГА | 2014 |

|

RU2553071C1 |

| Троичный счетный триггер | 1979 |

|

SU864503A1 |

| RS-ТРИГГЕР | 2015 |

|

RU2604682C1 |

| Цифроаналоговый преобразователь | 1986 |

|

SU1361719A1 |

| Тактовый генератор | 1982 |

|

SU1187243A1 |

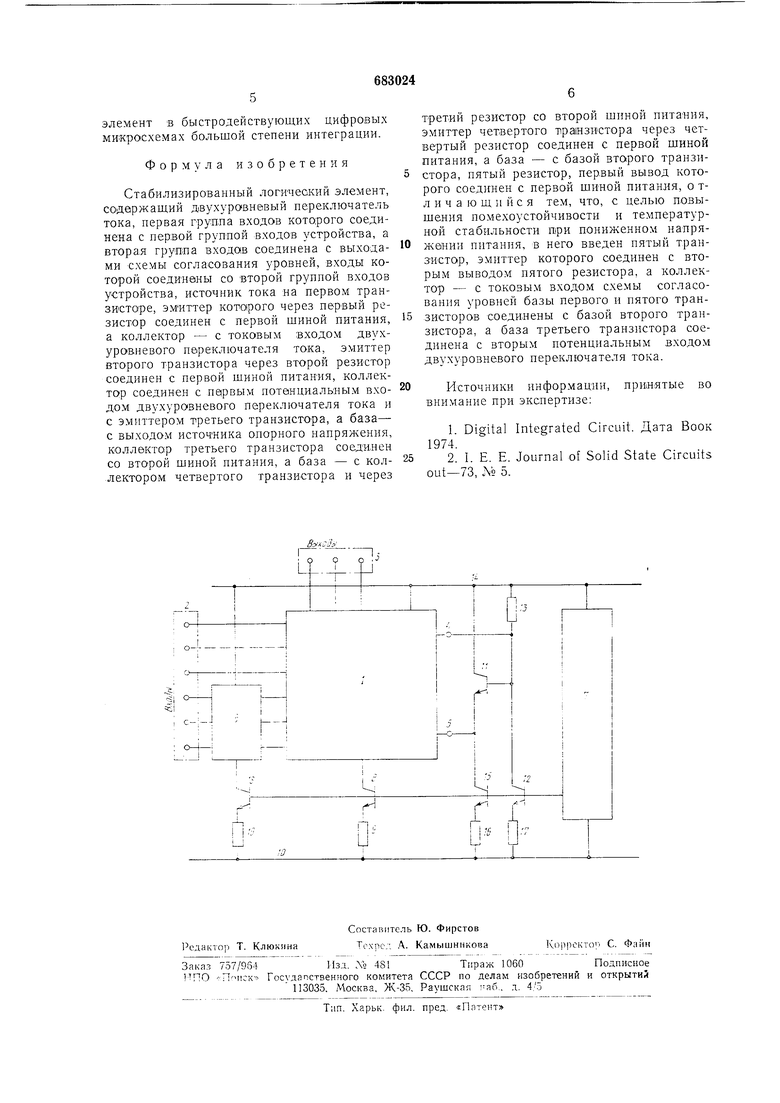

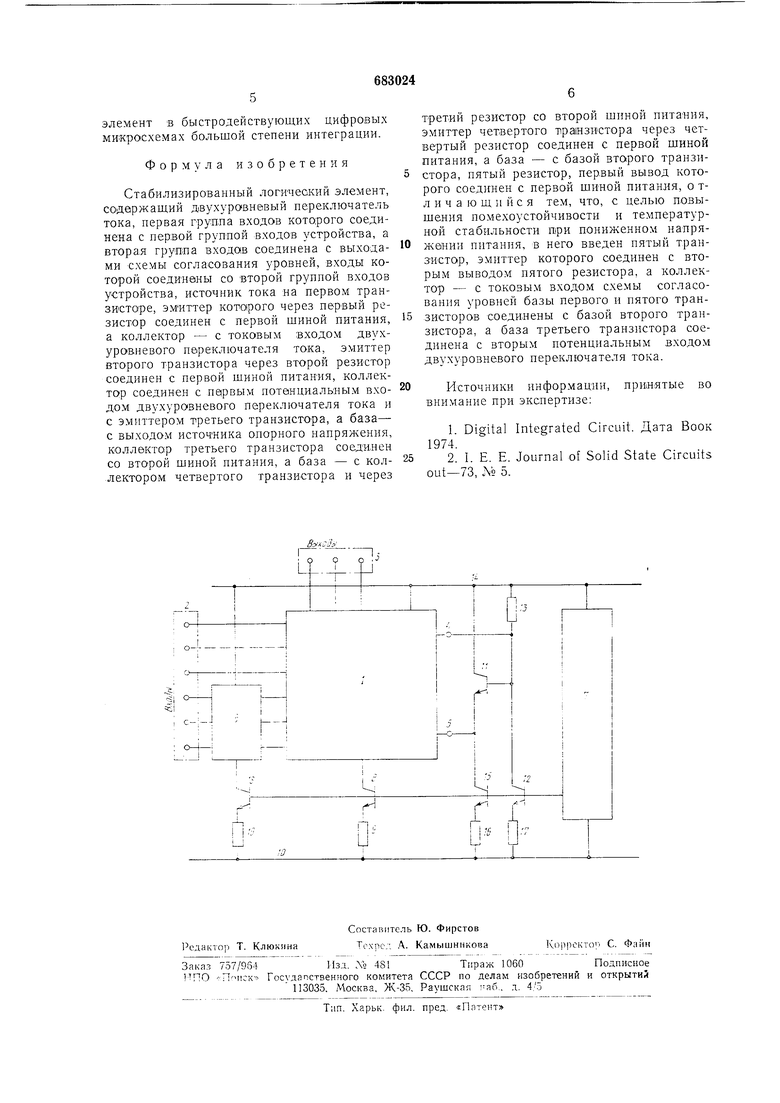

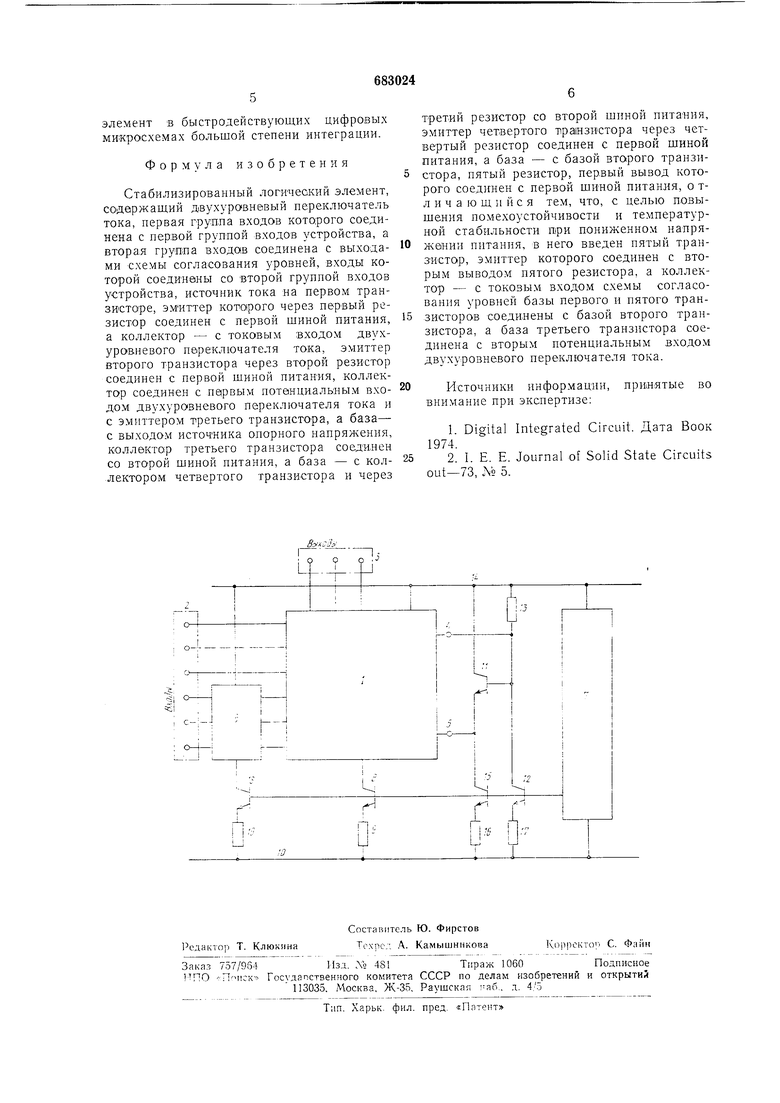

Изобретение относится к микроэлектронике и преднаэначено для использования тз быстродействующих цифровых микросхемах большой степени интегр.ации на нереключателях тока, работаюпхих с малым логическим перепадом при понижении напряжения питания. Известен логический элемент, состоящий из истачни КО:В рабочего тока, двухуровневого переключателя тока, схемы согласова-ния уровней, источника опорного напряжения, схемы передачи уровня опорного )1апряжения, содержащей первый транзистор, коллектор которого соединен с шмной положительного потенциала, база - с первым выходом источника опорного напряжения, эмиттер - с первым нотенциальным входом двухуровневого переключателя тока и с катодом первого диода, анод которого соединен с анодом второго диода, катод которого соединен со вторым потенциальным входом двух фовневого переключателя тока и с коллектором второго транзистора, база которого соединена со вторым выходом источника опорного напряжения, а эмиттер - с базой транзистора - источника тока двухуровневого переклю-.ателя и через первый резистор с шиной нулевого нотенциала 1. Однако этот элемент отличается больщой потребляемой мощностью вследствие значительной величины логического перепада и высокого, примерно 5 В, напряжения пнта1 ия, а также крайне низкой помехоустойчивостью при пониженном до 2-3 В напряжении питания и изменении темпераTyipbi, что не нозволяет использовать его в быстродейст-зующих цифровых микросхемах больщой степени интеграции. Наиболее близок к предложенному по технической сущности логический элемент с температурной компенсацией, содержащий переключатель тока с потенциальным и токовым входами, источник опорного напряжения, первую и вторую щины питания, рабочий ток В переключателе тока задается первым транзистором, коллектор которого соединен с токовым входом пе:рекл1очателя тока, эмиттер через первое со-противление подключен к первой тине питания, база и коллектор второго транзистора соединены вместе и соедиачены с первым выводом второго резистора и первым выводом третьего резистора, второй вывод третьего резистора соединен с базой третьего транзистора, эмиттер которого через четвертый резистор соединен с первой щиной питания, а коллектор через пятый резистор соединен с эмиттером четвертого тра;1зистора, коллектор четвертого транзистора соединен с базой пятого транзистора и через шестой резистор Соединен со ;второй шиной нитания, коллектор пятого транзистора соединен со второй шиной питания, а эмиттер соединен с потенциальным входом переключателя тока и с коллектором шестого транзистора, эмиттер шестого транзистора соедкнен -с базой лервого транзистора и со вторым выводом второго резистора, базы ineстого и четвертого транзисторов соединены с .выходом источника oHopiHoro напряжения, всоллектор третьего транзистора соединен с входом обратной связи источника onopHoio напряжения 2. Однако данное устройство )1меет недостаточно высокую ломехоустойчнвость и темнератур.ную стабильность при иоиижелном напряжении нитания. Кроме того, да.1ный логический элемент одноур01вневый. Целью изобретения является по:вышение помехоустойчивости и температурной стабильности логического многоуровиевого элемента при нониженном напряженни питания. Это достигается тем, что стабилизированиый логический элемент, содержаший двухуровневый переключатель тока, первая группа входов которого соединена с первой группой входов устройства, а вторая группа входов с выходами схемы согласования уровней, входы которой соединены со второй группой входов устроЙ Спва, источник тока на первом транзисторе, эмиттер которого через первый резистор соединен с первой шиной питания, а коллектор - с токовым входом двухуровневоло переключателя тока, эмиттер второго транзистора через второй резистор соедвнен с первой шиной питания, коллектор соединен -с первым потенциальны.м входом двухуровневого переключателя то.ка и с эмиттером третьего транзистора, коллектор которого соединен со второй шиной источника питания, а база - с выходом источника опорного напряжения, коллектор третьего транзистора соединен со второй шиной питания, а база-с коллектором четвертого транзистора и через третий резистор со второй шиной питания, эмиттер четвертого транзистора через четвертый резистор соединен с первой шиной питания, а база соедипена с ба3(ОЙ второго транзистора, пятый резистор, пер:вый вывод которого соединен с nepBoii шиной питания, дополнительно содержит пятый транзистор, эмиттер iKOTOporo соединен с вторым выводом пятого резистора, а коллектор - с токовым входом схемы согласования уровней, базы первого и пятого транзисторов соединены с базой щторого транзистора, а база третьего транзистора соединена с вторым потенциальным изходом двухуровневого переключателя тока, На чертеже приведена структурная схема стабилизированного логического элемента. Оп содержит двухуровневый переключатель / тока с логическими :входами 2 и выходами 3, нотенциальными входами 4 и 5 и схемой 6 согласования уровней, а также источник 7 опорного напряжения. Рабочий ток задается транзистором 8, коллектор которого соединен с токовькм входом переключателя / то.ка, а эмиттер через резистор 9 соединен с шиной 10 питания. Потенциальный вход 4 соединен с базой транзистора //, коллектором транзистора 12 и через резистор 13 с шиной 14 питания. Коллектор транзистора // также соединен с шиной М дитавия, а эмиттер подключен к потенциальному входу 5 и коллектору транзистора 15. Эмиттеры транзисторов 15 и 2 через резисторы 16 и /7 соедине 1ы с шиной 10 питания. Ток в схему согласования задается траагзистором 18, коллектор KOTOjJoro соединен с токовым входом схе,мы € согласования уровней, а эмиттер через резистор 19 соединен с шиной 10 питания. Базы транзисторов 8, 12, 15 и 18 объединены и подключены к источнику 7 опорного напряжения. Транзисторы 8 и 12, 15 и 18, резисторы 9 и 17, 16 и 19 изготавливаются (Одинакоазыми, Устройство работает следуюишм образом. При нодаче напряжения на шины питания через траизисторы 8, 12, 15 и 18 и резисторы 9, 16, 17 и 19 протекают токи. На резисторе 13 соз.дается иадение напряжения, равное половине логического иерепада, -которое подается на потенциальный вход 4 и через транзистор // на потенциальный вход 5 двухуровневого иереключателя / тока, В зависимости от комбинации логических сигналов на .входах 2 и конкретного вида двухуровневого переключателя / тока на выходах 3 )тся нужные выходные сигналы, Измене)ше напряжения питания и температуры приводит к одина-ковым изменениям токон через транзисторы 8 и 12, 15 и 18. В результате паденпе напряжения, снимаемое с резистора 13 и подаваемое на потенциальные входы 4 и 5, остается половине логического перепада, обеспечивая работоспособность ло.гичеокого элемента. Стабилизированный низкоуровневый логический элемент ра ботоопособен в широком температурном диапазоне от -30 до + 85° С ири напряжении питания ра.вном 3,0.(3±5%. Нри логическом перепаде , 0,42 5, помехоустойчивость равна -if/,,40,H5, Нредложениый элемент потребляет iB 2,5 раза ,меньшую мощность, имеет в 1,5 раза большее быстродействие по сравнению с серийно выпускаемыми схемами ЭС/1. Такие характеристики позволяют пспо;1ьзовать предложеннь й .inniur-.-tTifi

элемент в быстродействующих цифровых микросхемах большой степени интеграции.

Формула изобретения

Стабилизированный логический элемент, содержащий двухуро-внавый переключатель тока, первая группа входов которого соединена с первой группой входов устройства, а вторая группа входов соединена с выходами схемы согласования уровней, входы которой соединены со второй группой входов устройства, источник тока на первом транзисторе, эмиттер которого через первый резистор соединен с первой щиной питания, а коллектор - с токовым входом двухуровневого переключателя тока, эмиттер второго транзистора через второй резистор соединен с первой щиной питания, коллектор соединен с первым потенциальным входом двухуровневого переключателя тока и с эмиттером третьего транзистора, а база- с выходом источника опорного напряжения, коллекто1р третьего транзистора соединен со второй шиной питания, а база - с коллектором четвертого транзистора и через

третий резистор со второй шпной , эмиттер четвертого транзистора через четвертый резистор соединен с первой шиной питания, а база - с базой второго транзистора, пятый резистор, первый вывод которого соединен с первой шиной питания, о тл и ч а ю щ и и с я тем, что, с целью повышения помехоустойчивости и температурной стабильности nipH пониженном напряжании питания, в него введен пятый транзистор, эмиттер которого соединен с вторым выводом пятого резистора, а коллектор - с токовым входом схемы согласования уровней базы первого и пятого транзисторов соединены с базой второго транзистора, а база третьего транзистора соединена с вторым потенциальным входом двухуровневого переключателя тока.

Источники информации, принятые во

внимание при экспертизе:

Авторы

Даты

1979-08-30—Публикация

1977-03-03—Подача