I

Иэс ретенив относигся к области запоминающих устройств.

Известно запоминающее усгройсгво с исправлением ошибок, содержащее регистр числа, блок контроля, основной блок памяти, дополнительный блок памяти и аеишфpaTOp lj. В этом устройстве осуществляется исправление одиночных ошибок при считывании путем сравнения контрольной информации по Хеммингу, считанной из дополнительного блока памяти одновременно со считыванием числа из основного блока памяти, с контрольной информацией по Хеммингу, сформвфованной блоком контроля, дальнейшей дешифрацией результата сравнения и корректированием числа в регистре числапо результату дешифрации.Недостатком этого устройства яышетcHi-cHnbHoe увеличение количества оборудо- вания за счет блока кронтроля, а также увеличение времени обращения за счет формирования контрольной информации по Хеммингу.

Наиболее близким техническим решением к данному изобретению является запоминающее устройство с исправлением ошнбок, содержащее основной и дополнительный неисопнтелв, блок выборки адресов, деигафратор, блок контроля и регистр числа, выполненный на триггерах со счетными входами, причем выход блока выборки адресов соединен со входами накопителей, входы блока контроля и одни из информационных входов регистра числа подключены к выходам основного накопителя, первый выход блока контроля соединен с управляющим входом регистра числа 2.

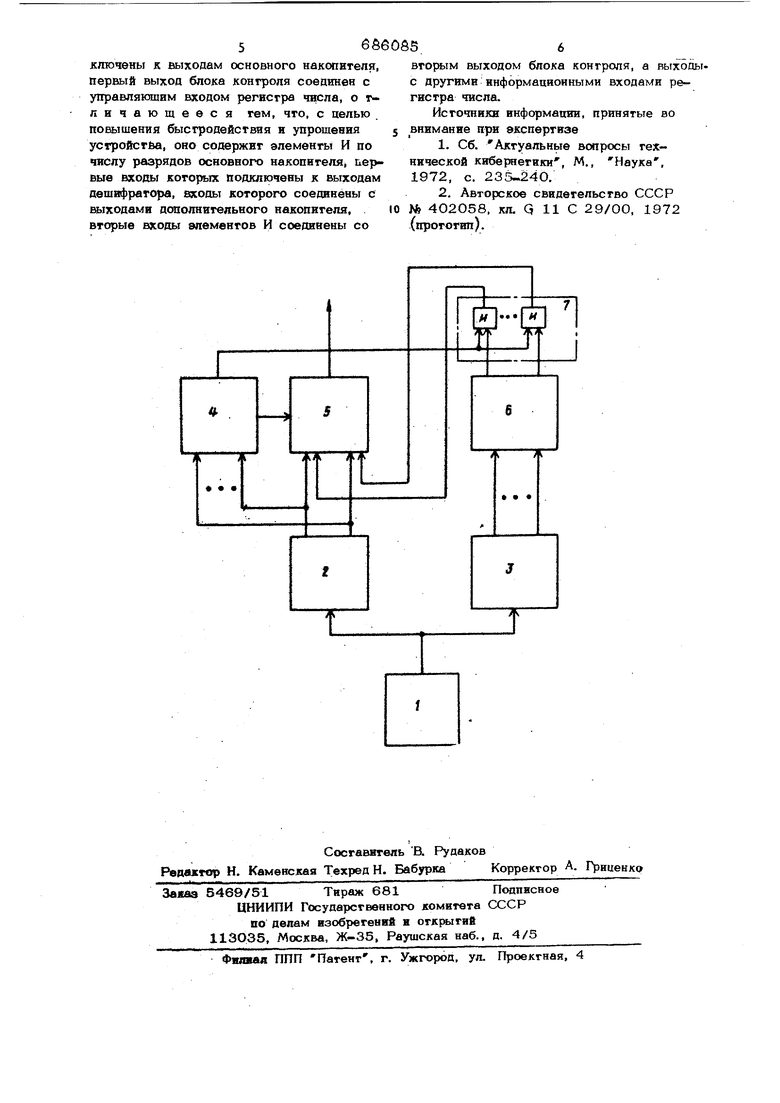

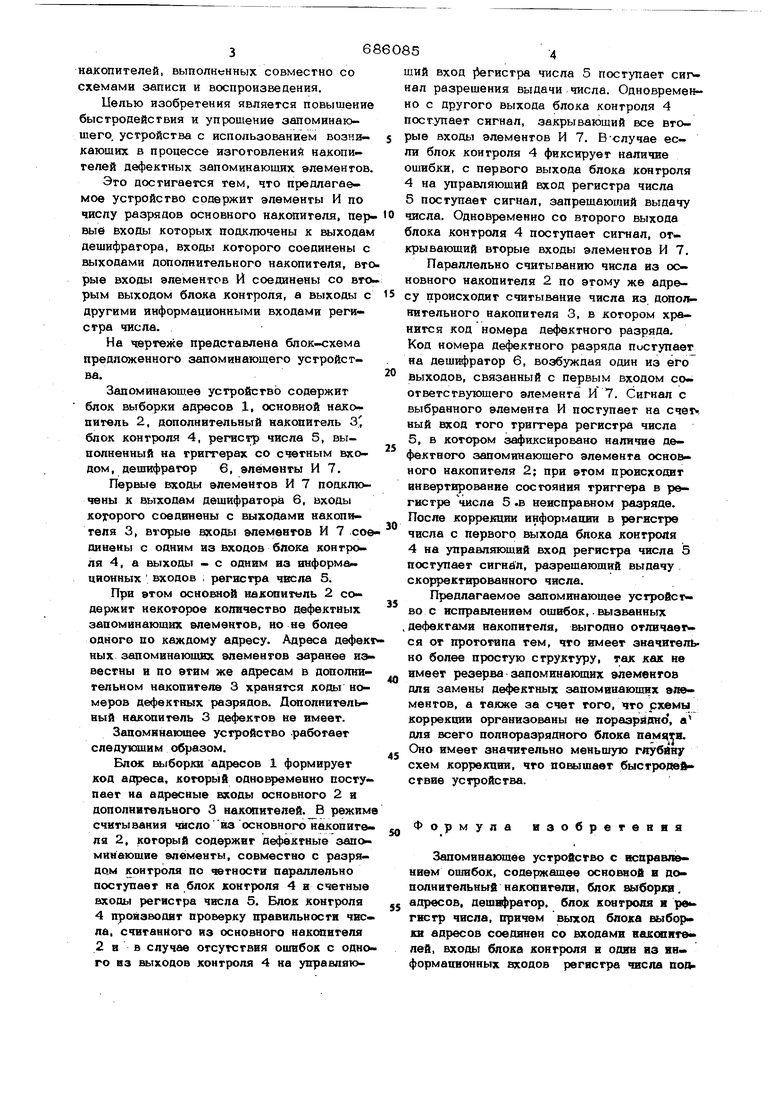

Недостатком этого запоминающего yci ройства является сильное увеличение количества оборудования за счет сложного блока контроля, за счет организации резерва зиюмннающих элементов для замены ими дефектных запоминающих влементоь, а также при организаЬин полноразряоп ного запоминающего устройства из одно- разрядных накопителей. Другим недостатком является невозможность использования накопителей, выполненных совместно со схемами записи и воспроизведения. Целью изобретения является повышение быстродействия и упрощение запоминаюшего. устройства с использованием возникаюших в процессе изготовлений накопителей дефектных запоминающих элементов. Это достигается тем, что предлагаемое устройство содержит элементы И по числу разрядов основного накопителя, первые вхощ, которых подключены к а.гходам дешифратора, входы которого соединены с выходами дополнительного накопителя, вто рые входы элементов И соединены со вто рым выходом блока контроля, а выходы с другими информационными входами регистра числа. На чертеже представлена блок-схема предложенного запоминающего устройства. Запоминающее устройство содержит блок выборки адресов 1, основной накопитель 2, дополнительный накопитель 3 блок контроля 4, регистр числа 5, выполненный на триггерах со счетным входом, дешифратор 6, элементы И 7. Первые входы элементов И 7 подключены к выходам дешифратора 6, входы KOj4)poro соединены с выходами накопнтеля 3, вторые входы элементов И 7 сое динены с одним из входов блока контроля 4, а выходы - с одним из информационных входов , регистра часла 5. При этом основной наксйзитиль 2 содержит некоторое количество дефектных запоминающих влементов, но не более одного по каждому адресу. Адреса дефек ных запоминающих элементов заранее известны и по этим же адресам в дополнительном накопителе 3 хранятся коды номеров дефектных разрядов. Дополнительный накопитель 3 дефектов не имеет. Запомннаклвее устройство .работает следующим образом. Блок ш 1борки адресов 1 формирует код адреса, который одновременно поступает на адресные входы основного 2 и дополнительного 3 накси1ителей. В режим считывания число йэ основного накопителя 2, который содержат дефектные запоминающие элементы, совместно с разрядом контроля по «ютности параллельно поступает на блок контроля 4 н счетные вхо{ш регистра числа 5. Блок контроля 4 производит проверку правильности числа, считанного из основного накопителя 2 ив случае отсутствия ошибок с одно го вз ш 1хоаов контроля 4 на управляюший вход у егистра числа 5 поступает сипнал разрешения выдачи числа. Одновременно с другого выхода блока контроля 4 поступает сигнал, закрывающий все вторые входьт элементов И 7. В-случае если блок контроля 4 фиксирует наличие ошибки, с первого выхода блока контроля 4на управляющий вход регистра числа 5поступает сигнал, запрещающий выдачу числа. Одновременно со второго выхода лока контроля 4 поступает сигнал, отрывающий вторые входы элементов И 7. Параллельно считыванию числа из осовного накопителя 2 по этому же адреу происходит считывание числа из дополнительного накопителя 3, в котором хранится код номера дефектного разряда. Код номера дефектного разряда пиступает на дешифратор 6, возбуждая один из его выходов, связанный с первым входом соответствующего элемента И 7. Сигнал с выбранного элемента И поступает на счетч ный вход того триггера регистра числа 5, в котором зафиксировано наличие дефектного запоминающего элемента основного накопителя 2; при этом происходит инвертирование состояаия триггера в регистре числа 5 .в неисправном разряде. После ко фекции информаони в регистре числа с первого выхода блока контроля 4 на управляющий вход регистра числа 5 поступает сигнйл, разрешающий выдачу скорректированного числа. Предлагаемое запоминающее устройство с исправлением ошибок, клзванных дефектами накопителя, выгодно отличает ся от прототипа тем, что имеет значительно более простую структуру, так как не имеет резерва запоминакшшх элементов для замены дефектных запоминающих эпементов, а также за счет того, что схемы коррекгога организованы не поразрядно , а для всего полноразрядного блока памятв. Оно имеет значительно меньшую глубину схем коррекции, что повышает быстродействие устройства. и а о б р е тения мула Запоминающее устройство с исправлением ошибок, содержащее основной и дополнительный накопители, блок выборка. адресов, дешвфратор, блок контроля и ре гнстр числа, причем выход блока выборки адресов соединен со Входами наеоакте лей, входы блока контроля н один из нн формационных входов регистра числе noi кяючены к выходам основного накстгителя, первый выход блока конгроля соединен с управляющим входом регистра числа, о гличающееся гем, что, с целью повышения быстродействия и упрощения усгройсгба, оно содержвг элементы И по числу разрядов основного накопителя, первые входы которых подключены к выходам дешифратора, входы которого соединены с выходами дополнительного накопителя. вторые входы элементов И соединены со ese s.6 вторым выходом блока конгроля, а выходыс другими информационными входами регистра числа. Источники информации, принятые во внимание при экспертизе 1.Сб. Актуальные вопросы технической кибернетики , М., Наука, 1972, с. 235-.240. 2.Авторское свидетельство СССР № 402О58, кл. q 11 С 29/00, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с контролем и коррекцией информации | 1983 |

|

SU1109809A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

Авторы

Даты

1979-09-15—Публикация

1978-04-13—Подача