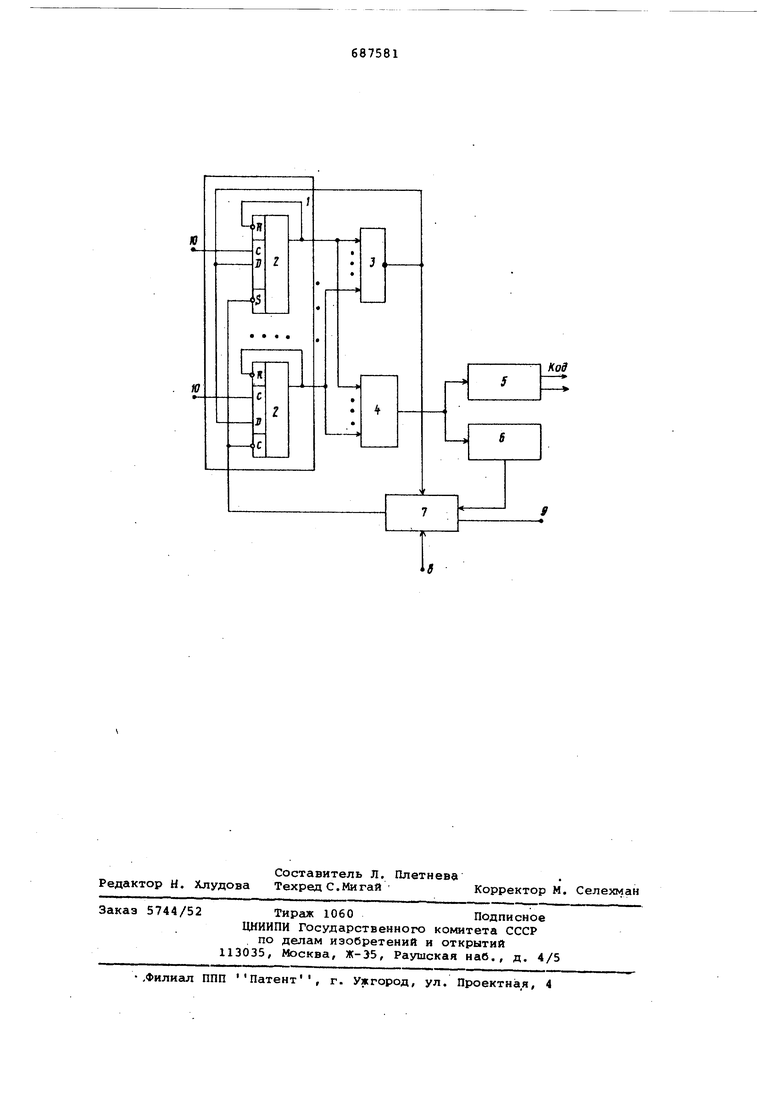

Изобретение относится к области ядерной спектрометрии и может быть использовано в многомерных анализаторах при статистическом анализе угловых распределений, а также при из-мерении интенсивности излучений во многих точках пространства с помощью многих детекторов. Известно устройство, которое содержит входные К.ЛЮЧИ, стробируемые внешним сигналом, регистр, выполненный на R-S триггерах, устройство исключения совпадений, кодирующее устройство и логический блок 1. В этом устройстве сигналы на вход регистра поступают только при наличи стробирующего импульса. Благодаря этому при уменьшении длительности входного импульса можно получить вы сокое временное разрешение. Однако реализовать это разрешение практичес ки оказывается невозможным вследствие того, что при уменьшении длитель ности стробируемого импульса уменьшается вероятность регистрации входного импульса, что приводит к увеличению числа просчетов, т,е, к снижению эффективности использования многовходового кодирующего устройства. Недостатком устройства являются определенные требования к длительности входных импульсов, которая должна быть минимальна для уменьшения вероятности совпадений и для исключения многократной регистрации одного и того же события, в то же время должна быть достаточно большой для уменьшения числа просчетов. Наиболее -близким к предлагаемому является устройство, содержащее блок кодирования, представляющий собой К-координатную матрицу,в узлах которой расположены Датчики, адресный регистр, вход каждого триггера которого подключен к соответствующей шине соответствующей координаты, а выход каждого триггера соединяется с одним из входов схемы ИЛИ, с одним из входов дифференциального дискриминатора, Функция которого заключается в обеспечении «1 на выходе при появ- . ленйи Ч только на одном из его входов и с одним из входов шифратора, исключая первый триггер, и логического блока 2. Одним из недостатков этого устройства является большое время резрешения, определяемое быстродействием элементов К-координатной матрицы. триггеров, регистров, схем ИЛИ, а также триггеров и схемы И логического блока (блока управления). Другим- недостатком известного уст ройства является требования к длител ности входных импульсов, невыполнени которых влечет к ошибкам преобразова ния . Входные импульсы устройства снижаются с выходов дискриминаторов амп литуды, поэтому их длительность может меняться в весьма широких пределах. Для того, чтобы избежать многократного кодирования импульса с одного и того же детектора, необходимо чтобы их длительность была меньше времени преобразования устройства. Таким образом, для нормальной работы устройства входные импульсы должны быть предварительно сформированы по длительности, что требует применения значительного числа формирователей (по числу входов), которые, требуя определенного времени восстановления ввиду статического характера поступающей на них информации будут выдавать часть импульсов дефектной дли тельности, которые затем будут отбро шены при кодировании. При этом параметры статического процесса исказятс Таким образом, необходимость использования входных импульсов стандартной длительности существенно усложняет работу с устройством и снижает точность производимых с устройством экспериментов. Целью изобретения является повышение быстродействия и точности преобразования, которое непосредственно выражается в уменьшении времени разрешения и снижении требований к ддительности входных импульсов. Это достигается тем, что в устройство, содержащее регистр, блок ко дирования, шифратор, выходы которого являются выходами преобразователя, блок вьщеления совпадений, выход которого соединен с первым входом блока управления, первый выход которого соединен с шиной готовности информации, второй выход блока управления подключен к первому входу регистра, введен многовходовый элемент И-НЕ, причем выход многовходового элемента И-НЕ подключен к вторым вхо дам блока управления и регистра, выходЦ которого соединены с соответствующими входами многовходового элемента И-НЕ и блока кодирования, выход блока кодирования подключен к входам шифратора и блока выделения совпадений, и кроме того,, регистр выполнен на -В- триггерах, причем R вход каждого триггера соединен с его выходом и с выходом регистра, С вход триггера подключен к соответствующей информационной входной шине регистра S входы всех триггеров объединены и подключены к первой входной шине регистра, а D входы всех триггеров соединены с второй входной шиной регистра. На чертеже представлена структурная схема предлагаемого устройства, Оно содержит регистр 1, выполненный на D триггерах 2, Выход каждого из триггеров соединен с входом (R) установки О того же триггера 2, одним из входов многовходового элемента И-НЕ 3 и соответствующим входом блока кодирования, который представляет собой К-координатную матрицу 4, выходы которого соединены с входами шифратора 5 и с входами блока 6 выделения совпадений, выход которого соединен с одним из входов бло-ка 7 управления, к одному из входов которого подключена шина 8 сброса, первый из выходов блока управления соединен с шиной 9 готовности информации, а второй его выход соединен с входами (S) установки в триггеров регистра. Выход многовходового элемента И-НЕ соединен с вторым входом блока управления и с вxoдa Ф D триггеров, С входы которых соединены с входными информационными шинами 10 регистра. Выход шифратора является выходом всего устройства. Устройство работает следующим образом. . Перед началом работы на шину 8 поступает сигнал сброса, устанавливающий триггеры 2 в состояние . При этом на выходе многовходового элемента И-НЕ 3 устанавливается лопоступающий на входы гический D триггеров 2, При появлении входного сигнала с одной из шин 10, соответствующий триггер 2 переводит в состояние О которое фиксируется на его входе R. На выходе многовходового элемента И-НЕ 3 при этом устанавливается логическая , которая поступает на входы D триггеров 2. Если теперь входные импульсы поступят по другим шинам 10, ни один из триггеров 2 своего состояния не изменит. Если же первым входным импульсом, уже зафиксированным соответствующим триггером 2, по той же шине 10 придет следующий импульс, срабатывающий триггер 2, несмотря на то, что на его входе установилась логическая , останется в состоянии О благодаря связи с его выхода на его вход R. Возможен также случай, когда первый пришедший по шине 10 импульс окажется настолько малой длительности, что переключения триггера 2 не произойдет. И в этом случае в схеме не произойдет ложных переключений и другие триггеры 2 регистра 1 останутся в разблокированном состоянии. С выхода триггеров 2 регистра 1 информации через блок кодирования (Ккоординатную кодирующую матрицу 4) поступает на вход шифратора 5, формирующего код номера входа, зарегист рировавшего импульс, и на вход блока 6 вьщеления совпадений. Если вход ная информация зарегистрирована толь ко одним из триггеров 2, то на выходе блока 6 вьщеления совпадений образуется сигнал, поступающий на один из входов блока 7 управления, котору совместно с сигналом, поступающим с выхода многовходового элемента И-НЕ 3 на другой вход блока 7 управления, определяет готовность устройства к вьадаче кода и выдает сигнал на шину 9 готовности. При регистрации триггерами 2 регистра 1 нескольких импульсов, информации о наличии совпадений выдается блок б вьщеления совпадений и передается в блок 7 управления, который в этом случае не выдает сигнала готовности на шину 9 и устанавливает триггеры 2 регистра в исходное состояние После считывания внешним устройст вом кода с выхода шифратора 5 на шин сброса 8 поступает внешний импульс, Г1О которому блок 7 управления вновь приводит триггеры 2 в исходное состо ние . Поскольку длительность входных импульсов может оказаться значительно больше времени регистрации, после считывания кода внешним устройством на шине 10, код которой уже передан, сигнал может сохранится. Если теперь информация поступит по другой входной шине 10, то совпадение этих импульсов зарегистрирован не будет, и устройство зарегистрирует только новый импульс, поскольку триггеры 2 переключатся по фронтам входных сигналов. Использование предлагаемого преобразователя номера датчика в цифровой код при проведении физических экспериментов, в частности, при изме рении интенсивности излучений во мно гих точках пространства с помощью многих детекторов, позволяет в сравнении с известным устройством работать с импульсами любой длительности уменьшив тем самым искажения статистических параметров исследуемого про цесса и уменьшив стоимость измерений поскольку для разрабатываемых в настоящее время устройств кодирования, имеющих 32-128 входов, потребовалось бы такое же количество формирователей . Кроме того, поедлагаемое устройст во имеет существенно меньшее разреша щее время по сравнению с устройством выбранным за прототип,. Так, например, если признать, что кодирукадая матрица и триггеры регистра содержат по два последовательно включенных логических элемента, разрешающее время устройства, выбранного за прототип- составляет Тр - 12 tn,где tn - время переключения одного логического элемента, тогда для предлагаемого устройства Тр - 3tne Четырехкратное уменьшение времени разрешения позволяет существенно повысить суммарную входную загрузку, что в конечном итоге приведет к уменьшению общего числа устройств кодирования, требующихся для проведения эксперимента. Формула изобретения 1, Преобразователь номера датчика в цифровой код, содержащий регистр, блок кодирования, шифратор, выходы которого являются вЕлходами преобразователя, блок вьщеления совпадений, выход которого соединен с первнлм входом блока управления, первый выход которого соединен с шиной готовности информации, второй выход блока управления подключен к первому входу регистра, отличающийся тем, что,- с целью повышения быстродействия и точности преобразования, в него введен многовходовый элемент И-НЕ, причем выход многовходового элемента И-НЕ подключен к вторым входам блока управления и регистра, выходы которого соединены с соответствующими входами многовходового элемента И-НЕ и блока кодирования, выход блока кодирования подключен к входам шифратора и блока вьвделения совпадений, 2. Преобразователь по п. 1, от личаюшийся тем, что регистр выполнен на D-триггерах, причем R вход каждого триггера соединен с его выходом и с выходом регистра, С вход триггера подключен к соответствующей информационной входной шине регистра, S входы всех триггеров объединены и подключены к первой входной шине регистра, а D входы всех триггеров соединены с второй входной шиной регистра. Источники информации, принятые во внимание при экспертизе 1.Басиладзе С.Г., Гузик 3. Предприят. ОИЯИ, Р13-7492 Дубна, 1973. 2.Авторское свидетельство СССР № 433632, кл. Н 03 К 13/02, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь номера датчика в цифровой код | 1984 |

|

SU1164888A1 |

| Многоканальное спектрометрическое устройство | 1979 |

|

SU864170A1 |

| Буферное запоминающее устройство | 1980 |

|

SU920834A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Шифратор команд | 1973 |

|

SU467466A1 |

| Шифратор позиционного кода | 1989 |

|

SU1642588A1 |

| Устройство для автоматического поиска неисправностей | 1972 |

|

SU467331A1 |

| Устройство для приема и передачииНфОРМАции | 1978 |

|

SU809293A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Устройство для импульсного регулирования мощности в @ -фазной сети без нейтрали и схема управления вентилями устройства для импульсного регулирования мощности в @ -фазной сети без нейтрали | 1983 |

|

SU1120467A1 |

Авторы

Даты

1979-09-25—Публикация

1977-07-04—Подача