(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Буферное запоминающее устройство | 1977 |

|

SU733017A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Генератор псевдослучайных чисел | 1976 |

|

SU693408A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Устройство для ввода информации | 1979 |

|

SU911500A2 |

1

Изобретение относится к вычислительной технике, в частности может быть использовано для совместной работы с быстродействующими аналого-цифровыми преобразователями для измерения однократных и редкоповторяющихся процессов.,

Известно буферное запоминающее устройство (БЗУ), содержащее регистры, в которых потенциальные однотактньге триггеры соединены через схемы совпадения, коммутатор, входной регистр, прямые и инверсные входы которого попарно соединены со схемами совпадения, подключенными к разделительным входам триггеров, образующих первую числовую линейку. Коммутатор представляет собой сдвиговый кольцевой регистр, каждый разрядный выход которого соединен со вторыми схемами совпадения. Триггер, генератор и логические схемы образуют устройство привода. Устройство обладает высоким быстродействием, поскольку работа всех элементов схемы происходит синхронно 1.

Однако такое устройство требует больщих затрат оборудования, поэтому может быть использовано только в случае, когда объем хранимой информации невелик.

Наиболее близким к предлагаемому техническим решением является БЗУ, содержащее накопитель, адресные входы которого соединены с выходами дешифратора, входы которого подключены к соответствующим выходам адресного счетчика. Вход адресного счетчика соединен с выходом блока управления. Информационные входы накопителя соединены с выходами входного регистра, входы которого соединены с вход Q ными шинами устройства. Выходные шины накопителя соединены со входами выходного регистра, выходы которого соединены с выходными щинами устройства. Объем памяти такого устройства может быть достаточно больщим, поскольку в качестве запоминающих элементов могут быть использованы интегральные ЗУ большой емкости 2.

Недостатком такого устройства является низкая надежность вследствии того, что после окончания записи под влиянием внеш ° них дестабилизирующих факторов информация, хранящаяся в БЗУ, может быть искажена.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее накопитель, адресные входы которого подключены к выходам дещифратора, информационные входы - к одним выходам входного регистра, а выходы накопителя подключены к информационным входам выходного регистра, управляющий вход которого подключен к соответствующему выходу блока управления, адресный счетчик, выходы которого подключены ко входам дешифратора, а вход - к соответствующему выходу блока управления, входы входного регистра являются входами устройства, дополнительно введены сумматоры, первые входы которых подключены к выходам накопителя, вторые входы - к выходам выходного регистра, а выходы сумматоров являются выходами устройства, и элементы И-ИЛИ-НЕ, одни входы которых подключены к одним выходам входного регистра, другие входы - к другим выходам входного регистра, а выходы элементов И-ИЛИ-НЕ подключены к другим входам входного регистра, управляющие входы элементов И-ИЛИ-НЕ подключены к соответствующим выходам блока управления.

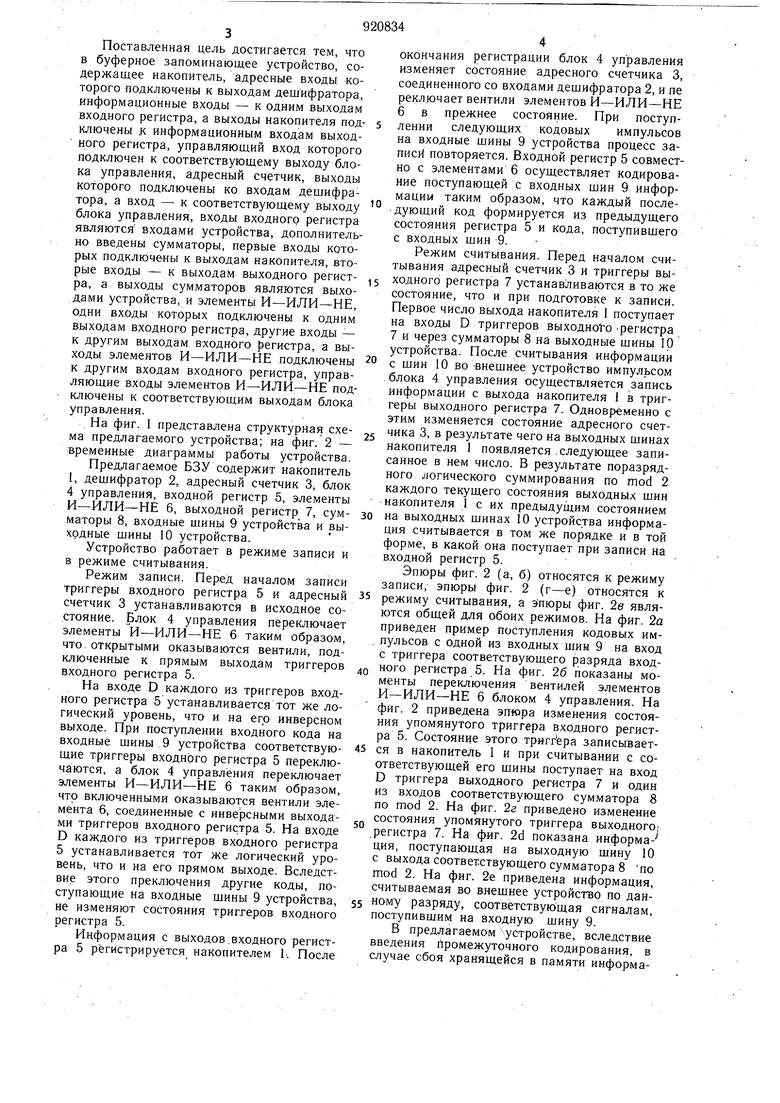

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы устройства.

Предлагаемое БЗУ содержит накопитель 1, дешифратор 2, адресный счетчик 3, блок

4управления, входной регистр 5, элементы И-ИЛИ-НЕ 6, выходной регистр 7, сумматоры 8, входные щины 9 устройства и выходные щины 10 устройства.

Устройство работает в режиме записи и в режиме считывания.

Режим записи. Перед началом записи триггеры входного регистра 5 и адресный счетчик 3 устанавливаются в исходное состояние. Блок 4 управления переключает элементы И-ИЛИ-НЕ 6 таким образом, что, открытыми оказываются вентили, подключенные к прямым выходам триггеров входного регистра 5.

На входе D каждого из триггеров входного регистра 5 устанавливается тот же логический уровень, что и на его инверсном выходе. При поступлении входного кода на входные шины 9 устройства соответствующие триггеры входного регистра 5 переключаются, а блок 4 управления переключает элементы И-ИЛИ-НЕ 6 таким образом, что включенными оказываются вентили элемента 6, соединенные с инверсными выходами триггеров входного регистра 5. На входе D каждого из триггеров входного регистра

5устанавливается тот же логический уровень, что и на его прямом выходе. Вследствие этого преключения другие коды, поступающие на входные щины 9 устройства, не изменяют состояния триггеров входного регистра 5.

Информация с выходов.входного регистра 5 регистрируется накопителем 1. После

окончания регистрации блок 4 управления изменяет состояние адресного счетчика 3, соединенного со входами дешифратора 2, и пе реключает вентили элементов И-ИЛИ-НЕ

6в прежнее состояние. При поступлении следующих кодовых импульсов на входные щины 9 устройства процесс записи повторяется. Входной регистр 5 совместно с элементами 6 осуществляет кодирование поступающей с входных шин 9 информации таким образом, что каждый последующий код формируется из предыдущего состояния регистра 5 и кода, поступивщего с входных шин -9.

Режим считывания. Перед началом считывания адресный счетчик 3 и триггеры выходного регистра 7 устанавливаются в то же состояние, что и при подготовке к записи. Первое число выхода накопителя 1 поступает на входы D триггеров выходно о регистра

7и через сумматоры 8 на выходные щины 10 устройства. После считывания информации с шин 10 во -внешнее устройство импульсом блока 4 управления осуществляется запись информации с выхода накопителя 1 в триггеры выходного регистра 7. Одновременно с этим изменяется состояние адресного счетчика 3, в результате чего на выходных шинах накопителя 1 появляется .следующее записанное в нем число. В результате поразрядного логического суммирования по mod 2 каждого текущего состояния выходных щин накопителя 1 с их предыдущим состоянием на выходных шинах 10 устройства информация считывается в том же порядке и в той форме, в какой она поступает при записи на входной регистр 5.

Эпюры фиг. 2 (а, б) относятся к режиму записи, эпюры фиг. 2 (г-е) относятся к режиму считывания, а эпюры фиг. 2в являются общей для обоих режимов. На фиг. 2а приведен пример поступления кодовых импульсов с одной из входных щин 9 на вход с триггера соответствующего разряда входного регистра 5. На фиг. 26 показаны моменты переключения вентилей элементов И ИЛИ-НЕ 6 блоком 4 управления. На фиг. 2 приведена эпюра изменения состояния упомянутого триггера входного регистра 5. Состояние этого трнггера записывается в накопитель 1 и при считывании с соответствующей его щины поступает на вход D триггера выходного регистра 7 и один из входов соответствующего сумматора 8 по mod 2. На фиг. 2г приведено изменение состояния упомянутого триггера выходного/ регистра 7. На фиг. 2d показана информация, поступающая на выходную шину 10 с выхода соответствующего сумматора 8 по mod 2. На фиг. 2е приведена информация, считываемая во внешнее устройство по данному разряду, соответствующая сигналам, поступивщим на входную щину 9.

В предлагаемом устройстве, вследствие введения йромежуточного кодирования, в случае сбоя хранящейся в памяти информации под влиянием внешних достабилирующих факторов при считывании, каждому искаженному числу соответствует другое искаженное число с отклонением в .том же разряде. ,,

При использовании m БЗУ данного типа, последовательно управляемых одним блоком управления, искаженные числа отстоят друг от друга на расстоянии, т, что позволяет не только отличить искаженную информаци1р, но и, используя методы корреляционного анализа, восстановить истинную картину записанного процесса. Кроме того, время регистрации информации в этом случае также уменьшается в m раз.

Формула изобретения

Буферное запоминающее устройство, сод1ержаш.ее накопитель, адресные входы которого подключены к выходам дешифратора, информационные входы - к одним выходам входного регистра, а выходы н копителя подключены к информационным входам выходного регистра, управляющий вход которого подключен к соответствующему выходу блока управления, адресный счетчик, выходы которого подключены ко входам дешифратора, а вход - к соответствующему выходу блока управления, входы входного регистра являются входами устройства, отличающееся тем что, с целью повышения надежности устройства, оно содержит сумматоры, первые входы которых подключены к выходам накопителя, вторые входы - к выходам выходного регистра, а выходы сумматоров являются выходами устройства, и элементы И-ИЛИ-НЕ, одни входы которых подключены к одним выходам входного регистра, другие входы - к другим выходам входного регистра,. а выходы элементов И-ИЛИ-НЕ подключены к другим входам входного регистра, управляющие входы элементов И-ИЛИ-НЕ подключены к соответствующим выходам блока управления.

Источники информации, приняты во внимание при экспертизе

1- Авторское свидетельство СССР № 411652, кл. Н 03 К 15/00, 1974.

/71 III

II

rjLJl JlJLJLJLJl Jl JLJLJl flJLJLJLJL

i-JLJLJLJL

JLJl

JI

П

JLJL

г

Авторы

Даты

1982-04-15—Публикация

1980-07-15—Подача