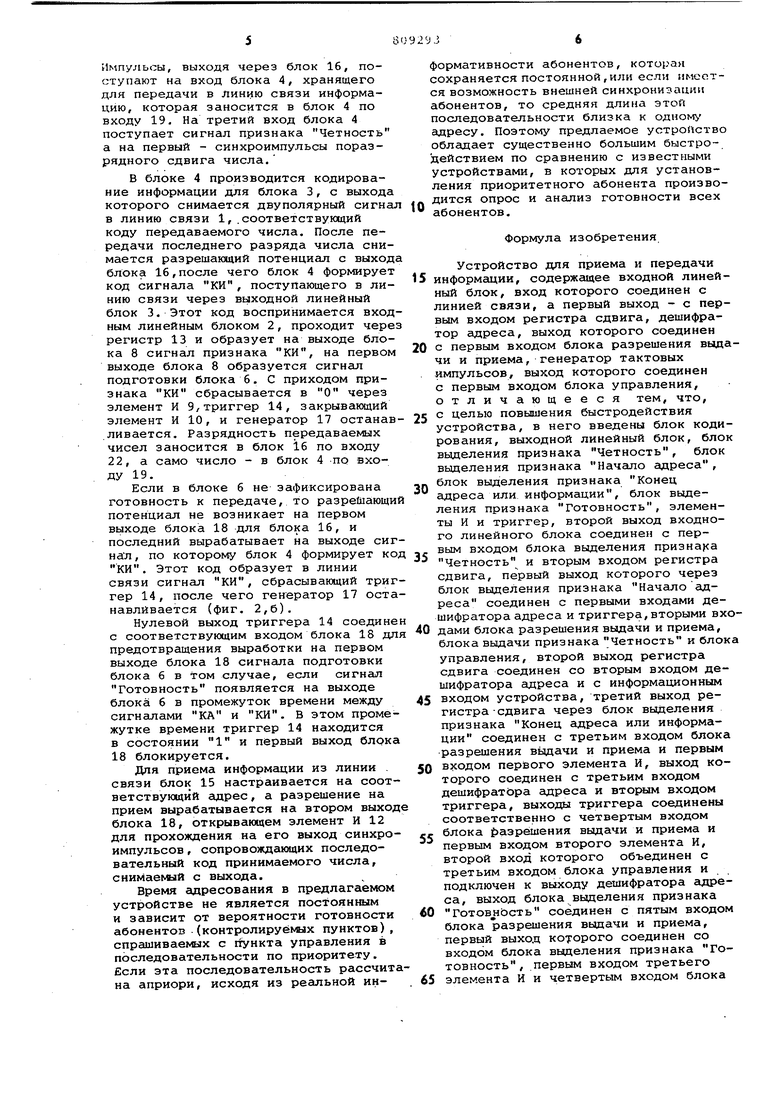

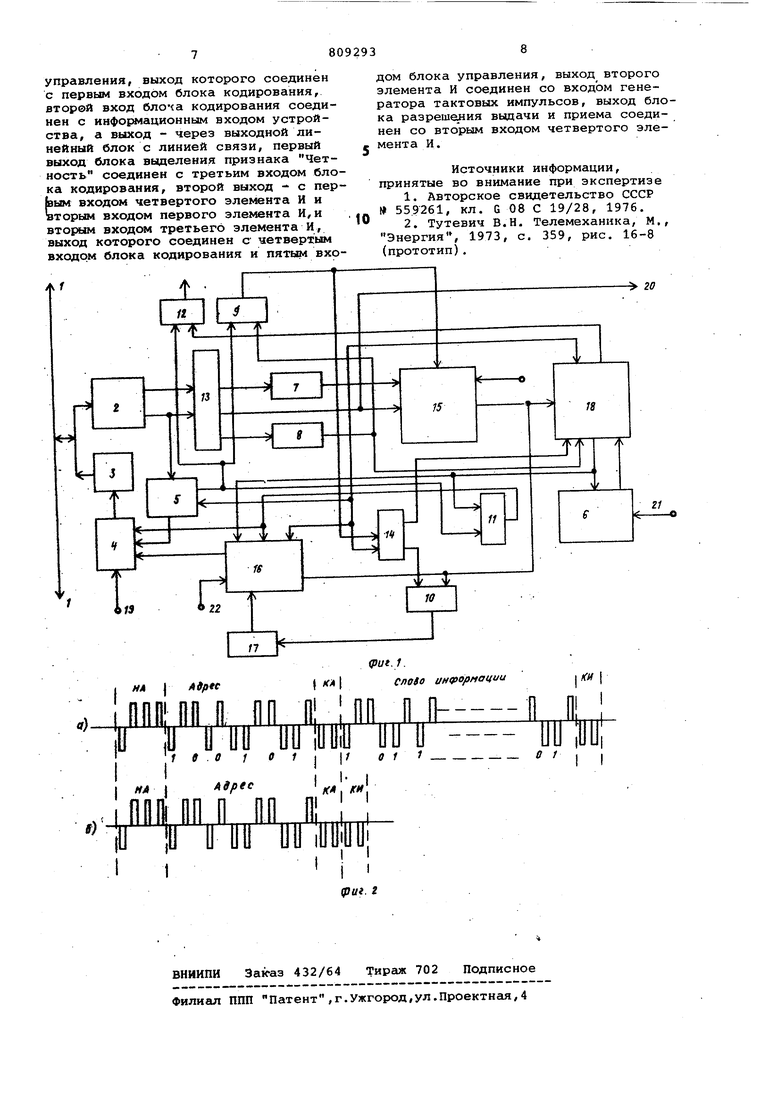

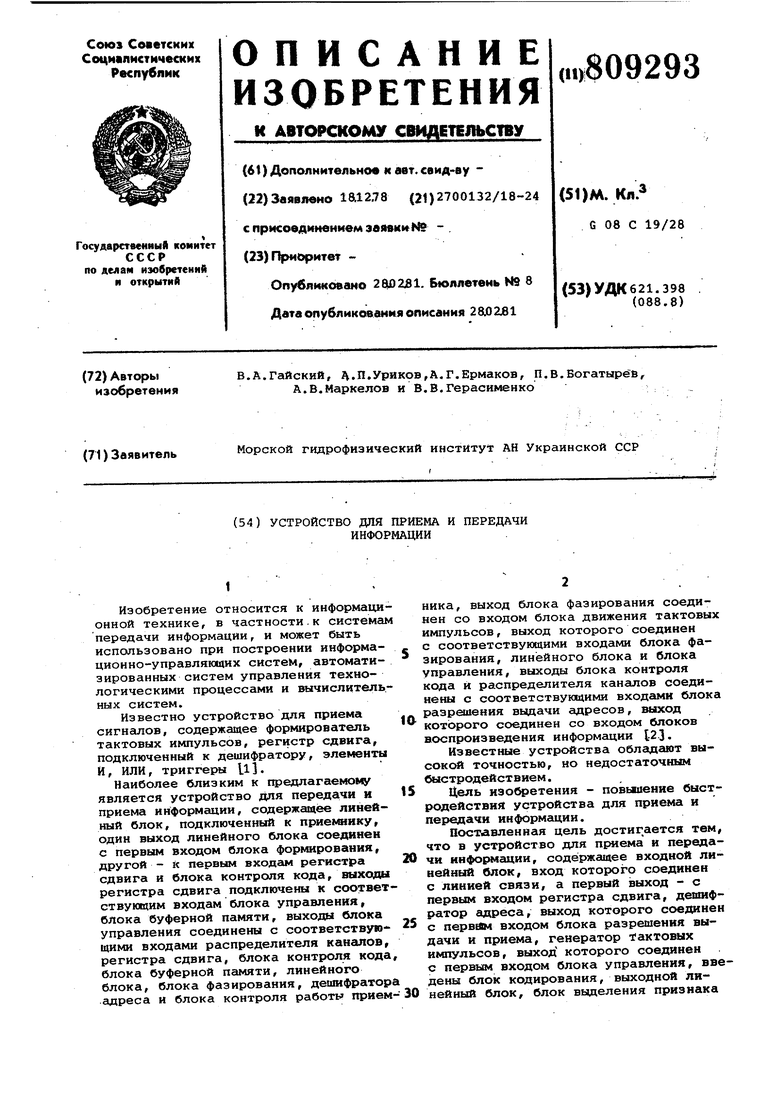

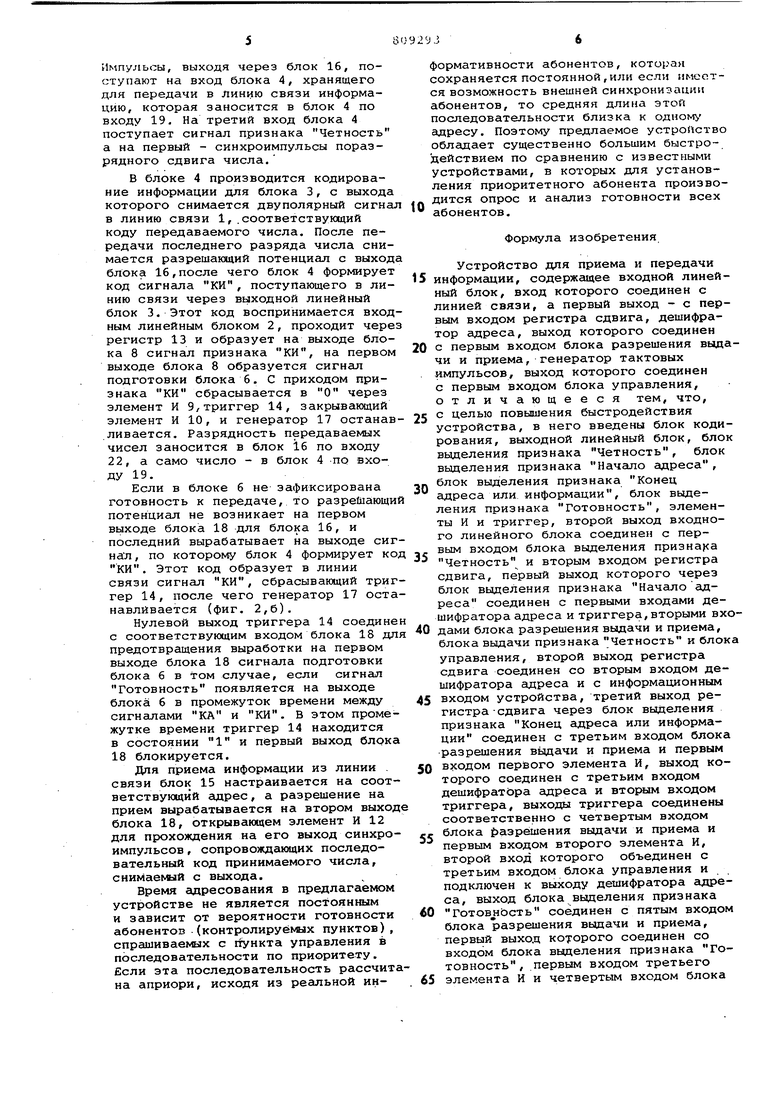

1Изобретение относится к информаци онной технике, в частности, к системеи передачи информации, и может быть использовано при построении информационно-управляющих систем, автоматизированных систем управления технологическими процессами и вычислитель ных систем. Известно устройство для приема сигналов, содержащее формирователь тактовых импульсов, регистр сдвига, подключенный к дешифратору, элементы И, ИЛИ, триггеры из. Наиболее близким к предлагаемому является устройство для передачи и приема информации, содержащее линейный блок, подключенный к прие1№ику, один выход линейного блока соединен с первым входом блока формирования, другой - к первым входам регистра сдвига и блока контроля кода, выходцы регистра сдвига подключены к соответ ствующим входам блока управления, блока буферной памяти, выходы блока управления соединены с соответствую щими входами распределителя каналов, регистра сдвига, блока контроля кода блока буферной памяти, линейного блока, блока фазирования, дешифратор адреса и блока контроля работы прием ника, выход блока фазирования соединен со входом блока движения тактовых импульсов, выход которого соединен с соответствующими входами блока фазирования, линейного блока и блока управления, выходы блока контроля кода и распределителя кангшов соединены с соответствующими входами блока разрааения вьшачи адресов, выход которого соединен со входом блоков воспроизведения информации .2.3. Известные устройства обладают высокой точностью, но недостаточным быстродействием. Цель изобретения - повышение быстродействия устройства для приема и передачи информации. Поставленная цель достиг,ается тем, что в устройство для приема и передачи информации, содержащее входной линейный блок, вход которого соединен с линией связи, а первый выход - с первым входом регистра сдвига, дешифратор адреса, выход которого соединен с nepBfliM входом блока разрешения выдачи и приема, генератор Тактовых импульсов, выход которого соединен с первым входом блока управления, введены блок кодирования, выходной линейный блок, блок выделения признака Четность, блок выделения признака Начало адреса, блок выделения признака Конец адреса или информации, блок- выделения признака Готовность элемент И и триггер, второй выход входного линейного блока соединен С первым входом блока выделения приз нака Четность и вторым входом регистра сдвига, первый выход которого через блок выделения признака Начало адреса соединен с первыми входами дешифратора адреса и триггера, вторыми входами блока разрешения выдачи и приема, блока выдачи призна ка Четность и блока управления, второй выход регистра сдвига соединен со вторым входом дешифратора адреса и с информационным выходом устройства, третий выход регистра сдвига через блок выделения признака Конец адреса или информации соединен с третьим входом блока разрешения выдачи и приема и первым входом первого элемента И, выход которого соединен с третьим входом дешифратора адреса и вторым входом триггера выходы триггера соединены соответственно с четвертым входом блока разрешения выдачи и приема и первым вхо дом второго элемента И, второй вход которого объединен с третьим входом блока управления и подключен к выходу дешифратора адреса, выход блока выделения признака Готовность соединен с пятым входом блока разрешени выдачи и приема, первый выход которо го соединен со входом блока выделения признака Готовность, первым входом третьего элемента И и четвертым входом блока управления, выход которого соединен с первым входом блока кодирования, второй вход блока кодирования соединен с информационны входом устройства, а выход - через выходной линейный блок с линией связ первый выход блока выделения признак Четность соединен с третьим входом блока кодирования, втррой выход - с первым входом четвертого элемента И, вторым входом-первого элемента И и йторым входом третьего элемента И, выход которого соединен с четвертым входом блока кодирования и пятым вхо дом блока управления, выход второго элемента И соединен со входом генератора тактовых импульсов, выход бло ка разрешения выдачи и приема соединен со вторым входом четвертого элемента И. На фиг. 1 представлена функционал ная схема предлагаемого устройства; на фиг. 2 - структура сигналов. На фиг. 1 обозначены линия связи 1, входной линейный блок 2, выходной линейный блок 3, блок 4 кодирования, блок 5 выделения признака Четность , блок 6, блок 7 выделения при .знака Начало адреса, блок 8 выделе ния признака Конец адреса или инфор мации, элементы И 9-12, регистр 13 сдвига, триггер 14, дешифратор 15 адреса, блок 16 управления, генератор 17 тактовых импульсов, блок 18 разрешения выдачи и приема, информационный вход 19 устройства, информационный выход 20 устройства, вход 21 .импульса Готовность к выдаче, вход 22 установки разрядности. Предлагаемое устройство для приема и передачи информации устанавливается на контролируемых пунктах, каждый из которых имеет свой адрес и подключен к линии связи с пунктом управления. Устройство работает следующим образом. Сигнал из линии связи 1 на вход блока 2 (форма сигнала в линии связи показана на фиг.2а). Первый выход блока 2 связ,ан с информационным входом регистра 13, а второй выход - с входом сдвигающих импульсов регистра 13. Для гистра 13 каждый положительный импульс в линии связи кодируется логической 1, а каждый отрицательный - О. Сигнал Начало адреса (НА) с выхода блока 7 в каждом цикле подготавливает устройство к работе, блок 8 служит для выделения сигналов Конец адреса (КЛ) и Конец информации (КИ). Кроме того, поскольку каждый бит информации кодируется двумя импульсами (1 кодируется комбинацией импульсов -+, а О - +-), то для выделения значения каждого разряда слова необходим блок 5. Сигнал из линии 1 связи воспринимается блоком 2, где кодируется так:отрицательные импульсы передаются на первый выход кодом О, а положительные - кодом 1. Эта информация заносится в регистр 13 синхроимпульсами со второго выхода блока 6. После приема адреса дешифратор 15 срабатывает в случае совпадения принятого адреса с адресом данного контролируемого пункта. С приходом сигнала КА, снимаемого с выхода блока 8, и следующего за ним строба четности на втором выходе блока 5, сигн.алом с выхода элементам 9 подается, раз решающий потенциал на третий вход дешифратора 15, сигналом с выхода которого включается блок 18. Если к этому моменту времени в блоке 6 была зафиксирована готовность к передаче (по импульсу готовности, подаваемому на вход 21),то на выходе его был подготовлен второй разрешающий потенциал для блока 18. В этом случае блок 18 срабатывает,выдавая на первом выходе разрешающий сигнал для блока 16, который после этого roYoB к приему импульсов генератора 17. Задним.Фронтом строба четности, проходящего через элемент И 9, устанавливается в 1 триггер 14 j после чего срабатывает элемент И 10, включая генератор 17.

Импульсы, выходя через блок 16, поступают на вход блока 4, хранящего для передачи в линию связи информацию, которая заносится в блок 4 по входу 19, На третий вход блока 4 поступает сигнал признака Четность а на первый - синхроимпульсы поразрядного сдвига числа.

В блоке 4 производится кодирование информации для блока 3, с выхода которого снимается двуполярный сигнал в линию связи 1,.соответствующий коду передаваемого числа. После передачи последнего разряда числа снимается разрешающий потенциал с выхода блока 16,после чего блок 4 формирует код сигнала КИ, поступающего в линию связи через выходной линейный блок 3. Этот код воспринимается входным линейным блоком 2, проходит через регистр 13 и образует на выходе блока 8 сигнал признака КИ, на первом выходе блока 8 образуется сигнал подготовки блока 6. С приходом признака КИ сбрасывается в О через элемент И 9,триггер 14, закрывающий элемент И 10, и генератор 17 останав.ливается. Разрядность передаваемых чисел заносится в блок 16 по входу 22, а само число - в блок 4 по входу 19.

Если в блоке 6 не зафиксирована готовность к передаче, то разрешающий потенциал не возникает на первом выходе блока 18 для блока 16, и последний вырабатывает на выходе сигнал, по которому блок 4 формирует код КИ. Этот код образует в линии связи сигнал КИ, сбрасывающий триггер 14, после чего генератор 17 останавливается (фиг. 2,б).

Нулевой выход триггера 14 соединен с соответствующим входом блока 18 для предотвращения выработки на первом выходе блока 18 сигнала подготовки блока 6 в том случае, если сигнал Готовность появляется на выходе блока 6 в промежуток времени между сигнашами КА и КИ. В этом промежутке времени триггер 14 находится в состоянии 1 и первый выход блока 18 блокируется.

Для приема информации из линии . связи блок 15 настраивается на соответствующий адрес, а разрешение на прием вырабатывается на втором выходе блока 18, открывающем элемент И 12 для прохождения на его выход синхроимпульсов , сопровождающих последовательный код принимаемого числа, снимаемой с выхода.

Время адресования в предлагаемом устройстве не является постояншлм и зависит от вероятности готовности абонентов (контролируемых пунктов) , спрашиваемых с пункта управления в последовательности по приоритету. Если эта последовательность рассчитана априори, исходя из реальной информативности абонентов, которая сохраняется постоянной,или если имеется возможность внешней синхронизации абонентов, то средняя длина этой последовательности близка к одному адресу. Поэтому предлаемое устройство облсщает существенно большим быстродействием по сравнению с известными устройствами, в которых для установления приоритетного абонента производится опрос и анализ готовности всех абонентов.

изобретения

Устройство для приема и передачи

информации, содержащее входной линейный блок, вход которого соединен с линией связи, а первый выход - с первым входом регистра сдвига, дешифратор адреса, выход которого соединен

с первым входом блока разрешения выдачи и приема, генератор тактовых импульсов, выход которого соединен с первым входом блока управления, отличающееся тем, что,

с целью повышения быстродействия

устройства, в него введены блок кодирования, выходной линейный блок, блок выделения признака Четность, блок выделения признака Начало гщреса, блок выделения признака Конец адреса или информации, блок вьщеления признака Готовность, элементы И и триггер, второй выход входного линейного блока соединен с первым входом блока вьщеления признака

Четность и вторым входом регистра сдвига, первый выход которого через блок выделения признака Началоадреса соединен с первыми входами дешифратор а адрес а и триггера,вторыми входами блока разрешения выдачи и приема, блока выдачи признака Четность и блока управления, второй выход регистра сдвига соединен со вторым входом дешифратора адреса и с информационным

входом устройства, третий выход регистра-сдвига через блок выделения признака Конец адреса или информации соединен с третьим входом блока разрешения выдачи и приема и первым

входом первого элемента И, выход которого соединен с третьим входом дешифратора гщреса и вторым входом триггера, выходы триггера соединены соответственно с четвертым входом

блока 4 аэрёшения выдачи и приема и первым входом второго элемента И, второй вход которого объединен с третьим входом блока управления и подключен к выходу дешифратора гщреса, выход блока вьщеления признака

roTOBjibcTb соединен с пятым входом блока разрешения выдачи и приема, первый выход которого соединен со входом блока выделения признака Готовность, первым входом третьего

элемента И и четвертым входом блока

управления, выход которого соединен с первым входом блока кодирования, второй вход кодирования соединен с информационным входом устройства, а выход - через выходной линейный блок с линией связи, первый выход «5лока выделения признака Четность соединен с третьим входом блока кодирования, второй выход - с перЬым входом четвертого элемента И и вторым входом первого элемента И,и BTopftiM входом третьего элемента И, выход которого соединен с четвертым входом блока кодирования и пятым входом блока управления, выход второго элемента И соединен со входом генератора тактовых импульсов, выход блока разрешения выдачи и приема соединен со вторым входом четвертого элемента И.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 559261, кл. G 08 С 19/28, 1976.

2.Тутевич В.Н. Телемеханика, М., Энергия, 1973, с. 359, рис. 16-8 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУНИКАЦИОННОГО ИНТЕРФЕЙСА | 2010 |

|

RU2460124C2 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532937A1 |

| Устройство для передачи и приема информации | 1980 |

|

SU903935A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1981 |

|

SU976437A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

put.i. Cnoio инфорпации

Авторы

Даты

1981-02-28—Публикация

1978-12-18—Подача