Изобретение относится к вычислительной технике и предназначено для сложения-вычитания двоично-десятичных и двоичных чисел.

Известен сумматор-вычитатель для двоично-кодированных десятичных чисел содержащий одноразрядный сумматор, преобразователь двоичного кода в десятичный для осуществления коррекции результатов в случае переносов между двоично-десятичными числами и линии задержки 1 .

Однако это устройство сложно и содержит значительное число линий задержки.

Известно малогабаритное вычислительиое устройство, содержащее четыре регистра, сумматор последовательного действия и ряд цепей с логическими элемвитгив 2 . Недостатком этого устройCTsa для выполнения операций сложения-вычитания является значительная аппаратурная избыточность.

Наиболее близким по технической сущности к изобретению является устройство для последовательного сложения и вычитания чисел, содержащее одноразрядный сумматор-вычитатель, сдвиговые регистры первого и второго слагаемых, блок коррекции, элемент задержки, элементы И и ИЛИ. Первый и второй входы сумматора-вычитателя соединены с выходами младших разрядов сдвиговых регистров соответственно первого и второго слагаемьах, а выход сумматора подключен ко входу старшего разряда сдвигового регистра первого слагаемого . Однако это устройство сложно.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что в предложенном устройстве сдвиговый регистр второго слагаемого содержит дополнительный разряд, выход которого подключен ко входу старшего .разряда этого регистра, а вход - к выходу блока коррекции. Первый, второй и третий входы блока коррекции подключены к выходам трех старших разрядов сдвигового регистра первого слагаемого, четвертый вход - к выходу первого элемента И, первый вход которого через элемент задержки подключен к выходу переноса одноразрядного сумматора-вычитателя, а второй вход - к шине разрешения переноса. Пятый вход блока коррекции подключен к первому управляющему входу устройства. Выход блока коррекции подключен к первому

входу элемента ИЛИ, выход которого содинен со вторым и третьим старшими разрядами сдвигового регистра второго слагаемого. Второй вход элемента ИЛИ соединен с внходом второго элемента И, первый лкод которого подключен к выходу первого элемента и, а второй вход - ко второму управляющему входу устройства.

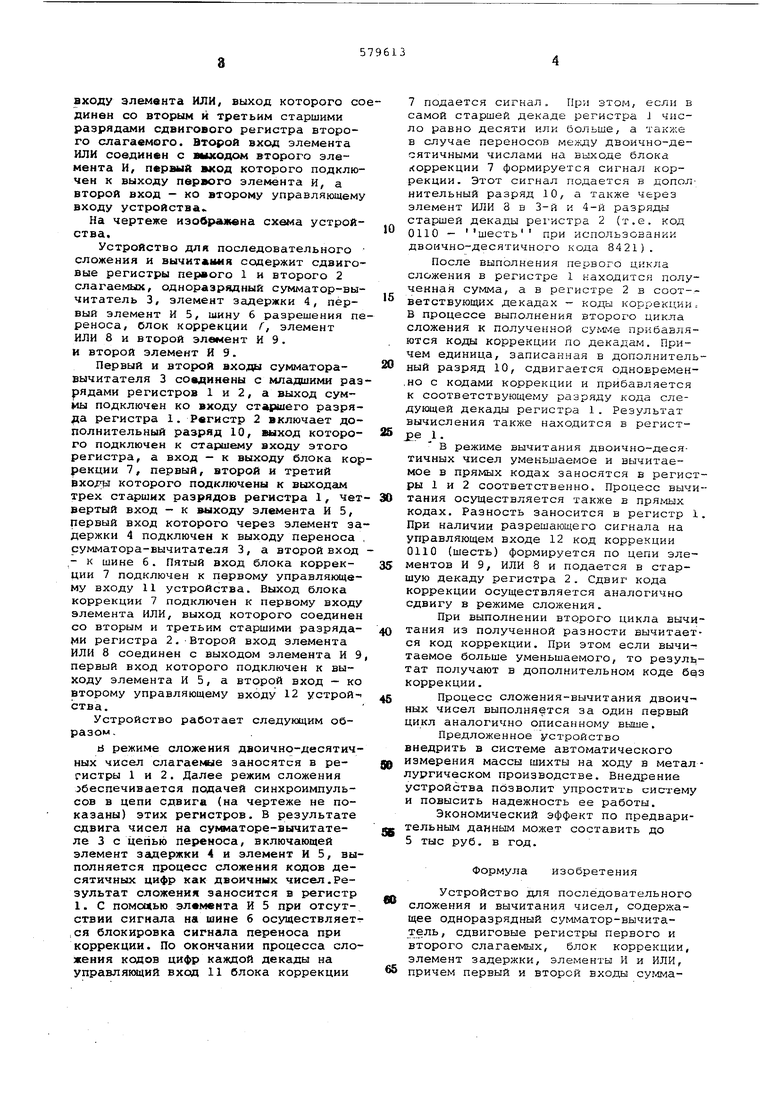

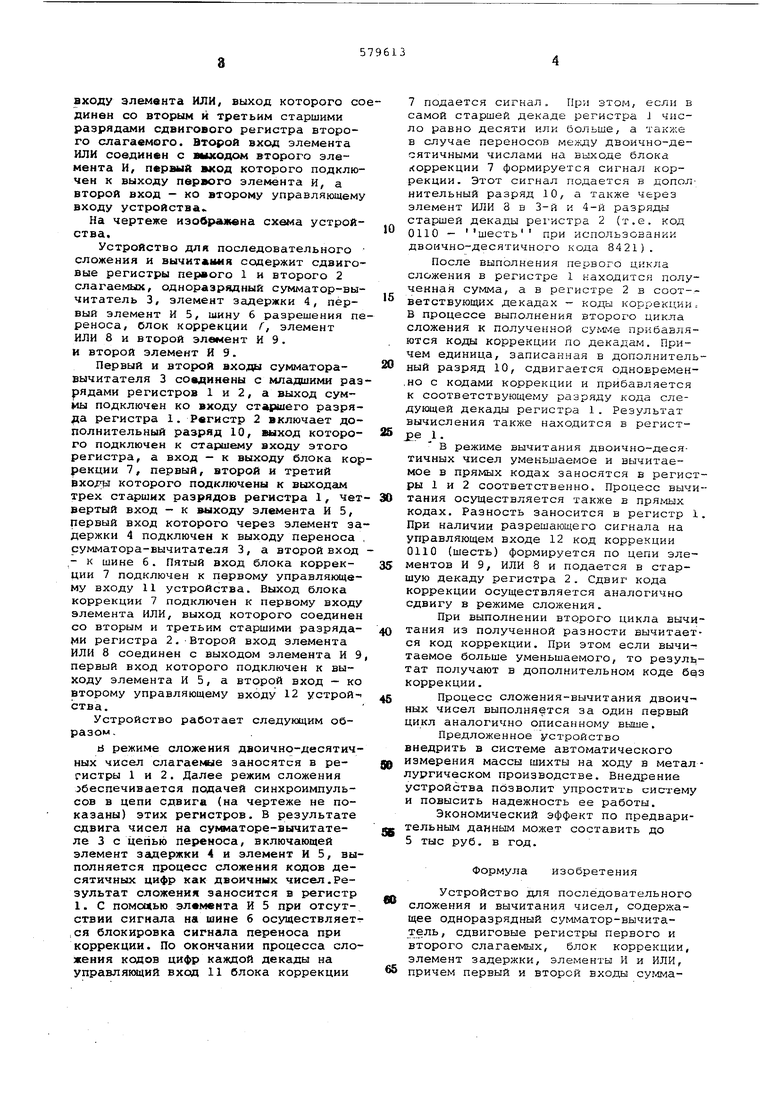

На чертеже изображена схема устройства.

Устройство для последовательного сложения и вычитания содержит сдвиговые регистры первого 1 и второго 2 слагаемых, одноразрядный сумматор-вычитатель 3, элемент задержки 4, первый элемент И 5, шину 6 разрешения переноса, елок коррекции f, элемент ИЛИ 8 и второй элемент И 9. И второй элемент И 9.

Первый и второй входы сумматоравычитателя 3 соединены с младшими разрядами регистров 1 и 2, а выход суммы подключен ко входу старшего разряда регистра 1. Регистр 2 включает дополнительный разряд 10, выход которого подключен к стараиему входу этого регистра, а вход - к выходу блока коррекции 7, первый, второй и третий которого подключены к выходам трех старших разрядов регистра 1, четвертый вход - к выходу элемента И 5, первый вход которого через элемент задержки 4 подключен к выходу переноса сумматора-вычитателя 3, а второй вход ,- к шине 6. Пятый вход блока коррекции 7 подключен к первому управлякнцему входу 11 устройства. Выход блока коррекции 7 подключен к первому входу элемента ИЛИ, выход которого соединен со вторым и третьим старшими разрядами регистра 2, Второй вход элемента ИЛИ 8 соединен с выходом элемента И 9 первый вход которого подключен к выходу элемента И 5, а второй вход - ко второму управляющему входу 12 устрой-ства.

Устройство работает следующим образом ,

tJ режиме сложения двоично-десятичных чисел слагаемые заносятся в регистры 1 и 2. Далее режим сложения обеспечивается подачей синхроимпульсов в цепи сдвига (на чертеже не показаны) этих регистров. В результате сдвига чисел на сумвлаторе-вычитателе 3 с цепью переноса, включающей элемент задержки 4 и элемент И 5, выполняется процесс сложения кодов десятичных цифр как двоичных чисел.Результат сложения заносится в регистр 1. С помоиью элемента И 5 при отсутствии сигнала на шине 6 осуществляет ,ся блокировка сигнала переноса при коррекции. По окончании процесса сложения кодов цифр каждой декады на управляющий вход 11 блока коррекции

7подается сигнал. При этом, если в самой старшей декаде регистра J чнсло равно десяти или больше, а также в случае переносов между двоично-десятичными числами на выходе блока коррекции 7 формируется сигнал коррекции. Этот сигнал подается в дополнительный разряд 10, а также через элемент ИЛИ 8 в 3-й и 4-й разряды старшей декады регистра 2 (т.е. код

ОНО - шесть при использовании двоично-десятичного кода 8421).

После выполнения первого цикла сложения в регистре 1 находится полученная сумма, а в регистре 2 в соот-ветствующих декадах - коды коррекции

8процессе выполнения второго цикла сложения к полученной сумме прибавляются коды коррекции по декадам. Причем единица, записанная в дополнительный разряд 10, сдвигается одновремен,но с кодами коррекции и прибавляется к соответствующему разряду кода следуквдей декады регистра 1 . Результат вычисления также находится в регистре 1.

в режиме вычитания двоично-десятичных чисел уменьшаемое и вычитаемое в прямых кодах заносятся в регистры 1 и 2 соответственно. Процесс вычи0 танин осуществляется также в прямых кодах. Разность заносится в регистр 1. При наличии разрешающего сигнала на управляющем входе 12 код коррекции ОНО (шесть) формируется по цепи элементов И 9, ИЛИ 8 и подается в старшую декаду регистра 2. Сдвиг кода коррекции осуществляется аналогично сдвигу в режиме сложения.

При выполнении второго цикла вычитания из полученной разности вычитается код коррекции. При этом если вычи- таемое больше уменьшаемого, то результат получают в дополнительном коде бв.з коррекции.

6 Процесс сложения-вычитания двоичных чисел выполняется за один первый цикл аналогично описанному выше.

Предложенное устройство внедрить в системе автоматического

g измерения массы шихты на ходу в металлургическом производстве. Внедрение устройства позволит упростить систему и повысить надежность ее работы.

Экономический эффект по предвариак тельным данным может составить до 5 тыс руб. в год.

Формула изобретения Устройство для последовательного

сложения и вычитания чисел, содержащее одноразрядный сумматор-вычитатель, сдвиговые регистры первого и второго слагаемых, блок коррекции, элемент задержки, элементы И и ИЛИ, причем первый и второй входы сумматора-вычитателя соединены с выходами младших разрядовсдвиговых регистров соответствеино первого и второго слагаемых, а выход сумматора-вычитателя подключен ко входу старшего разряда сдвигового регистра первого слагаемого, отли ч ающе ес я тем, что, с целью упрощения устройств сдвиговый регистр второго слагаемого содержит дополнительный разряд, выход которого подключен ко входу старшего разряда этого регистра, а вход - К выходу блока коррекции, первый, вто рой и третий входы которого подключены к выходам трех старших оазрядов сдвигового регистра первого слагаемого, четвертый вход - к выходу первого элемента И, первый вход которого чере элеме {т задержки подключен к выходу переноса одноразрядного сумматора-вычитателя, а второй вход - к шине разрешения переноса; пятый вход блока ко рекции подключен к первому управляющему входу устройства; выход блока кор- рекции подключен к первому входу элемента ИЛИ, выход которого соединен со вторым и третьим старшими разряда ми сдвигового регистра второго слагаемого; второй вход элемента ИЛИ соединен с выходом второго элемента И, первый вход которого подключен к выходу первого элемента И, а второй вход - ко второму Управляющему входу устройства. Источники информации, принятые во внимание при экспертизе: 1.Патент США № 3694642, кл. га5-170, 1972. 2.Патент Японии 49-28212, кл. 97(7)Н9, 1975. 3.Патент Франции 2151477, кл. е 06 Р 7/00, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Одноразрядный десятичный сумматор | 1975 |

|

SU690479A1 |

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

Авторы

Даты

1977-11-05—Публикация

1976-04-07—Подача