(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1980 |

|

SU896741A2 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

| Умножитель частоты | 1981 |

|

SU1058021A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Цифровой умножитель частоты следования импульсов | 1980 |

|

SU1013952A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

1

Изобретение относится к радиотехнике и может использоваться для умножения частоты, например, в системах автоматики и контрольноизмерительной техники, а также для увеличения девиации частоты в следящих системах.

Известен умножитель частоты, содержащий последовательно соединенные первый опорный генератор, первый счетчик, устройство памяти, устройство сравнения кодов и буферное устройство, а также последовательно соединенные второй опорный генератор и второй счетчик, выход которого соединен с другим входом устройства сравнения кодов 1 .

Однако в известном умножителе частоты Недостаточно высок коэффициент умноження, определяемый отношением опорных частот, первая из которых выбирается из условия обеспечения требуемой точности, а вторая зависит от быстродействия элементной базы.

Цель изобретения - увеличение козффициента умножения.(

Для этого в умножитель частоты, содержащий последовательно соедине1шые П1грвый опорный генератор, первый счетчик, устройство памяти, устройство сравнения кодов и буферное устройство, а также послёдъвйтельнб соединенные второй опорный генератор и второй счетчик, выход которого соединён с другим входом устройства сравнения тсодов, введен триггер, установочный вход которого подключен х выходу устройства памяти, а прямой и инверсный выходы триггера через вновь введенные первый и второй элементы И соединены с установочнь1ми вхОдаК1и в 6рого счетчика, а вторые входы элементов И и счетный вход триггера объединены и подключены к выходу буферного устройства.

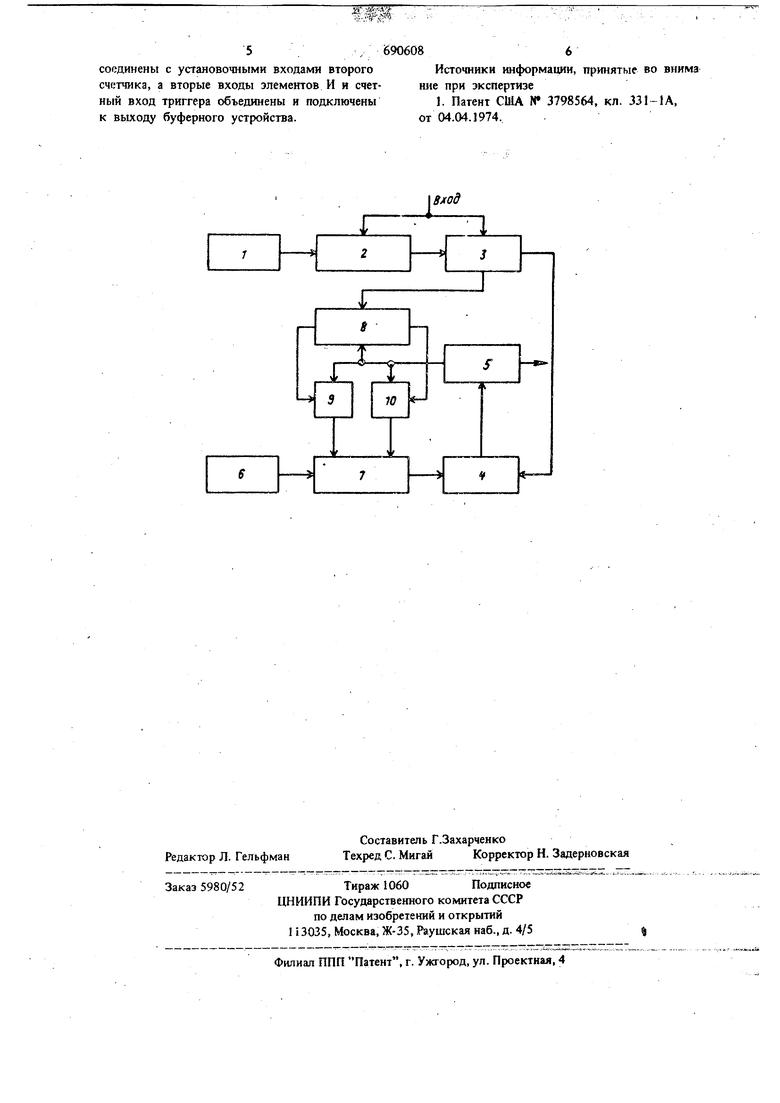

На чертеже приведена структурная электрическая схема предложенного устройства.

5, Умножитель частоты содержит последователь но соединенные первый опорный генератор 1, первый счетчик 2, устройство памяти 3, устройство сравнения кодов 4 и буферное устрой ство 5, а так5ке последовательно соединенные

0 второй опорный генератор 6 и второй счетчик

7,выход которого соединен с другим входом устройства сравнения кодов 4, а также триггрр

8,установочный вход которого подключен к вы 369 выходу устройства памяти 3, а прямой и инверсный выходы триггера 8 через первый и вто рой элементы И 9 и 10 соединены с установочными входами второго счетчика 7, а вторые входы элементов И 9 и 10 и счетный вход триггера 8 объединены и подключены к выходу буферного устройства 5. Устройство работает следующим образом. На вход устройства поступают сигналы в нине узких импульсов, при этом обнуляется первый счетчик 2, а также происходит перенос кода, содержащегося в первом счетчике 2 до поступления этого импульса, в устройство памяти 3. Код с устройства памяти 3 поступает на один вход устройства сравнения кодов 4 со сдвигом на один разряд относительно кода, формирующегося во втором счётчике 7 и поступающего на другой вход устройства сравнения кодов 4. Таким образом, на первый вход устройства сравнения кодов 4 поступает код в два. раза меньще содержащегося в устройстве памяти 3. На вход второго счетчика 7 поступают импульсы со второго опорного генератора 6 с частотой в п раз больщей частоты первого опорного генератора 1, сигналы с которого поступают на первый счетчик 2. Устройство сравнения ко дов 4 вырабатывает импульсный сигнал в момент равенства кодов на его входах. Этот сигнал поступает через буферное устройство 5 на входы элементов И 9, 10 и на счетный вход триггера 8. Сигнал с младшего разряда устройства памя ти 3 поступает на установочный вход триггера 8. Если в младшем разряде устройства памяти 3 содержится сигнал нулевого уровня триггер 8 устанавливается в определенное состояние, и с его прямого выхода поступает запрещающий потенциал на вход элемента И 9. На вход элемента М 10 поступает разрещающий потенциал с инверсного выхода триггера 8. Триггер 8 при этом не переключается нри поступлении на его счетный вход импульсов с буферного устройства 5, а элемент И 10 пропускает эти импульсы на вход установки в ноль второго счетчика 7. Таким образом, при наличии в. устройстве памяти 3 четного числа и при этом в младщем разряде его - сигнала нулевого уровня, второй счепик 7 формирует код до значения, равного половине значения кода, содержащегося в устройстве памяти 3. При равенстве кодов на входах устройства сравнения 4 - на его выходе вырабатывается импульс, который через буферное устройство 5 и через элемент И 10 поступает на вход установки в ноль второго счетчика 7, обнуляя го. Далее процесс понторяется. Иэ выходе буферного устройства S формируются импульсы с чистотой fjjf,. 2.n.fi, за счет использования второю опорного генератора 6 с частотой в п раз больн1ей частоты опорного генератора 1 и за счет подачи кода с устройства памяти 3 на вход устройства сравнения кодов 4 со сдвигом на один разряд относительно кода, поступающего со второго счетчика 7. При наличии в устройстве памяти 3 нечетного числа в его младшем разряде содержится сигнал единичного уровня, ноступающий на установочный вход триггера 8. При этом триггер 8 будет переключаться из одного состояния в противоположное при поступлении на его счетный вход сигнала с выхода буферного устройства 5. Элементы И 9, 10 будут поочередно пропускать импульсы, формируемые устройством сравнения кодов 4, на вход установки в ноль, или на вход установки минус единицы второго счетчика 7 соответственно. Таким образом, суммарная длительность двух соседних интервалов времени между импульсами, вырабатываемыми устройством сравнения кодов 4, будет ссютветствовать коду, содержащемуся в устройстве памяти 3. Длительность одного интервала времени будет отличаться от длительности соседнего - на один такт частоты второго опорного генератора 6 за счет нечетности кода, содержащегося в устройстве памяти 3. При изменении входной частоты изменяется код, формируемый первым счетчиком 2 и соответственно выходная частота устройства. Таким образом, в предложенном устройстве коэффициент умножения увеличивается в два раза по сравнению с известным устройством за счет формирования вторым счетчиком 7 кода, в два раза меньшего, чем в известном устройстве, и введения триггера 8 и элементов И 9 и 10. Формула изобретения Умножитель частоты, содержащий последова-. тельно соединенные первый опорный генератор, первый счетчик, устройство памяти, устройство сравнения кодов и буферное устройство, а также последовательно соединенные второй опорный генератор и второй счеТчик, выход которогЬ соединен с другим входом устройства сравнения кодов, отличающийся тем, что, с целью увеличения коэффициента умножения, введен триггер, установочный вход которого подключен к выходу устройства памяти, а прямой и инверсный выходы триггера через вновь введенные первый и второй элементы И

,. . - . .. :

5 , (5906086

соединены с установочными входами второгоИсточники информации, принятые во виима

счетчика, а вторые входы элементов И и счет-ние при экспертизе

ный вход триггера объединены и подключены1. Патент США N 3798564, кл. 331-1А,

к выходу буферного устройства.от 04.04.1974.

1S:Kff,,.. V- . . ; :

Авторы

Даты

1979-10-05—Публикация

1977-10-21—Подача