(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретный умножитель частоты | 1980 |

|

SU896740A2 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Дискретный умножитель частоты следования импульсов | 1980 |

|

SU928345A2 |

| Умножитель частоты | 1977 |

|

SU690608A1 |

| Цифровой умножитель частоты следования импульсов | 1980 |

|

SU1013952A1 |

| Цифровой умножитель частоты следования импульсов | 1984 |

|

SU1226604A1 |

| Генератор функций | 1984 |

|

SU1275411A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

1

Изобретение относится к радиотехнике и может быть использовано для умножения частоты в системах автоматики, контрольно-измерительной технике, в контрольноиспытательной аппаратуре аналого-цифровых преобразователей.

По основному авт. св. № 690608 известен умножитель частоты, содержащий после довательно соединенные первый опорный генератор, первый счетчик, устройство памяти, устройство сравнения кодов, буферное устройство, первый триггер, установочный вход которого подключен к выходу устройства памяти, а прямой и инверсный выходы первого триггера через первый и второй элементы И соединены с установочными входами второго счетчика, вход которого подключен к выходу второго опорного генератора, а выход соединен с другим входом устройства сравнения кодов, причем вторые входы элементов И объединены и подключены к выходу буферного устройства 1 .

Недостатком известного умножителя частоты является низкая надежность, так как в случае отсутствия входного сигнала на выходе устройства формируется ложный сигнал.

Цель изобретения - повышение надежности.

Для достижения поставленной цели в умножитель частоты, содержащий последовательно соединенные первый опорный генератор, -первый счетчик, устройство памяти, устройство сравнения кодов, буферное устройство, первый триггер, установочный вход которого подключен к выходу устройства памяти, а прямой и инверсный выходы первого триггера через первый и второй элементы И сое10динены с установочными входами второго счетчика, вход которого подключен к выходу второго опорного генератора, а выход соединен с другим входом устройства сравнения кодов, причем вторые входы элементов И объединены и подключены к выходу буфер sного устройства, введен второй триггер, причем первый вход второго триггера подключен к выходу старшего разряда первого счетчика, второй вход - к другому входу первого счетчика, а выход второго тригге20ра подключен ко второму установочному входу устройства памяти.

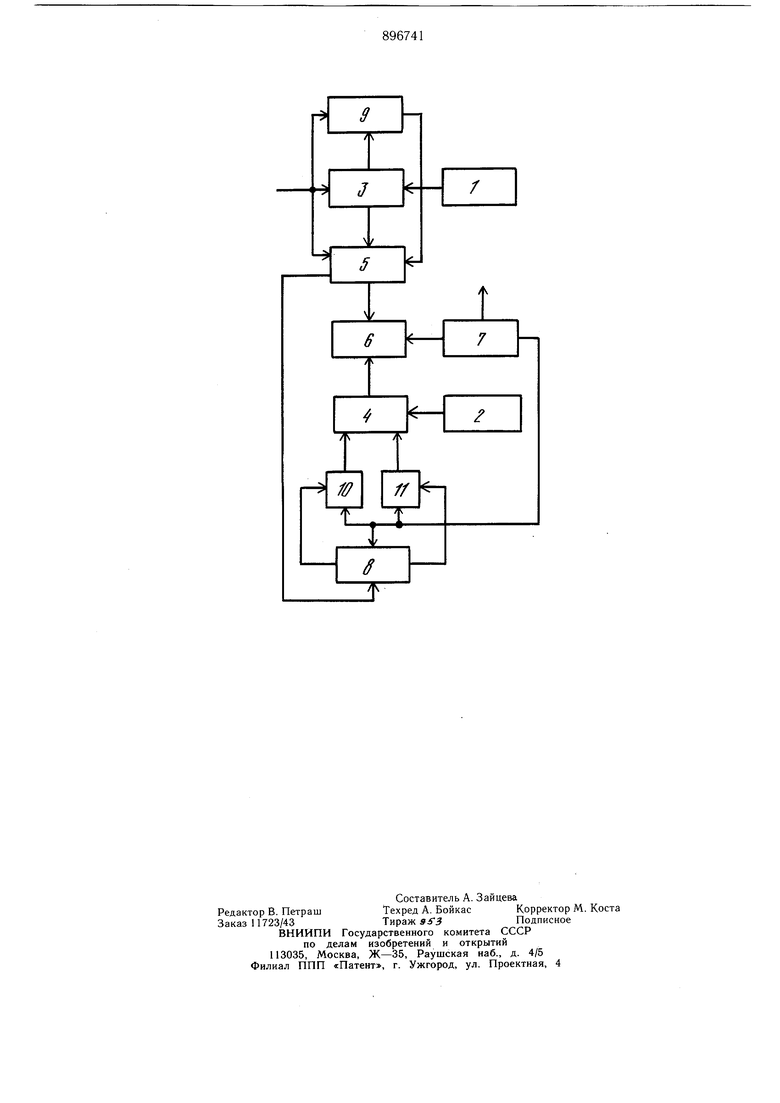

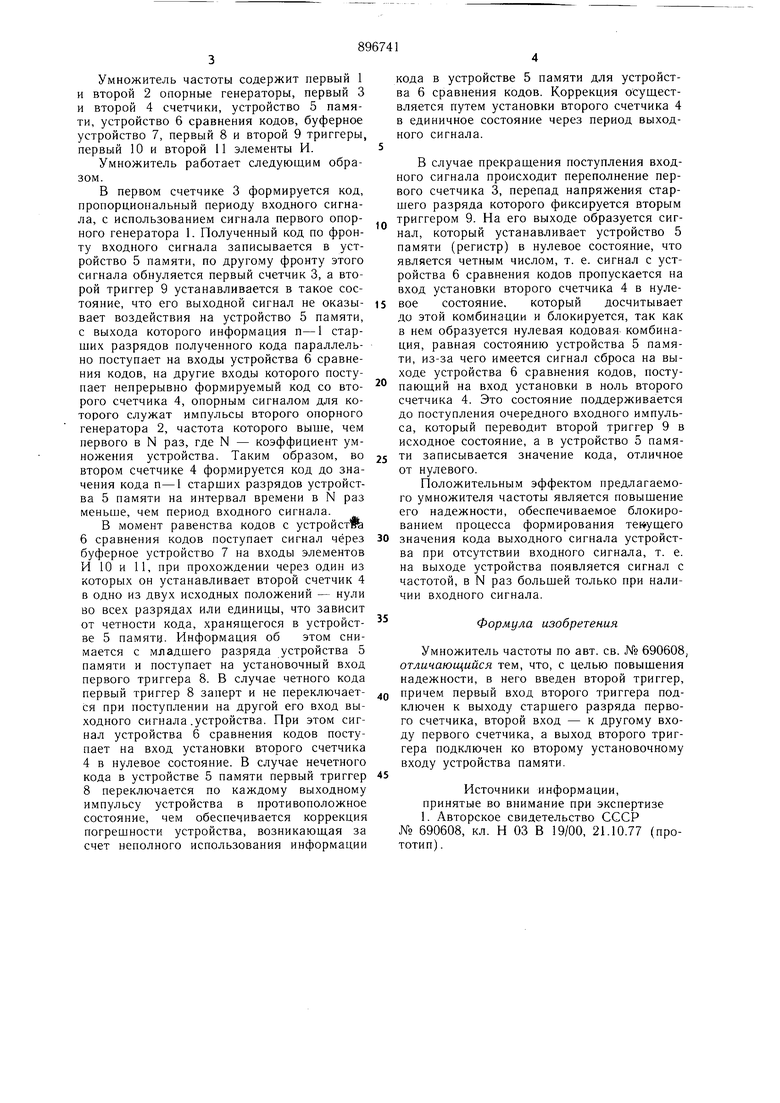

На чертеже приведена структурная электрическая схема умножителя частоты.

Умножитель частоты содержит первый 1 и второй 2 опорные генераторы, первый 3 и второй 4 счетчики, устройство 5 памяти, устройство 6 сравнения кодов, буферное устройство 7, первый 8 и второй 9 триггеры, первый 10 и второй 11 элементы И.

Умножитель работает следующим образом.

В первом счетчике 3 формируется код, пропорциональный периоду входного сигнала, с использованием сигнала первого опорного генератора 1. Полученный код по фронту входного сигнала записывается в устройство 5 памяти, по другому фронту этого сигнала обнуляется первый счетчик 3, а второй триггер 9 устанавливается в такое состояние, что его выходной сигнал не оказывает воздействия на устройство 5 памяти, с выхода которого информация п-1 старших разрядов полученного кода параллельно поступает на входы устройства 6 сравнения кодов, на другие входы которого поступает непрерывно формируемый код со второго счетчика 4, опорным сигналом для которого служат импульсы второго опорного генератора 2, частота которого выше, чем первого в N раз, где N - коэффициент умножения устройства. Таким образом, во втором счетчике 4 формируется код до значения кода п-1 старших разрядов устройства 5 памяти на интервал времени в N раз меньше, чем период входного сигнала.

В момент равенства кодов с устройст 6 сравнения кодов поступает сигнал через буферное устройство 7 на входы элементов И 10 и 11, при прохождении через один из которых он устанавливает второй счетчик 4 в одно из двух исходных положений - нули во всех разрядах или единицы, что зависит от четности кода, хранящегося в устройстве 5 памяти. Информация об этом снимается с младшего разряда устройства 5 памяти и поступает на установочный вход первого триггера 8. В случае четного кода первый триггер 8 заперт и не переключается при поступлении на другой его вход выходного сигнала .устройства. При этом сигнал устройства 6 сравнения кодов поступает на вход установки второго счетчика 4 в нулевое состояние. В случае нечетного кода в устройстве 5 памяти первый триггер 8 переключается по каждому выходному импульсу устройства в противоположное состояние, чем обеспечивается коррекция погрешности устройства, возникающая за счет неполного использования информации

кода в устройстве 5 памяти для устройства 6 сравнения кодов. Коррекция осуществляется путем установки второго счетчика 4 в единичное состояние через период выходного сигнала.

В случае прекращения поступления входного сигнала происходит переполнение первого счетчика 3, перепад напряжения старшего разряда которого фиксируется вторым триггером 9. На его выходе образуется сигнал, который устанавливает устройство 5 памяти (регистр) в нулевое состояние, что является четным числом, т. е. сигнал с устройства 6 сравнения кодов пропускается на вход установки второго счетчика 4 в нулевое состояние, который досчитывает до этой комбинации и блокируется, так как в нем образуется нулевая кодовая комбинация, равная состоянию устройства 5 памяти, из-за чего имеется сигнал сброса на выходе устройства 6 сравнения кодов, поступающий на вход установки в ноль второго счетчика 4. Это состояние поддерживается до поступления очередного входного импульса, который переводит второй триггер 9 в исходное состояние, а в устройство 5 памяти записывается значение кода, отличное от нулевого.

Положительным эффектом предлагаемого умножителя частоты является повышение его надежности, обеспечиваемое блокированием процесса формирования текущего значения кода выходного сигнала устройства при отсутствии входного сигнала, т. е. на выходе устройства появляется сигнал с частотой, в N раз большей только при наличии входного сигнала.

Формула изобретения

Умножитель частоты по авт. св. № 690608, отличающийся тем, что, с целью повышения надежности, в него введен второй триггер, причем первый вход второго триггера подключен к выходу старшего разряда первого счетчика, второй вход - к другому входу первого счетчика, а выход второго триггера подключен ко второму установочному входу устройства памяти.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 690608, кл. Н 03 В 19/00, 21.10.77 (прототип) .

Авторы

Даты

1982-01-07—Публикация

1980-04-10—Подача