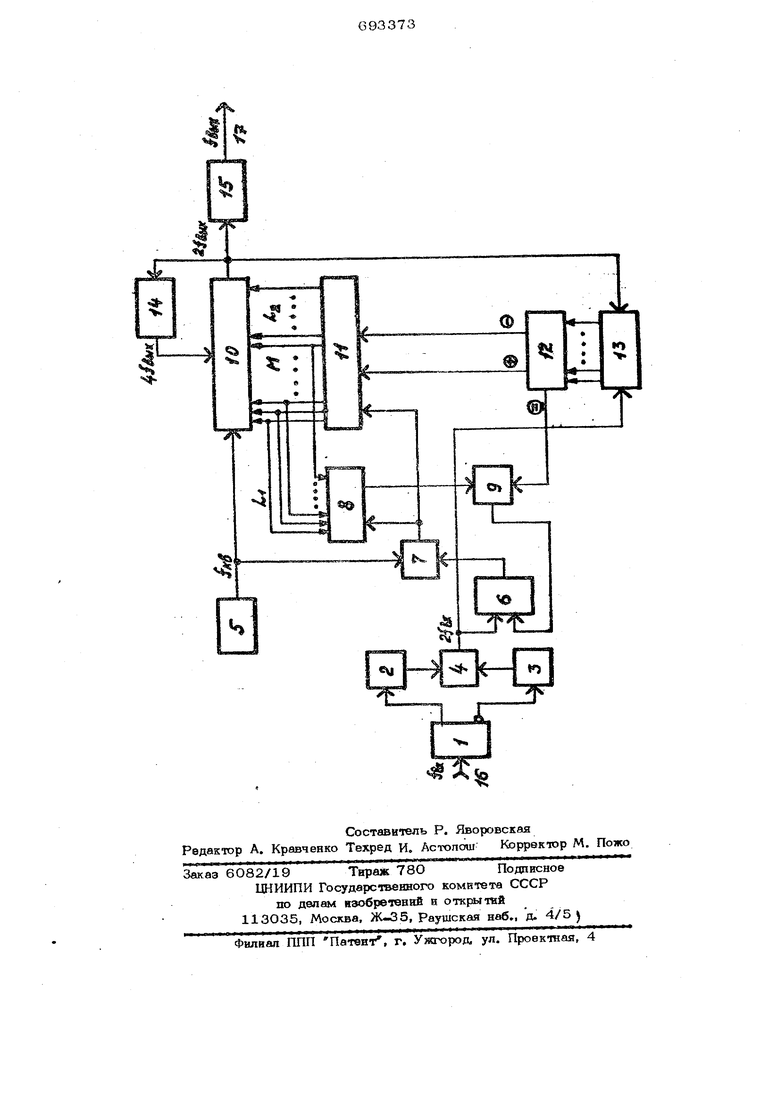

. . -../. .1 ; Изобретение отиоситсга к б0лаета вы-, числителшрЁ техника и мрже.т бать ас-, пользовано для умножения низких и йнфор мапйониих частот.:. Известаме цн фовые умножители визквх в нвакйх частот l обладают существенной пргрещнрстыо умножевйя, обусловленной, например, наличием шстоян ной сЬставляюшей ,в выходном сигнале уси лителя юграничнтеДя. Уменьшение данной ногревшостй делением частоты ухудшает временные зсарактервстаки преобразования (уменьшается быстродействие). Наиболее близким техническим решением к предлагаемому является умножитель часто-ям; содержавши ynpiaaтшемыи делитель частоты, .информационные входы которого ерединевы с шхрда- ми счетчика, генератор импулЬсЬв, выход которого подключен к первому управляющему входу управляемого делителя частоты, формирователь импульсов, входом соединенный с клходрм управляемого делителя частоты и входом первого тригге- pa, шлход которого является выходом умВОжйтепя частоты, выход формирователя импулЬсрв 1к:)далючев к уйравляюшему входу управляЕом01ч двйвтеля часто ты, эл емент И, первый вход кЪторого соединен с выходом BtopOrp л ригтёра, усилитель, вход которого является умножителя, вы- хода усилителя по дкл|Ьчейы ковходам амядвтудаых Д11Ь|фйм|ваторОв 2. Недос1 ачок устройства заключается в высокой BorpeDtptpcitr (:ёнйя. Цель espejpeieH повышение точности умшжвгеляЧвСгООыг. Цель достигается тем, что умножитель содержит два элемента ИЛИ, два дополвител1лых cnevi ta а дешифратор, причем выходи амплитудных дискриминаторов подклюяеаы ко взводам первого элемента ИЛИ, выход которого подключен к первым входам второго iparrepa и первого дополнитвльного счетчшса, второй вход которого лодк оочен к выходу управляемого делите/рт 4ж:топы, разрядите выходы первого дополнительного счетчика через дешифратор подключены к разрядным входам счетчика, информационный вход которого подключен к выходу элемента И, второй вход которого подключен к выходу второго триггера, разрядные вьтходы первого счетчика через второй дополнительный счетчркпойключены к первому входу в торого элемента ИЛИ, второй вход которого подключен к дешифратора, выход - ко втор1ому входу второго триггера, На чертеже предст лена структурн схема предпагаемого устройства. Цифровой умножитель частоты содержит усилитель 1, амйлитудиые дискриминаторы ЙГЗТэлемент ИЛИ 4, генера-гор 5 импульсов, триггер 6, элемент И 7, дозпоянйтельннй счетчик 8, элемент ИЛИ 9, угфавляемый, дел:йтель 10Г частоты; счетчик 11, дешиф ратор 12, дополнительньтй счечпвк 13, фор мирователь 14 импульсов ввода, триггер 15, вход 16 и выход 17 устройства. Умножитель частоты работает следуюшим образом. При синусоидальном входном сигнале входное воздействие подается на вход 16 усилителя 1, ограничивается, и выходные противофазные напряжения усилителя дискриминируются двумя аналогичными Дискриминаторами 2, 3 (моменты срабатыва- ния которых могут быть совмещены с положительными нуль-«ереходами сигнала). Наличие гистерезиса отпускания дискрими на роров 2, 3 несушественао. Импульсные сигналы через элемент ИЛИ 4 с двойной частотой { 2 f,) поступают на первый вход трнхтера 6, устанавливая его каждым вмпУлъюом в единичное состояние и давая разрешение на прохождение импульСОВ; ньхссжрй частоты { ) с йыхода згенератора 5 Импул1 сов (и качестве кото jporo МОзкет быть использован кварцевый рёнератор с высокой стабильвостью часто ты) через эяеметат И 7 на счетный вход «йчёт-чийов 8 и 11. Счетчик 11 выполнен iK схеме реверсивного, ивмене аие ef-o со 5тойния в сторону увеличения выхойногб кода М иЛЕГ-умёйешенйя дос-шгаетсй сигналами с выходов дешифратора 12. Перё л очеШе на сложеввеипн вычитание определявтхзя знаком pabcofларэваний на частоте i вх TD есть если ,- .. эффициент умножения умножителя, то снгная рассогласования л ; О, н соответствующим сигналом с выхода дешифратора 12 Оё) триг.. гер 6 через элемент ИЛИ 9 сбрасывается, запрещая прохождение Импульсов высокой частоты ( кв) на счетйый вход че-хчиков 8 и ll. Выходной код счетчиа 11 имеет в установившемся режиме остоянное значение (), определяющие оэффициент пересчета управляемого делиеля 10 частоты , где с - коэффициент деления управляемо- го делителя 10 частоты; V- его разрядность. Соответственно - f -iK. ВЫХ с В умножителе осуществляется умножение входной частоты ( вх. в заданное чисйо раз такй образом, что на выходе 17 формируется частота f . изменении входной частоты ( -ви.) нзме- ; няется выходная частота (и,,,,). В этом случате всегда присутствует динамическая; (вд) ошибка прео азования. Требуемое изменение f Bjji)t достигается изменением коэффициента деления с управляемого делителя 10 часШ-Й сПОМОЩЬЮ сче1чик;а 11 0)0 результатам подсчета количества импульсов повышенной частоты ( 2 .щ,,) с вь1ХЪ да управляемого делителя 1О частоты счетчиком 13 за период входаой . частоть. Для обеспечения режима слежения за изменением входной частоты (f ) используются не только результаты рассогласования по частотам. 2f -и 0$ П Z. ./Ilj isbvx , JJ(). -f VM ВЫХ/ 6X . J -n - - --- ,....v.. v.-..-. . . . .- ; .Т.е. N - не только д ,но н 4 gx. i -®М-Ф( - функция двух переменных: сйгнаЛаг рассогласования и входнойчастоты. В йроШвном;Гслучаё не достагается минимальная ошибка умюжения в широком частотном диапазоне (а не только в ассчитайном).. ПрЬИЁвсс слежения за изменением входной частоты (fgji) может быть описан таким образом. Период входной ч ютоты ( ) можно выразить формулой (f 2. / где TKB период следоватшя импульсов генератора 5 (,); KB При изменении периода входной частэ1Ы ошибка воспроизведения первода вмпулъ сами ловышепной частоты будет равна АТ.1, ЛПТ. гае ДИ - количество импульсов повышенной частоты, соответствующее нзмеиеняю периода входной частоты ( ) Данная ошибка быть компенсирована изменением коэффициента деления () управляемого делителя 10 частоты, т.е. ее моясно выразить как Д.Т, П1Г. Acj,, из (2) в (З) можно выразить оребуемрв для компенсации ошибки изменение коэффициента деления (С ) управляемого дели телю 1О частоты . ЕСЛИ изменеше коэффициента деления ( ДЧ. ) определяется только велнч| ой рас согларования С). в случае не зависящей от входной частоты 2 Х то с прюсодом каждого импульса частоты () происходит коррекция по частоте, Относителыолй шаг коррекции, можйо выразигь как , Aq, ВХВХ К т.е. при изменении входной частоты (i точность умножение будет разной непостоянства относительного шага рекцвн ддд разлочны к входных частот, как видао на (5). Постоянство относительного шага коррекпнн достигается нспрпъэрвшвем дополнительного счетчика 8, позволяюпюго изменять коэффициеВГ депёнвя (t) управляемого делителя 1О частоты .... :.. дч sbfconet . С потеким образом, что --- т МОЩЬЮ дополнительного счетчика 6 черев элемент ИЛИ 9 достигается данная щх)« порция изменения Д пропорционально | Так как отношение завн- самость относательнбго тага коррекции по частоте от входной частоты ( -0 ли693373нейна. Поэтому цифровой умножитель сохраняет точность умножения частоты в ши роком диапазоне входных частот, При сравнительно низкой входной частоте уп- равляющее воздействие измесгается на большую величину (код. 1Л), 1к зволяюп1ую более эффективно компенсировать ошибку умножения. При более высокой входной частоте управляюшее воздействие изменя- ечся на меньшую величину, чем достигается меньшая динамическая ошибка. Дополнительный счетчик 8 выпо/щяет функцию ввучренней обратной связи по управлению :Воздействием счетчика 11 на управляемый делитель 10 частоты. Причем дпя эффективного управления достаточно использовать с выхода счетчика И (l« -M-U2 ) старшие разряды ннсгчё ухудасается динамика процесса. При измененнн частоты входного сигнала ( f), например, в сторону возрастания ( f fo-) выходная частота также должна возрасти (-.., -, . ВЬ|1ц такую величину, что JBblX BbtX вых Р -л ВЫХ ВХ Данное изменв1| ие д{ ь хЯРСтигается переключением счётчика 11 на слежение на , время Д -t, необходимое для компенсации рассогласования по частоте, за которое Ни реверсивный счетчик 11 поступит , импульсов, причем Д-t определяется в 9свовном .как сигналом рассогласования { , так и входной частотой (f g ); запрещением прохождения лпульсов с выхода генератора 5 через элемент И 7, сбросом триггера 6 как сигналом (© с дешифратора 12, так и им- пульсом переполнешя дополнительного (яетчика 8. Выходные импульсы с выхода управляемого делителя 1О частоты ( , ) возникают вследствие периода- чеякого пврехюлнения счетчика управляемого делителя 1 О частоты импульсами высокой частоты (f кв выхода генератора 5 импульсов. Ввод часла М в управляемый делитель 10 частоты осуществляется с даойнрй частотой ( -f р,,, ) по отношению к 2{(,, с помощью форШ1рователя 14 импульсов шода. Двойная частота обеспечивает лучшие динт««ичес- кие характеристики устройства. Кроме того, для нормального функционирования умножителя без режима автоколебаний с помощью дешифратора 12 искусственно соз- Йёётся збна йечувс1ВйтельйОс№, определяемая в обшей: случае характерйс-Гйками электронных узлов а диапазоном частот. Такой умножи-гель имеет лучщне статическне в динамические характеристики 6 щйрЬК10М дищШОнё входных частот. Предооженвый цифровой ум) часчоЛз с расщиревным диапазоном вы годно отлачается от прототипа. Qia пегко реализуется на элементах днскретвой тех вики, обладает более высокой точностью умножения частот за счет использования отрипателыной обратаюй связи пс частоте в сочетании с корректирующим воздействием, позволяющим стабилизировать oivносительный шаг коррекции в широком диапазоне частот, и соответствующего выбора зоны нечувствительности. При пра ВИЛЬНО выбранных схемных элементах уст ройс-то позволяет существенно снизить абсолючную и относительную погрешности времяимпульсного преобразования (прибли зительно в К д раз, где К д - коэффиди ент деления делителя частоты прототипа) в широком диапазоне юсодвых частот, а не дгш одной (расчетной) определенной частоты ( д5)- В результате наличия ука аанных достоннстт расширяется сфера использования и функдибйальвме возможности уст йства. ормула изобретен Шфровой умножитель частоты, соя Жащий упрайляеь й делитель частоты, информадаонные взводи кото)эо1х озедйнены с выхода1и4и счетчика, генераторймпульсов, выход «оторого нодклвЗчен к перво ty управляющему входу управляемого делителя частоты, формирователь импульсов входом соединенный с выходом управляе мого делителя частоты и входом первого триггера, выход которого является выходом умножителя частоты, выход формирователя импульсов подключен к управляющему входу управляемого делителя частоты, элемент И, первый вход которого соединен с й 1ходом второго TptctTepa, усилитель, вход которого явлается входом умножителя, выходы усилителя подключе ны ко входам амплитудных дискриминаторов, отличающийся тем, что, с целью повышения точности умножителя ч астоты, он содержит два элемента ИЛИ, два дополнительных счетчика и дешифратор, причем Ш.13ЮДЫ амплитудных дискриминаторов подключены ко входим первого элемента, ИЛИ, выход которого подключен к первым входам второгчэ тт иггера и первого дополнительного счетчика, вХо)1 которого подключен к выходу управ ляемого делителя частоты, разрядные выходы первого дотголнительнозго счетчика через дешифратор подключены к разрядным входам , информационный вход которого подкч Ючен к выходу элемента И, второй вход которого подключен к въгзйэду второго триггера, разрядные выходы первого счетчи через второй дополнительшлй счетчик лодалючены к первому н8:оду второго элемента ИЛИ, второй вход которой подключен к вьгходу дешифратору й-тход - ко вторбму входу второго триг г раГ .; ; ::-:,; v::/.;., . :.. .. Источники информации, йрвйя йле во вникланке при экспертизе 1.Киртайаки Н. В., Дудыкевич В. В., МатЬдаЕг ус тро;Йст а цифрового измерения и инфразайзких частот. Львов, ища т лал1976.. 2,Техника средств связи. Серая Радиойзмерительная техника, вып. М., 1976, с. 96.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1977 |

|

SU691853A1 |

| Следящий умножитель частоты | 1977 |

|

SU732866A1 |

| Преобразователь частоты в код | 1978 |

|

SU744974A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU691877A2 |

| Устройство для интегрирования частотно-импульсных сигналов | 1984 |

|

SU1160444A1 |

| Следящий умножитель частоты | 1979 |

|

SU832556A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU732907A1 |

| Интегратор импульсов | 1978 |

|

SU750508A1 |

| Преобразователь угла поворота вала в код | 1976 |

|

SU661589A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1272507A1 |

Авторы

Даты

1979-10-25—Публикация

1977-06-27—Подача