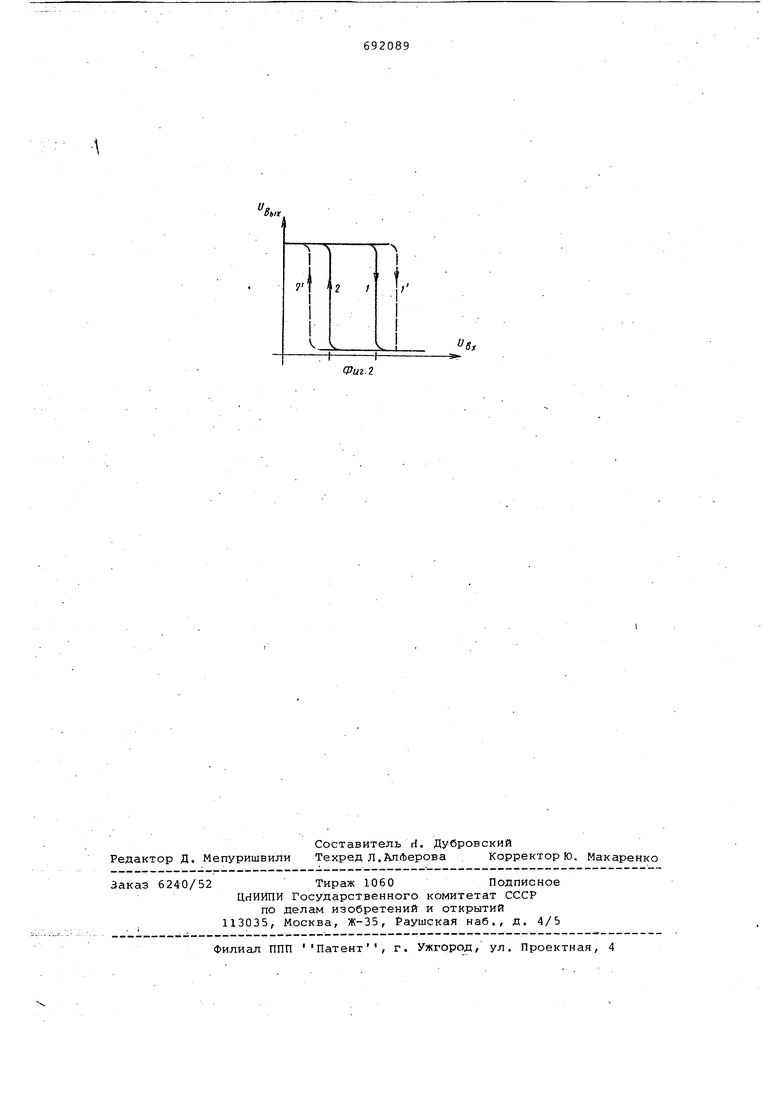

(54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ торов, подложки и истоки .которых, а также подложка первого нагрузочного транзистора подключены к общей шине, затворы нагрузочных транзисторов входногоКаскада подключены к выходной шине элемента, а затворы вход ных транзисторов - к соответствующим входам элемента Г21. Недостаток данного устройства низкая помехоустойчивость. Целью изобретения является повышение помехоустойчивости. . . Для достижения поставленной цели в логический элемент ИЛИ.-НБ на МДПтранзисторах, содержащий последова тельно включенные первый и второй инверторы на транзисторах с дополняю щим типом, пронбдймости и входной ,. каскад, состоящий из двух входных . транзисторов, затворы.которых подклМ чены к .соответствующим в.ходам элемен та,, истоки и подложки - к общей шине а стоки - к .стоку первогО; нагру зочноготранзисторас каналом р-тип.а, йстоку ВТОРОГО нагрузочного .транзис.тора с каналом п-типа и ко .входу пер .в.огои-нвертора, исток и подложка первого нагрузочного транзистора .и сток :второго нагрузоч.ного транзистора под ключе ны к щйне -питания; подлрж.к,а вто рого нагрузочного т ранзистора.прдклю .чена к общей шине, а затворыпервого и второго нагрузочных транзисторов к выходу второго., .инвертора, который является oднoвpё 4eннq выходом элемен та в первыйинвертор-дополнительно введены инвертирующий с каналомп- . типа и нагруз.очный с .кд-.налом р-типа транзй.сторы, подложки которых подклю чеды с.оотве.тственно к общей, шине и .Шине -питан-ия, а э.атворы. - -к з-.атборам транзистЬрбв первого инвертора, сток и.нв-ертирующегО тра.нзистора подключен к истоку- доп-олнительногоинве-ртирующего транзистора, сток которого подк чен к стоку н01грузочн;ого транзистора исток которого подключен к стоку дополнйтельнрго нагрузочного транзистора, исток которого подключен к общей шине. .;. . . .. .. .Устройствопоказано на фиг. .1, Входной каскад состоит из первого 1. и второго 2 входных транзисторо с каналом п-типа и первого 3 с каналом п-типа и второго 4с каналом ртипа нагрузочных транз.исторов. Первый инвертор включает первый 5 и дополнительный 6 с каналами п . типа инвертирующие транзисторы,а также первый 7 и дополнительный 8 нагрузочные транзисторы с каналом р-типа. Второй инвертор состоит из инвертирующего транзистора 9 с каналом п-типа и нагрузочного транзистора 10 с каналом р-типа. Логический элемент включает также шины питания 11, нулевого потенциала 12 и выходную 13. Источки и подложки входных транЗистрров 1 и 2, подложка нагрузочного транзистора 3, истоки инвертирующих транзисторов 5 и ь, а также исток и подложка инвертирующего транзистора 9 присоединены к шине нулевого потенциала 12. Затворы входных транзисторов 1 и 2 соединены с о-оответствующими входами элемента Вх. 1 и Вх.2. Стоки входных (транзисторов 1 и 2 объединены с истоками нагрузочного транзистора 3 со стоком транзистора 4 и с затворами транзисторов первого инвертора5, 6,- 7 и 8.Подложка транзистора 4, а также сток транзистора 3, исток транзистора 4, подложки транизстора7, -истоки и подложки нагрузочных транзисторов 8 и- 10 соединены с шИной питания11. Затворы транзисторов 3 и 4,а также стоки транзисторов второго инвертора 9 и 10 подключены, к .выходной шине. 13. .Сток транзистора 5 объединен с исток:ом транзистора 6..Стоки транзисторов , :б и 7 объединены .с затворами тр-анзисторов 9 и 10. Исток тра:нзис.тора 7 объединен со стоком транзистора 8. Рассмотрим принцип работы предлагаемого лог;ического элемента . , Отметим, что для повышения помехоустойчивости элемент Должен обладать передаточной характеристикой, имеющей петлю гистерезиса; показанную на .фиг. 2. Изменение.- ширины петли гйстерезис-а приводит к изменению поМез с1уст0йч,ивости как по отношению к положительной, так и отрицательной п-Омехам.. - ; :; - , - ;. - Петля гистерезиса может быть получена в схеме,обладающей положительной 6братной связью. Изменение порогов. сраба.ть1вания первой и второй ветви передаточной характеристики с петлей гистерезиса мржно добиться, изменяя Un и Ur,2 Для этого и введены дополнительныетра:Нз.истОры в первый инвертор. - . Напряжение отпирания транзисторов 6 и 7 зависит от разности потенциалов между их подложк:ами и истоками. Для .каждой пары транзисторов 5, б и 7, 8 один из них, в. частности транзистор 8 для пары 7, 8 и транзистор 5для пары 5, 6, создает отрицательную обратную связь для другоготранзистора, в результате чего изменяется напряжение отпирания транзисторов 6и 7. Это приводит к изменению положения передаточной.характеристики ветви 1 и 2 сдвигаются по направлению ветвей l и 2. Увеличение входного напряжения на затворе одного из инвертирующих транз исторов приводит к уменьшению напряжения: в точке соединения истоков транзисторов 3 и 4 со стоками транзисторов 1 и 2 и с затворами транзи торов 5, 6 , 7. и 8. Транзисторы 7 и 8 остаются закры тыми до тех пор, пока йапряжение не изменится до величины Ер - Uop ггде Ер- напряжение питания, а Uop- поро говое напряжение р-канального транзистора... . В результате возникновения отрицательной обратной связи напряжение переключения увеличивается, Следова тельно, для того, чтобы произошло срабатывание логического элемента, входной сигнал долженизмениться на большую величину. Регулировать напряжение переключения, .логического срлемента можно путем увеличения числа-последовательно соединенных транзисторов в первом инверторе.. Действие положительной обратной связи обеспечивается соединением выхода элемента и затворов двух на-;грузочных транзисторов с .каналами п- и р-типов. Действительно, если напряжение на выходе увеличивается, :то это приводит к запиранию р-канального транз.истора 4 и с тпиранию п-канальн6гр транзистора 3v Из принципа работы логического элемента, описанного выше в.идно,, что он обладает повышенно.й помехоустойчивостью и быстродействием. Формула изобретения Логический элемент ИЛИ-НЕ на МДПтранзисторах, содержащий последовательно включенные первый и вторбй инверторы на транзисторах с дополняю цим типом проводимости и входной каскад, состоящий из двух входных транзисторов, затворы которых подключены к соответствующим входам элемента, истоки и подлож.ки - к общей шине, а стоки - к стоку первого нагрузочного транзистора с каналом р-типа, истоку второго нагрузочного транзистора с каналом п-типа и ко входу первогоинвертора, исток и подложка первого нагрузочного транэисто за и сток второго нагрузочного транзистора подключены к шине питания, подложка второго нагрузочного транзистора подключ.енд к общей шине, а затворы первого и второго нагрузочных транзисторов - к выходу второго инвертора, который является одновременно выходом элемента, отличаю, вдийс я тем, что, с целью повышения помехоустойчивости, в /первый инвертор дополнительно введены инвертирующий с каналом п-типа и н&грузочный g каналом р-типа транзисторы, подложки которых соответственно подключены к общей шине и шине питани-я, затворы дополнительно введенных тразисторов подключены к затворам транзисторов первого инвертора, сток инвертирующего транзистора подключен к истоку дополнительного инвертирующего транзистора, сток которого подключен к стоку нагрузочного транзистора, исток которого подключен к стоку дополните.льного нагрузочного транзистора, исток которого подключен к общей ине. Источники .информации принятьае во внимание при экспертизе 1.Авторское свидетельство СССР 405178, Kji. Н 03 К 19/08, 1972. 2.Заяв.ка 2454132/21, л. Н 03 К 19/08, 16,02.77, по котоой принято решение о выдаче авторского свидетельства.

г

г /

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент на мдп-транзисторах | 1977 |

|

SU664297A1 |

| Динамический инвертор на МДП-транзисторах | 1982 |

|

SU1080210A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Дешифратор адреса | 1980 |

|

SU938408A1 |

| Формирователь импульсов | 1980 |

|

SU919062A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| МДП-инвертор | 1990 |

|

SU1780184A1 |

| Ключевой элемент | 1984 |

|

SU1202048A1 |

| Сумматор | 1983 |

|

SU1101863A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

e,

--11Э..

Авторы

Даты

1979-10-15—Публикация

1977-08-03—Подача