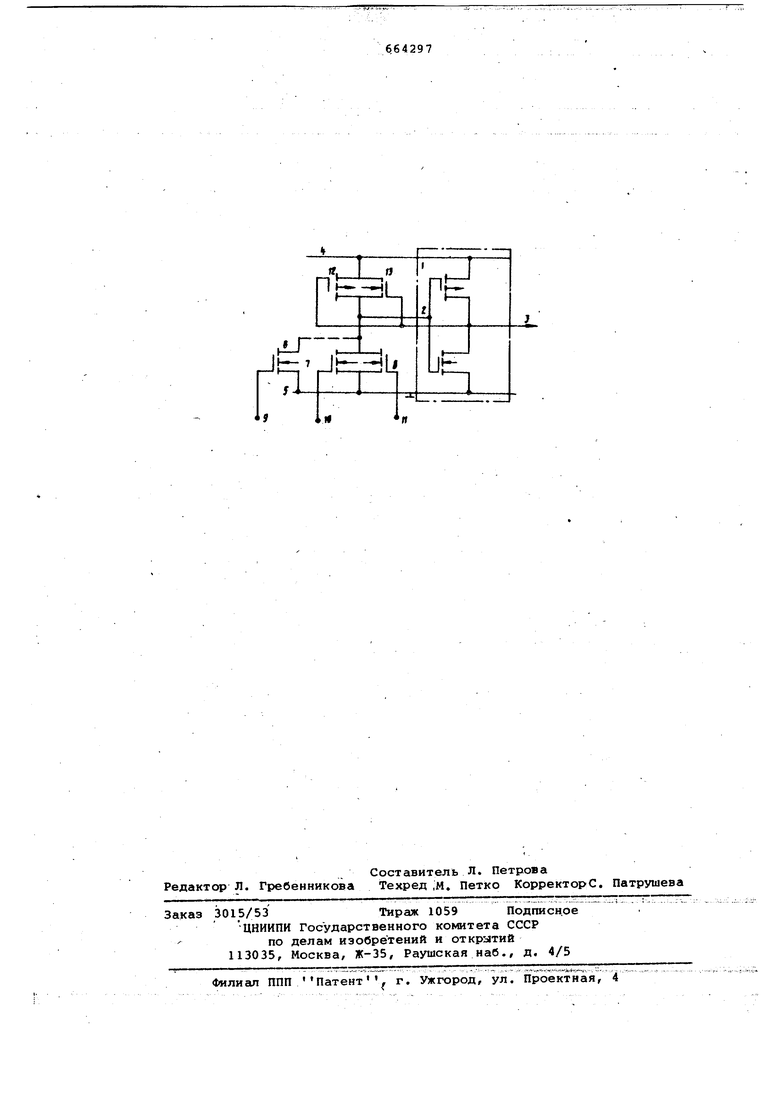

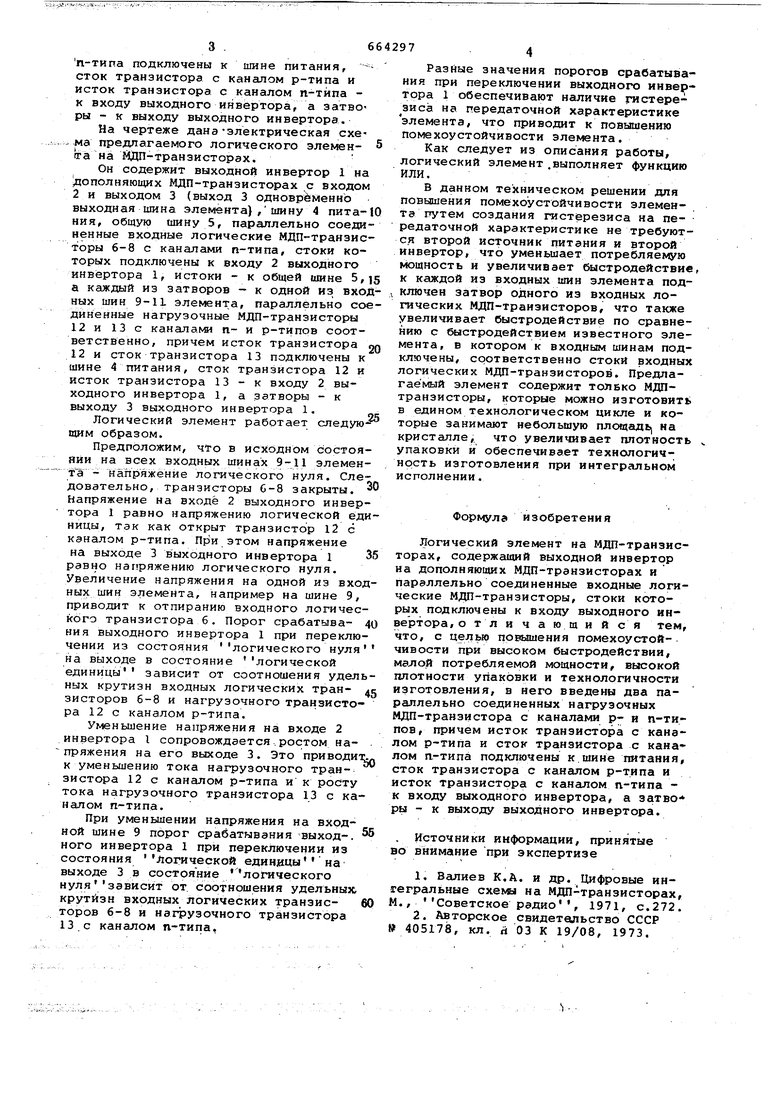

.- -1 Изобретение относится к электронике и вычислительной технике и может быть испольэрвано в цифровых интегральных схемах. Известен элемент ИЛИ-НЕна дополни Ю1ДИХ МДП-транэисторах . Недостатком такого элемента является отсутствие гистерезиса на его передаточной характеристике, что умен шает помехоустойчивость элемента. Известен также ИЛИ на МДПтранзисторах, имеющий передаточную характеристику с гистерезисом для обеспечения повышенной помехоустойчивости и содержащий параллельно соединенные входные логические МДП-транэис торы, резистор и два последовательно включенных инвертора на дополняющих МДП-транзисторах, подключенных к различным источникам питания, причем исток каждого иэ входных логических МДП-транэисторов подключен к Ьдной из входных шин элемента, эатворы входных логических МДП-транзисторов подключены к выходу первого инвертора, а стоки соединены с входом первого .инвертора и череэ. резистор - с общей ши- ной 2. Однако в таком элементе используются два инвертора и два источника питания, что снижает быстродействие и увеличивает потребляемую мощность. Кроме того, элемент содержит линейный резистор большого номинала и большое число транзисторов, которые занимают большую площадь при интегральном исполнении, что приводит к уменьшению плотности упаковки и уменьшению технологичности изготовления из-за наличия pejncTopa, к каждой из входных шин элемента подключен исток одного из входных логических МДП-транзисторов, что ограничивает быстродействие элемента. Цель изобретения - повышение помехоустойчивости при высоком быстродействии, малой потребляемой мощности, высокой плотности упаковки и технологичности изготовления. Для этого в логический элемент на МДП-транзисторах, содержащий выходной инвертор на дополняющих МДП-транзисторах и параллельно .соединенные входные логические МДП-транзисторы, стоки которых подключены к входу выходного инвертора/ введены два параллельйо соединенных нагрузочных МДПтранзистора с каналами р- и п-типов, причем исток транзистора с каналом р-типа и сток транзистора с каналом, n-типа подключены к шине питания, сток транзистора с каналом р-типа и исток транзистора с каналом п-тйпа к входу выходного инвертора, а эатворы - к выходу выходного инвертора. На чертеже данаэлектрическая схв ма предлагаемого логического элеменгга на ЙДП-транэнсторах. Он содержит выходной инвертор 1 на ;дополняю11Ц1х МДП-транзисторах с входом 2 и выходом 3 (выход 3 одновременно выходная шина элемента) ,шину 4 питания, общую шину 5, параллельно соединенные входные логические МДП-транзисторы 6-8 с каналами п-типа, стоки которых подключены к входу 2 выходного инвертора 1, истоки - к общей шине 5, а каждый из затворов - к одной из вход ных шин 9-11 элемента, параллельно сое диненные нагрузочные МДП-транзисторы 12 и 13 с KaHanaNSn п- и р-типов соответственно, причем исток транзистора 12 и сток транзистора 13 подключены к шине 4 питания, сток транзистора 12 и исток транзистора 13 - к входу 2 выходного инвертора 1, а затворы - к выходу 3 выходного инвертора 1. Логический элемент работает следующим образом. Предположим, что в исходном состоянии на всех входных шинах 9-11 элемента - напряжение логического нуля. Сле довательно, транзисторы 6-8 закрыты. Напряжение на входе 2 выходного инвертора 1 равно напряжению логической ед ницы, так как открыт транзистор 12 с каналом р-типа. При этом напряжение на выходе 3 выходного инвертора 1 равно напряжению логического нуля. Увеличение напряжения на одной из вход ных шин элемента, например на шине 9, приводит к отпиранию входного логического транзистора 6. Порог срабатывания выходного инвертора 1 при переключении из состояния логического нуля на выходе в состояние логической единицы зависит от соотношения удель ных крутизн входных логических транзисторов 6-8 и нагрузочного транзистора 12 с каналом р-типа. Уменьшение напряжения на входе 2 инвертора I сопровождается.ростом напряжения на его выходе 3. Это приводи .г«л.,11тг. т .ff , . ..л. .... «.«.«. ...ni .. . к уменьшению тока нагрузочного транзистора 12с каналом р-типа и к рооту тока нагрузочного транзистора 13 с ка налом п-типа. При у1«юньшении напряжения на входной шине 9 порог срабатывания выход-. ного инвертора 1 при переключении из состояния Логической единицы иа выходе 3 в состояние логического нулязависит от соотношения удельных крутизн входных логических транзисторов 6-8 и нагрузочного транзистора 13 с каналом п-типа, Разные значения порогов срабатывания при переключении выходного инвертора 1 обеспечивают наличие гистерезиса на передаточной характеристике элемента, что приводит к повышению помехоустойчивости элемента. Как следует из описания работы, логический элемент .выполняет функцию ИЛИ. в данном техническом решении для повышения помехоустойчивости элемента путем создания гистерезиса на передаточной характеристике не требуются второй источник питания и второй инвертор, что уменьшает потребляемую мощность и увеличивает быстродействие, к каждой из входных шин элемента подключен затвор одного иэ входных логических МДП-траизисторов, что также увеличивает быстродействие по сравнению с быстродействием известного элемента, в котором к входным шинам подключены, соответственно стоки входных логических МДП-транзисторов. Предлагаемый элемент содержит толвко МДПтранзисторы, которые можно изготовит в едином технологическом цикле и которые занимают небольшую площадЬ| на кристалле, что увеличивает плотность упаковки и обеспечивает технологичность изготовления при интегральном исполнении. Формула изобретения Логический элемент на МДП-транзисторах, содержащий выходной инвертор на дополняющих МДП-транзисторах и параллельно соединенные входные логические МДП-транзисторы, стоки которых подключены к входу выходного инвертора/ отли чающи и ся тем, что, с целью повышения помехоустой- чивости при высоком быстродействии, малой потребляемой мощности, высокой плотности упаковки и технологичности изготовления, в него введены два параллельно соединенных нагрузочных МДП-транзистора с каналами р- и п-типов, причем исток транзистора с каналом р-типа и сток транзистора с каналом а-типа подключены к.шине питания, сток транзистора с каналом р-типа и «Я и О ЪГ Э С О U Я П Я U исток транзистора с каналом п-типа к входу выходного инвертора, а затво ры - к выходу выходного инвертора. Источники информации, принятые во внимание при экспертизе 1.Валиев К.А. и др. Цифровые интегральные схемы на МДП-транзисторах, М.,Советское радио , 1971, с.272. 2.Авторское свидетельство СССР 405178, кл. и 03 К 19/08, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент или-не- на мдптранзисторах | 1977 |

|

SU692089A1 |

| Динамический инвертор на МДП-транзисторах | 1982 |

|

SU1080210A1 |

| @ -Триггер с предпочтительной установкой в @ -состояние | 1982 |

|

SU1075380A1 |

| Логический элемент И | 1981 |

|

SU951707A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Буферное устройство | 1977 |

|

SU622204A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

Авторы

Даты

1979-05-25—Публикация

1977-02-16—Подача