(54) АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Микропроцессор | 1977 |

|

SU943734A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1168963A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

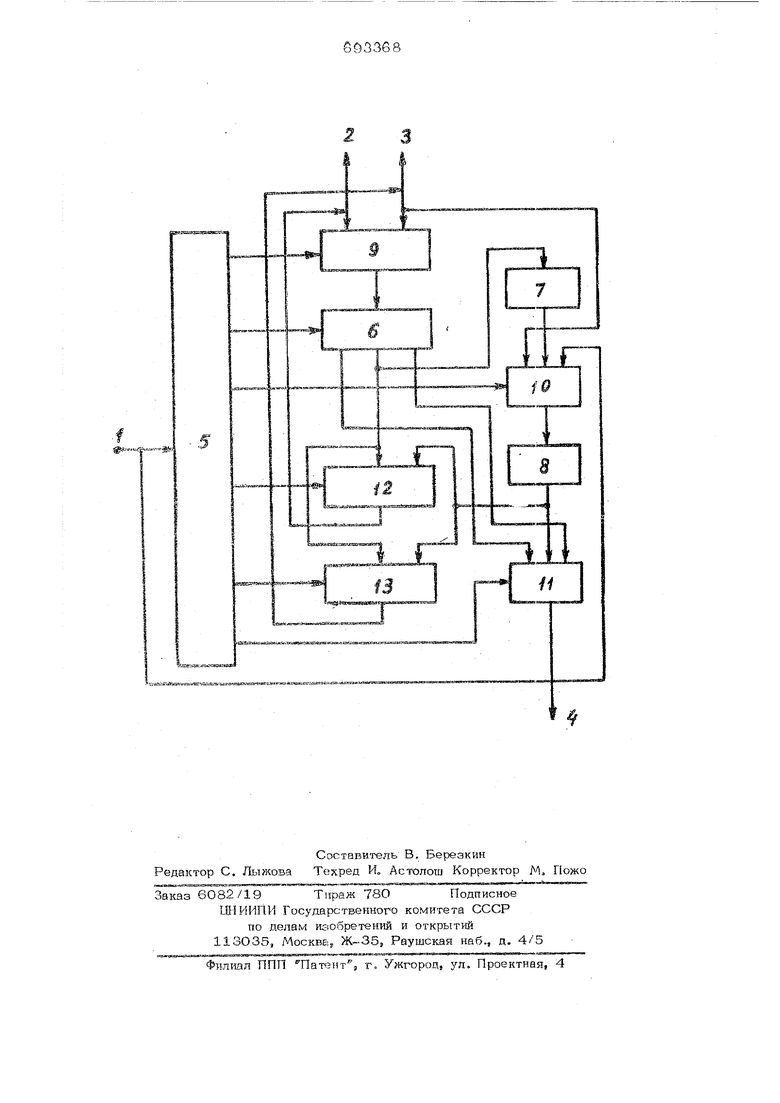

Изобретение относится к областн вычислительной техники и может быть использовано, например, при проектировании микро-ЭВМ на больших интегральных схемах (БИС). Известии арифметико-логические устройства, выполненные в виде отдельных больших интегральных схем l . Наиболее близким по технической сущности к изобретению является устройство, содержащее дешифратор микрокоманд, накапливающий сумматорэ блок формирования признаков, регистр признаков, Т1ервый, второй и третий коммутаторы, причем управляющие ВХОДЫ накапливающего сумматора и коммутаторов соединены с выходами дешифратора микрокоманд, входы которого подключены к шине микрокоманд, шина входа-выхода подключена к nepiBOMy ВХОДУ TiepBoro коммутатора, ВЫХОД KOTopoго подключен ко входу накапливающетх сумматора, выходы которого соединены со входами блока формирования признаков, ВЫХОД которого подключен к первому входу второго коммутатора, выход которого подключен ко входу регистра признаков, ВЫХОД которого соединен с первым вхс дом третьего коммутатора, выход которого соединен с выходной шиной устройств ва 2. Недостатком этого устройства является его ограниченные функциональные возможности. Так, например, устройство не позволяет передавать информацию из накапливающего сумматора на выходную шину, проИдЗводить Изменение адресов микрокоманд по слову, полученному в регистре признаков. Устройство не обеспечивает также восстановление содержимого регистра признаков и не позволяет записывать В регистр признаков часть слова с шины микрокоманд. Цель изобретения - расширение функицональных возможностей за счет обеспечения передачи информации из накапливающего сумматора на выходную шину, изменения адресов микрокоманд по слову, полученному в регистре признаков, восста69новления содержимого регистра признаков и возможности записи в регистр признаков Чисти слова с шины микрокоманд, Кпя достижения доставленной цели в арифметико-логическое устройство, содержащее дешифратор макрокоманд, наканливающий сумматор, блок формирования приз наков, регистр признаков, первый, второй и третий коммутаторы, тфичем управляющие входы накапливакицего сумматора и коммутаторов соединены с выходами дешифратора микрокоманд, входы которого подключены к шине микрокоманд, шина входа-выхода подключена к первому входу первого коммутатора, выход которого подклкяен ко входу накапливаюшего сумматора, выходы которого сое динены со входами блока формирования признаков, выход которптю подклкнен к первому входу второго коммутатора, вырсод которого подключен ко входу регис-рра признаков, выход которого соединен с первьтм входом третьего коммутатора, выход которого соединен с выходной шиной устройства, введены вторая шина вхо да- выхода, четвертый и пятый коммутаторы, перв-ый и второй входы KOTOpfcix соед) нены с выходами соответственно накапливающего сумматора и регистра признаков а выходы соответственно с первой и второй шинами входа-выхода, вторая шина входа-выхода подключена ко вторым входам первого и вторрго коммутатора, третий вход второго коммутатора соединен С ШИНОЙ микрокоманд, вторсй и трет1 / входы третьего коммутатора подключены К выходам накапливающего сумматора. На чертел е представлена блок-схема устройства. Устройство содержит шину 1 микрокомйдн, шины ВХОДИ-ВЫХОДИ 2 и 3, выходную шину 4, дешифратор 5 микрокоманд, накапливаюший сумматор 6, блок формирования прйэнаков 7, регистр признаков 8, коммутаторы 9-13. Вход дешифратора 5 микрокоманд соединен с шиной 1 микрокоманд. Управляюшда входы накапливающего сумматора 6 и комму f« торов 9-13 соединены с выход ми дешифратора 5. Входы первого коммутатора 9 соединены с шинами входа-выхода 2, 3, а выход - со входом суммато ра 6. Коммутатор 9 подключает ту или доугую мину ко входу сумматора 6. Входы блока формирования признаков 7 соединены с выходами сумматора 6. Этот блок ф(1рмируёт првэвакв результата one84рации по содержимому сумматора 6. Выходы блока формирования признаков 7 соединены с одним из входов коммутатора 10, два других входа последнего соедине ны соответственно с шинами 1 и 3, а выход - со входом регистра признаков 8. Комк-тутатор 10 подключает блок признаков, разряды шины микрокоманд или шины входа-выхода ко входу регистра признаков, фиксирующего соответствующую информацию. Входы третьего коммутатора 11 соединены с выходами накапливающего сумматора 6 и регистра признаков, а выход с выходной шиной. Коммутатор передает на эту шину содержимое соответствующих разрядов сумматора 6 и регистра признаков. Входы коммутаторов 12 и 13 соединены с выходами накапливающего сумматора 6 и регистра признаков 7, а ихвыходы соединены соответственно с шинами входа-выхода 2 и 3. Коммутаторы передают на эти шины содержимое накапливающего сумматора 6 или регистра признаков. Арифметико-логическое устройство (АЛУ) предназначено для построения микропроцессов параллельного действия с микропрограммным управлением, АЛУ позволяет Б гаолнять арифметические и логические действия над байтами, поступающими по шинам входа-выхода 2, 3, и one-: раций пересылок между входящими в его состав регистрами и .шинами. Все действия ito приему, пересылке и обработке информации в АЛУ осуществляются управляющими сигналами, формируемыМи дешифраторами микрокоманд 5. Эти сигналы поступают с выходов дешифрато ра 5 на управляющие входы соответствующих функциональных узлов АЛУ. Эти управляющие сигналы вырабатывают дешифратором микрокоманд 5 в соответствии с кодом, поступающим на его вход по шине микрокоманд 1. Накапливающий сумматор 6 под воздействием сигналов, поступающих на его управляющий вход, производит действие над байтами, один из которых содержится в Heiwt самом, а другой поступает с коммутатора 9. Этот коммутатор под воздействием управляющих сигналов передает на вход сумматора б байты с шин 2 или 3. Результат операции (байт) .фиксируется в накапливающем сумматоре б, Содержимое накапливающего сумматора 6 передается через коммутаторы 12 56 и 13 на шины 2 или 3. Эти же KOMivfyra торы передают на те же шины содержимо регистра признаков 8. Блок формирования признаков 7 вырабатывает рад признаков результата опера аии, вьшолняемой сумматором 6, признаки переполнения разрядной ки, переноса из старшего разряда, равенства нулю результата операции. Эти приэ наки фиксируются в четырехразрядном регистре признаков 8 сигналом, подаваеMbiM с дешифратора микрокоманд 5 на уп равляющий вход коммутатора 1О; другие управляющие сигналы, подаваемые на это коммутатор, фиксируют в регистре призна ков 8 содержимое разрядов шин 2 и 1. Слово с регистра признаков 8 может быть передано через коммутатор 11 на четырехразрядную выходную шину 4. При синтезе микро-ЭВМ эта шина может быть соединена, например, с устройством, формирующим последовательность адресов . микрокоманд, и содержимое шины может быть использовано в этом случае для изменения этих адресов., . СигнаАг с дешифратора 5 микрокоманд на управляющие входы коммутатора 11 обеспечивают также передачу на выходную шину 4 содержимого старшей и младшей половин накапливающего сумматора 6. Соединение входа регистра признаков 8 с шинсА 1 микрокоманд через коммутатор Ю позволяет записывать в регистр признаков 8 часть слова с этой шиной, после чего эта часть слова может feiTb передана на шины 2 или 3 входа-выхода и на выходную шину 4 (через коммутаторы 12, 13 и 11). Возможность через коммутатор Ю записывать четырехразрядное слово со второй шиной 3 входавыхода в регистр признаков 8 обеспечивает, например, восстановление содержиХого регистра признаков в тех случ/аях, когда слово с этого регистра (например, в режиме прерывания) &шо записано во Внешнюю память через коммутатор 13 и шину 3 входа-выхода. Обеспечение возможности передачи на выходную шину 4 содержимого накапливающего сумматора 6 позволяет производить изменение адресов микрокоманд по слову, полученному в сумматоре. 68 Все вышесказанное позволяет значительно расширить функциональные возможности АЛУ. Формула изобретения Арифметико-логическое устройство, содержащее дешифратор микрокоманд, накапливаюший сумматор, блок формирования . Признаков, регистр признаков, первый, второй и третий коммутаторы, причем управляющие входы накапливающего сумматора и коммутаторов соед1шены с выходами дешифратора микрокоманд, входы которого подключены к шине микрокоманд, шина входа-выхода подключена к первому входу первого коммутаторе, выход которого подключен ко входу накапливающего, сумматора, выходы которого соединены со входами блока формирования признаков, выход которого подключен к первому входу второго коммутатора, выход которого подключен ко входу регистра приэнаков, выход которого соединен с первым входом третьего коммутатора, выход которого соединен с выходной шиной устрсйства, отл ичающееся тем, что, с целью расщирения функциональных возможностей за счет обеспечения передачи информации из накапливающего сумматора на выходную шину, изменения адресов микрокоманд по слову, полученному в регистре признаков, восстановления содержимого регистра признаков, возможности записи в регистр признаков части слова с шины микрокоманд, в устройство введены вторая шина входа-выхода, четвертый и пятый коммутаторы, первый и второй входы которых соединены с выходами соответственно накапливающего сумматора и регистра признаков, а выходы - соответственно с первой и второй шинами входа-выхода, вторая шина входа-выхода подключена ко вторым входам первого и-второго коммутатора, тертий вход второго коммутатора соединен с шиной микрокоманд, второй и третий входы третьего коммутатора подключены к выходам накапливающего сумматора. Источники информации, принятые во внимание при экспертизе 1.Майоров С. А. и др. Принципы органйзаиии цифровых машин, Л., Машиностроение, 1974. с. 168, рис. 4.56. 2.Патент США N 3745532, кл. 34О-172, 5, 1963 (прототип).

2 3

Авторы

Даты

1979-10-25—Публикация

1977-04-05—Подача