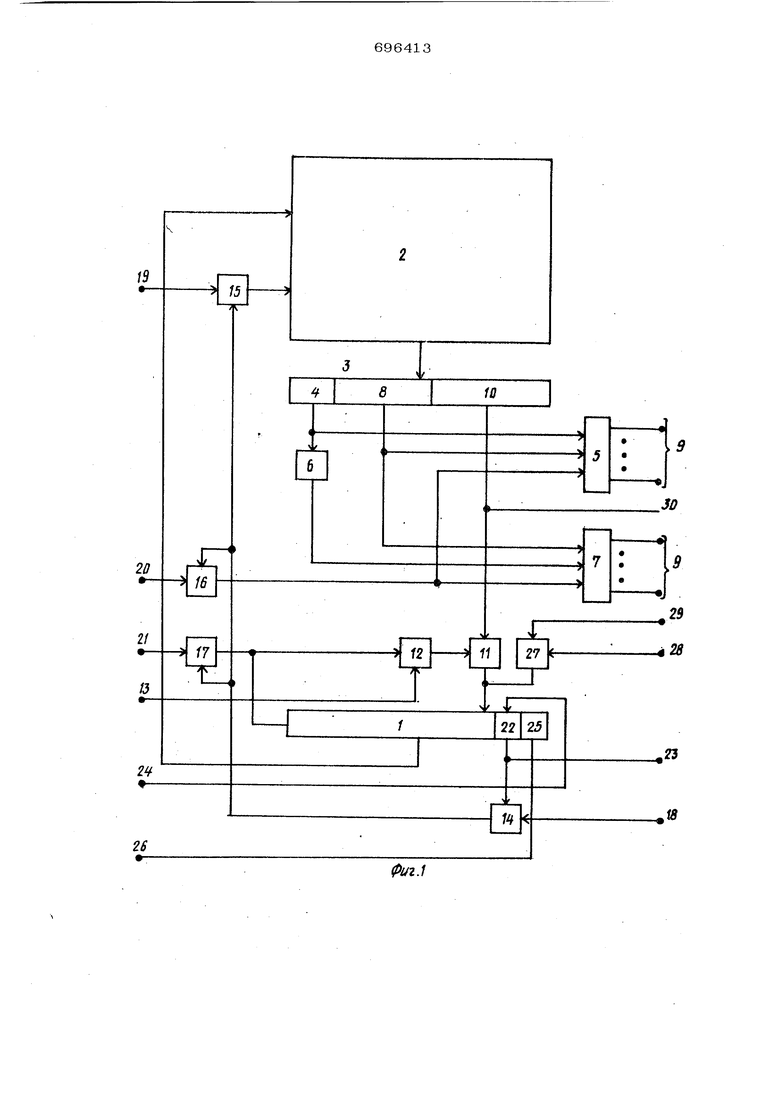

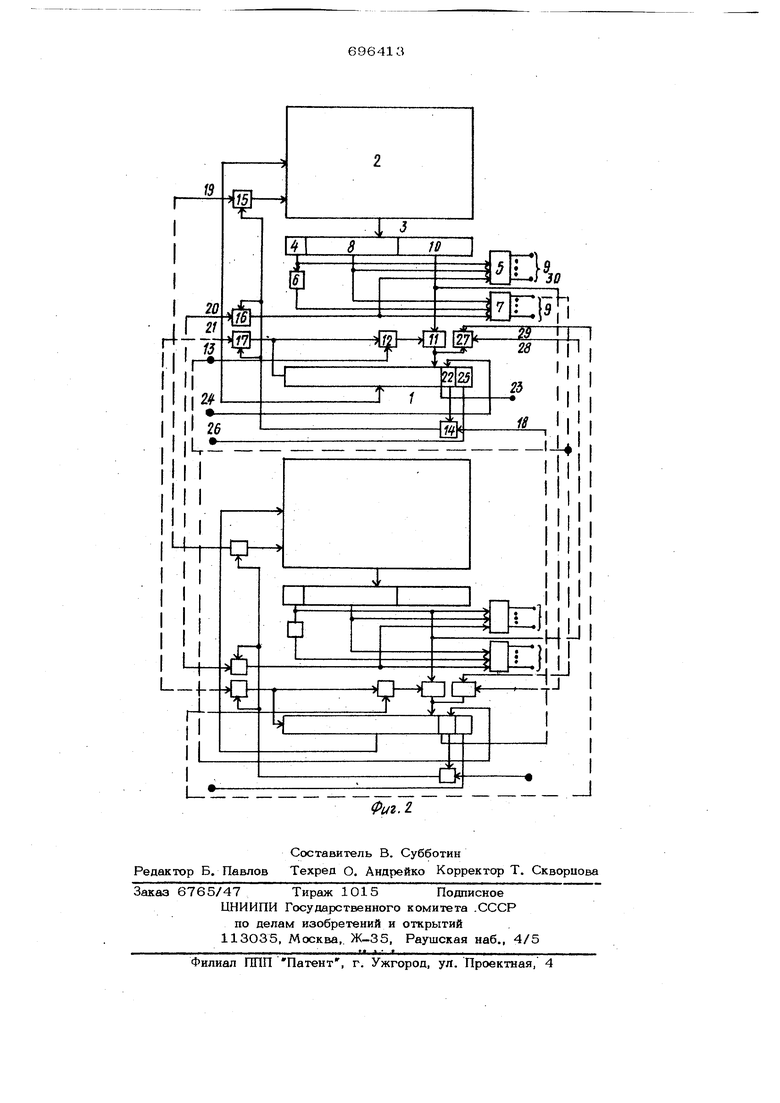

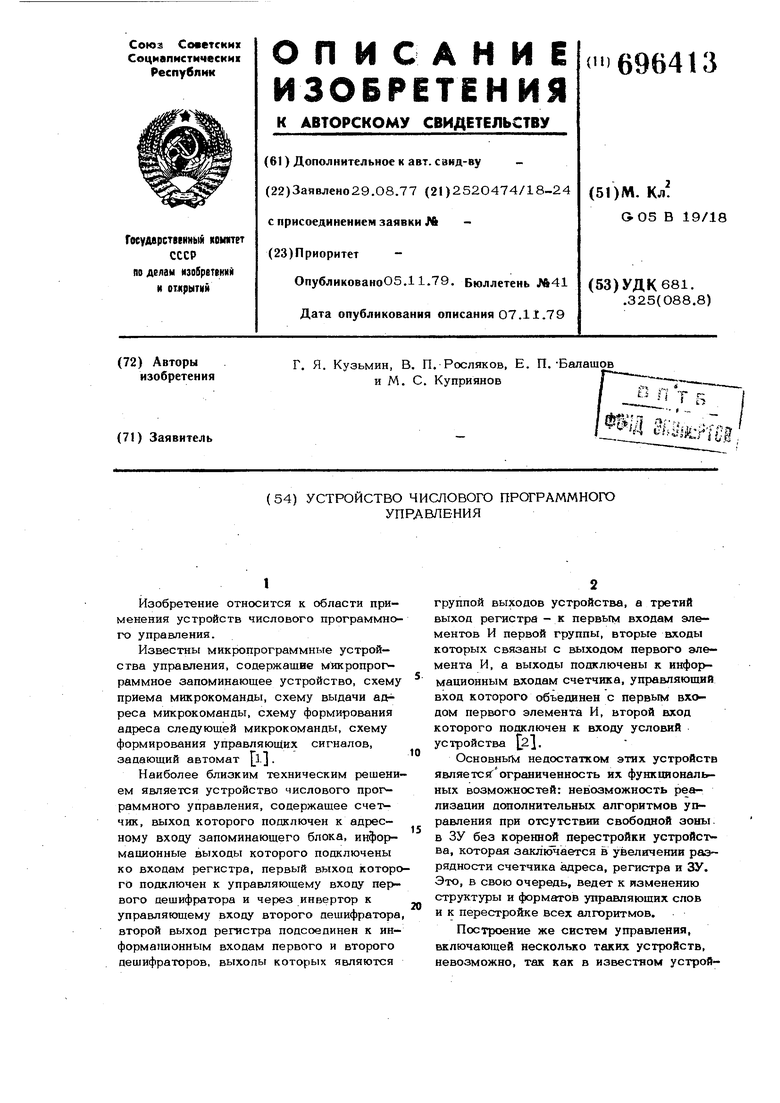

Изобретение относится к области применения устройств числового программного управления. Известны микропрограммные устройства управления, содержащие микропрог раммное запоминающее устройство, схему приема микрокоманды, схему выдачи ад реса микрокоманды, схему формирования адреса следующей микрокоманды, схему формирования управляющих сигналов, задающий автомат р.. Наиболее близким техническим решени ем является устройство числового программного управления, содержащее счетчик, выход которого подключен к адресному входу запоминающего блока, информационные выходы которого подключены ко входам регистра, первый выход которо го подключен к управляющему входу первого дешифратора и через инвертор к управляющему входу второго дешифратора второй выход регистра подсоединен к информационным входам первого и второго дешифраторов, выхопы которых являются группой выходов устройства, а третий выход регистра - к первым входам элементов И первой группы, вторые входы которых связаны с выходом первого элемента И, а выходы подключены к информационным входам счетчика, управляющий вход которого объединен с первым входом первого элемента И, второй вход которого подключен к входу условий устройства 2., Основные недостатком этих устройств является ограниченность их функциональных возможностей: невозможность реализации дополнительных алгоритмов управления при отсутствии свободной зоны. в ЗУ без коренной перестройки устройства, которая заключается в увеличении разрядности счетчика адреса, регистра и ЗУ. Это, в свою очередь, ведет к изменению структуры и форматов управляющих слов и к перестройке всех алгоритмов. Построение же систем управления, включающей несколько таких устройств, невозможно, так как в известном устройстве отсутствуют элементы и внешние шины, которые обеспечивали бы взаимо- пейотвие данных устройств в системе и реализацию, тем самым, заданных алгоритмов. Цель предлагаемого изобретения - расширение класса решаемьк задач за счет подключения. . Для этого устройство содержит второ третий, четвертый и пятый элементы И и вторую группу элементов И, причем первый вход второго элемента И подключен к инверсному выходу второго разряда счетчика. Второй вход второго элемента И подсоединен к первому управляю щему входу устройства, а выход - к пер вым входам третьего, четвертого и пятого элементов И, вторые щсоды каждого их которых .подключены к соответству щим тактовым входам устройства, а выходы подсоединены к управляющему входу запоминающего блока, управляЕощим входам j первого и второго дешифраторов и упраБЛЯющему входу счетчика, соответст венно. Прямой выход второго разряда счетчика подключен ко второму управляю щему входу устройства, нулевой вход второго разряда счетчика - к третьему управляющему входу устройства, прямой выход первогО разряда счетчика - к четвертому угфавляющему входу устройст ва. Первые входы элементов И второй группы связаны с первой группой входов передачи устройства. Вторые входы подгключены к пятому управляющему входу устройства , а выходы - к информационным входам счетчика, причем второй выход регистра подключен ко второй группе входов передачи устройства. Такое введение в известное устройст- во новых гэлементов и организация их . связей обеспечивает расширение набора реализуемых алгоритмов путем гфостого подключения такого же устройства, в запоминающем устройстве которого разм щены недостающие алгоритмы. На фиг. 1 приведена структурная схема предлагаемого устройства для числового программного управления (модуля), а на фиг. 2 - схема соединений с другим аналогичнРым устройством (модулем). Предлагаемое устройство (фиг. 1) содержит счетчик 1, часть выходов которого подключена к адресным входам запоминающего блока 2, информапнонные выходь которого подключены ко входам регистра 3, первый разряд 4 которого подключен к управляющему входу первого дешифратора 5 и через инвертор 6 к управляющему входу второго дешифратора 7, одна часть 8 разряда регистра 3 подключена к информационным входам де- щифраторов 5 и 7, выходы которых подключены к группе выходов устройства 9, а другая часть 10 разрядов регистра 3 - к первым входам группы элементов И 11, вторые входы которых подключены к выходу элемента И 12, а выходы подключены к информационным входам счетчика 1. Управляющий .вход счетчика подключен к первому Bxoziy элемента И 12, другой вход которого подключен к Bxocsy 13 условий. Устройство содержит также четыре элемента И 14, 15, 16, 17, причем первый элемент И 14 подключен к инверсному выходу второго разряда счетчика 1, второй вход схемы И 14 подключен к управляющему входу 18, а выход к первым входам элементов И 15, 16, 17, вторые входы которых подключены соответственно к тактовым входам 19, 20, 21, а выходы - к управляющему входу запоминающего блока; управляющим входам дещифраторов 5 и 7 и управляющему входу счетчика 1, прямой выход второго разряда 22 которого погцслючен к управляющему входу 23, нулевой вход второго разряда 22 - к управляющему входу 24, прямой выход первого разряда 25 - к управляющему входу 26. Первые входы введенной дополнительной группы элементов И 27 подключены к первой группе входов 28 передачи,, вторые входы 27 групп подключены к управляющему входу 29, выходы - к информационным входам счетчика 1, а выходы части 1О разрядов регистра 3 подключены ко второй группе входов 30 передачи. Предположим, что в одном устройстве, например, в верхнем, (фиг. 2) в исходном состоянии разряды 22 и 25 счетчика установлены в нулевое состояние, а в другом устройстве - в одиночное и нулевое соответственно. Из этого следует, что функция управления выполняется верхним на чертеже устройством, так как в нем разрешено прохождение сигналов по тактовым шинам через элемент И 15, 16, 17. Цикл работы устройства составляет три такта и происходит под действием сигналов, подаваемых на тактовые входы 19, 2О, 21. В первом такте производится считываг ние микрокоманды (МК) по адресу, установленному на счетчике 1, на регистр 3 при подаче сигнала на тактовый вход 19. Сигнал проходит чеоез открыты элемент 15, поступает на управляющий вход запоминающего блока и является сигналом чтения. Во втором такте производится выполнение микроопераций, проверка логических условий, а также передача управления соседнему сверху или снизу устройству/ Если первый разряд регистра, а также последний и предпоследний разряды равны нулю, то происходит выполнение микроопераций. Это достигается подачей части 8 разрядов регистра на дешифратор 7-, выходы которого подключаются к функциональным блоком системы управления. Если первый разряд регистра равен , поЬледний разряд - , а предпоследний О, то происходит передача управления соседнему снизу устройству. Это достигается передачей части 10 разрядов из регистра 3 верхнего устройства через входы 29 и 30 передачи, группу 27 элементов И на информационные входы счетчика 1. Для обеспечения такой передачи в часть 8 разрядов регистра должна кодировать микрооперацию, при которой возбуждается выход дешифратора 7, подключенный к управляющему входу 29 нижнего устройс1 ва и входу 13 условий верхнего устройс ва. Часть 9 разрядов регистра, передавае мая на счетчик 1 нижнего устройства, является адресом начала алгоритма, подлежащего реализации и размещенного в запоминающем блоке нижнего устройства. Если первый и последний разряды регистра равны О, а первый и предпоследний.Д, то происходит передача управления соседнему сверху устройству аналогичным образом, т.е. каждое устройство может передавать управление двум соседним устройствам. Если первый разряд регистра равен , а последний и предпоследний О, то происходит анализ условий, путем подачи кода условий на дешифратор 5, вь1ходы которого подключены к cooi ветствующим схемам функциональных бло ков, производящим анализ условий. Остал ные сочетания значений первого, предпос леднего и последнего разрядов в устройс ве не используются. В третьем такте производится добавление к содержимому счетчика 1, если во втором такте выполнялась микрооперация. Ьсли проверялась условно, значение которого поступает на вход 13, то происходит добавление и передача Части разрядов микрокоманды на информационные входы счетчика 1 при emiHOTHOivi значении условия и только до.бавление при нулевом значении условия. Если во втором такте производилась передача управления соседнему снизу устройству, то часть 10 разрядов регистра передается на счетчик 1, в результате чего разряд 25 устанавливае-рся в 1, это приводит к установлению в О разряда 22 счетчика нижнего yclp-, ройства, что закрывает элемент И 14 верхнего устройства и открывает такой же элемент 14 нижнего устройства, обеопечивая прохождение тактовых сигналов через элементы 15, 16, 17 нижнего ус-рррйства и считывание микрокоманды по адресу, переданному из верхнего устройств ва. Если производилась передача соседнему сверху устройству, то аналогичным образом устанавливается в 1 разряд 22, что приводит к запрещению прохождения тактовых сигналов в устройстве, передающим угфавление и разрешение прохождения сигналов устройства, принимающем управление. В дальнейшем цикл работы предлагаемого устройства повторяемся. Таким образом, предлагаемое устройство обеспечивает расширение набора реализуемых алгоритмов, путем простого подключения такого же устройства, в запоминающем блоке которого размешены недостающие алгоритмы. При этом в нужных местах реализуемых алгоритмов помещаются микрокоманды, обеспечивающие передачу управления в соседнее сверьху или снизу устройство, что позволяет также реализовать один алгоритм путем объединения его частей, размещенных в разных запоминающих блоках. Передача управления может использоваться также при отказе функциональных блоков системы управления, что требует перевода системы на новые алгоритмы функционирования, которые удобно размещать в другом ЗУ. Предлагаемое устройство для числового nporpaMivfHoro управления способствует повышению однородности системы, что отвечает требованиям больших питательных схем и увеличивает ее надежность. Формула изобретения Устройство числового программного управления, содержащее счетчик, выход 7e которого подключен к адресному входу запоминающего блока, информанионньге выходы которого подключены ко входам регистра, первый выход которого подключен к управляющему входу первого дешифратора, и через инвертор к упрйвляющему входу второго дешифратора, второй выход регистра подсоединен к информационным входам первого и второго дешифраторов, выходы которых являются группой выходов устройства, а третий выход регистра - к первым входам элементов И первой группы, вторые входы которых связаны с выходом первого элемента И, а выходы подключены к информационным входам счетчика, управляющий вход которого объединен с первым входом первого элемента И. второй вход которого подключен к входу условий уст ройства, отличающееся тем что, с целью расширения класса решаемы задач, оно содержит второй, третий, чет вертый и пятый элементы И и вторую группу элементов И, причем первый вход второго элемента И подключен к инверсному выходу второго разряда счетчика, второй вход второго элемента И подсоединен к первому управляющему входу устройства, а выход « к первым входам третьего, четвертого и пятого элементов И, вторые входы каждого из которых .48 подключен. к соотве1х:т15, тактовык входам устройства, а выходы подсоединены к управляющему входу запоминающего блока, управляющим входам первого и второго дешифраторов и управляющему входу счетчика, соответственно, прямой выход второго разряда счетчика подключен ко второму управляющему входу устройства, нулевой вход второго разряда счетчика - к третьему управляющему входу устройства и прямой выход первого: разряда счетчика - к четвертому управляющему входу устройства, первые входы элементов И второй группы связаны с первой группой входов передачи устройства, вторые входы подключены к пятому управляющему входу устройства, а выходы - к информационным входам счетчика, причем второй выход регистра подключен ко второй группе входов передачи устройства. Источники информации, принятые во внимание при экспертизе 1.Кравцов Л, Я., Черницкий Г, И.; Проектирование микропрограммных устройств управления. Л., Энергия, 1976, с, 51. 2.Майоров С, А., Новиков Г. И. Принципы организации цифровых машин. Л., Машиностроение, 1974, с. 217.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство микропрограммного управления | 1981 |

|

SU985788A1 |

| Микропрограммное устройство управления | 1980 |

|

SU898431A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

Авторы

Даты

1979-11-05—Публикация

1977-08-29—Подача