(54) ПРЕОБРАЗОВАТЕЛЬ ПРЯМОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь прямого кода в дополнительный | 1977 |

|

SU748406A1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Многоканальный измеритель временных характеристик последовательности дискретных сигналов | 1987 |

|

SU1442971A1 |

| "Генератор чисел в кодах "золотой" пропорции" | 1989 |

|

SU1711143A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

1 ,

Изобретение относится к области абтоматики и цифровой вычислительной техники и может быть использовано при построении вычислительных устройств.

Известен преобразователь прямого кода в дополнительный, содержащий триггерный регистр, группы вентильных элементов пля установки входного кода, группу вентильных элементов, входы которых соединены с выходами триггеров регистра l.

МедЬстапком известного устройства является его сложность и относительно низкое быстродействие, связанное с необходимостью установки входного кода, после которой следует собственно преобразование.

Наиболее близким техническим решением к данному является йреобразователь, содерткаший разрядный триггерный регистр, первые установочные входы триггеров которого соединены с соответствующими шинами ввода прямого значения, (tb2) элементов ИЛИ, группу

элементов И, входы которых нодключе- ны к выходам триггеров регистра ..

Недостатком известного преобразователя является относительно низкое быстродействие, связанное с необходимостью задержки преобразования на время первоначальной установки входного кода в регистр.

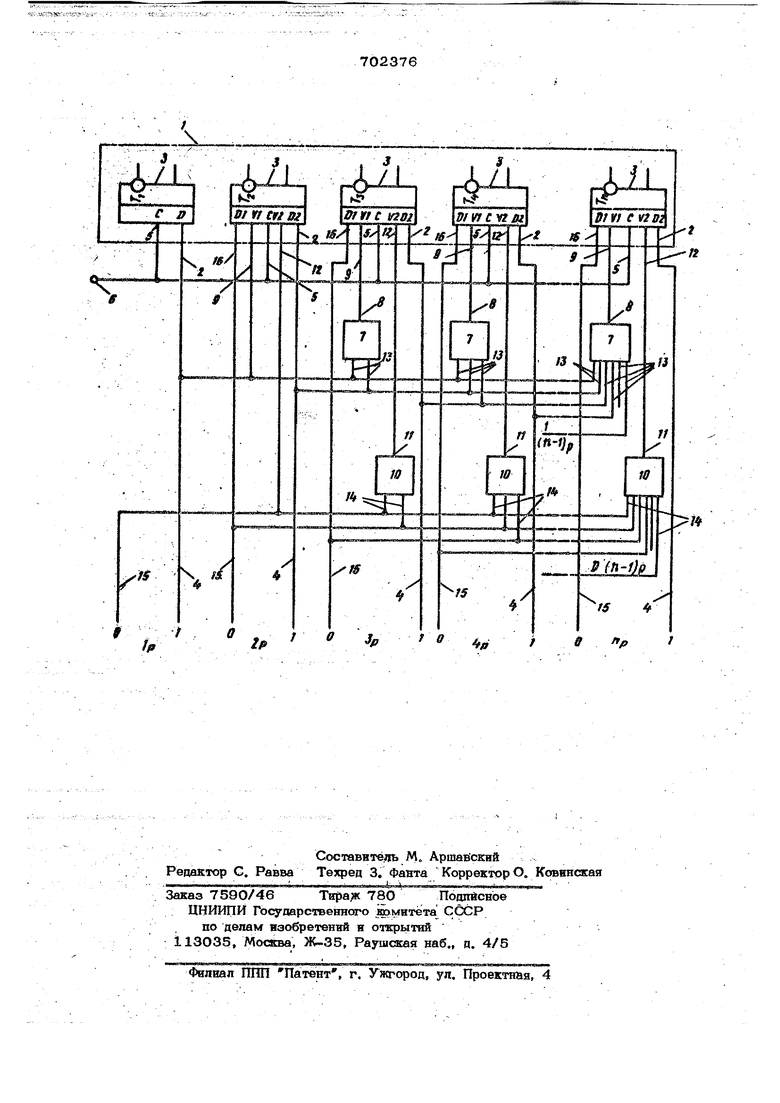

Целью предлагаемого изобретения является сократцение времени преобразования. Это достигается тем, что преобразователь содержит (И-2) элементов И, выходыэлементов ИЛИ соединены с первыми разрешающими входами триггеров с З-го по кь-ый разряд, выходы элементов И соединены с вторыми разрешающими вя:одами триггеров З-го по п-ый разряд,-шина ввода прямого значения 1-го разряда () соединены со входами элементов ИЛИ во всех разрядах старше i-го, шина ввода инверсного значения п-го разряда соединена со входами элементов И во всех разрядах старше i-го, первый и второй разрешаЙ Шйе входы триггера второго разря- ; дй соединены с шинами ввода прямого и Й1шерсного значений мпадщего разряда соответственно, вторые устййоёо с входы триггеров со 2-го соединены б шинами ввода инверсного значения соо-гаетствугопгах разрядов, синзфовходы всех триггеров регистра соединены с управляющей шиной преобразователя, На че|)Теже представпенй схема преобразователя прямого кода в дополните НЫЙ.- ;. . . . . - - .V. Преобразователь прямого кода в дополнительный содержит }i-разрядный триггерный регистр 1, йёрвые установочные входы 2 (входи Dg) tpiirrepoiB 3 Которого подключены к соответствую щим шинам 4 ввода прямого зиаченияГ а их синхровходы 5 (входы С) подключены к угфавлякяцему входу 6 преоб разбвателя, п- Я элементов ИЛИ 7, бы.ходы 8 которых соответственно подклн чбны к первым разрешающим входам :9 (вхоДйУ) триггеров с 3-го по О-ый разряд. Я- 2 элементов И 10, выходы 11 которых соответственно подключены ко вторым разрешающим бходам 12 (входам V2) триггеров 3 с 3 по h-й разряд, входы 13 элементов ИЛИ 7 и входы 14 елементов И 10 1ЮпкШ& чевы соотьетстеенно к шинам 4 да йрямого значения и.к шинам 15 ШОда инверсного значение предыдущ1а х разрядов, первый разрешающий вход 9 и второй разрешающий вход 12 2-г6 триггера 3 подключены соответственно к шине 4 ввода npaMoSo значения к к шине 15 вывода инверсного значеткня младшего разряда, вторые установочные входы 16 (входы Т31) со 2-г6 по /Й-й ipmrepoB 3 йОдкййЧёшл к соответствующим шинам 15 ввода йнверб. ного значения. . ,;; , Преобразователь работает следующи образом. Прямое и обратше значение парафазнб представленного иСходногоШда, Который должен быть преобразован, в виде соответствующих логических уровней подается через шины 4 ввода прямого значения и шины 15 ввода ннёёрснвго зйачеийя на первые установочные входы 2 и Вторйё установочные 1входы 16 триггеров 3. В зависимости от того, на какой из разрешающих входов триггеров 3 поступит ёдиш чный, то есть разрешающий логический

которой на первый разрешающий вход 9 подготавливаетзавись обратного значения даннсго разряда исходного- кода в соответствующий триггер 3. Запись прямых или обратных значений преобразуемого кода в соответствии с требованиями закона преобразования прямого уровень, будет подготовлена запись в соответствующий триггер 3 или. пря мого пли обратного значения соотвегствуютцего разряда исходного кода. Так, если уровень логической единипы пазту- . пит на первый разрешающий вход 9, то будет подготовлена запись в триггер 3 обратного значения данного разряда ио-. хрдного кода, так как вход 9 разрешает запись в 3 состояния второго установочного входа 16, соединенного с шиной ввода инверсного аначе ния 15. ЕСЛИ же логическая единица поступит на второй разрешающий вход 12, то этам будет подготовлена запись в триггер 3 прямого значения данного разряда исходного кода, так как вход 12 разрешает запись в триггер 3 соСТОЯНИЯ первого установочного вхош 2, соединенного с шиной 4 ввода П|:1я мого значения. В зависимости от конкретного значения преобразуемого кода логическая единица поступит на вторые .разрешающие входы 12 Tex TpgiTepoBV 3, по отношению к которым все предшествующие, более младшие разряды исходного кода содержат лсггические нули, В этом СЛ5чае все входы 14 элемента И 10 в таком разряде преобразователя будут находиться под йотенййалом логической единипы, что вызовет.появление единичного логического на выходе 11 соответствуюихего элемента И 10 и поступление его на второй разрашающий вход 12. При этом ни на одном из входов 13 элементов ИЛИ 7 в тех же разрядах не будет ни одйой единида, следствием terd яййтСя появление нуля на выходе 8 элемента ИЛИ 7, поступление которого на первый разрешающий вход 9 блокирует возможность записи в триггер 3 состояния второго установочного вхо да 2, соединенного с соответствующей шиной 15 ввода инйерсного значеш1я. Во всех остальнь х разрядах преобразог вате1ю, по отношению к которым хотя бы один из болёб мпадших разрядов исходного йода содержит единицу, на выходе 8 элемента ИЛИ 7 будет иметь место логическая единица, поступление

(цополиительного) кода в до толнительный (прямой) код в; триггеры 3 триггерного регистра 1 производится под воздействвем импульса управляющей частоты, подаваемого через управляющий вход 6 преобразователя на счетные входы 5 всех триггеров 3. В самый младший разряд всегда будет производиться запись прямого значения младшего разряда преобразуемого кода.

Таким образом, преобразование прямого кода в дополнительный я дополнительного кода в прямой осуществляется, в течение одного такта управляйте ей частоты вместо двух тактов, необходимых для выполнения, той же операции в известных устройствах.

Формула изобре, т

е н и я

Преобразователь прямого кбда в дополнительный, содержащий ц-разрядный трйггерный регистр, первые установочные входы триггеров которого соединены с соответствующими шинами ввода прямого значения Л У1-2) элементов ИЛИ, отличающийся тем, что, с целью сокращения времени преобразования, он содержит П г-2 элементов

702376

И,ВЫХОДЫ элементов ИЛИ соединены с первыми разрешающими входами тригге ров с 3-го по .ч-ый разряд, выходы элементов И соединены со вторыми раз- решающими входами триггеров с З-го по , h-ый разряд, шина ввода прямого значения i-го разряда () соединена со входами элементов ИЛИ во всех разрядах старше , пшна ввода инверсного значе1шя i -го разряда соединена со входами эпементов И во всех разрядах старше т-го, первый и второй разреша.ющие входы триггера второго разряда соединены с шинами ввода прямого и инверсного зН1ачений младшего разряда соответ ственно, вторые установочные входы триггеров со по И-ьтй соедипепы с шинами ввода инверсного значения соответствующих разрядов, синхровходы всех триггеров регистре соединены с управляющей шиной преобразователя.

Источники информации, принятые во внимание при экспертизе

№ 185548, кл, G06 F 5/02, 1966.

Авторы

Даты

1979-12-05—Публикация

1977-07-14—Подача