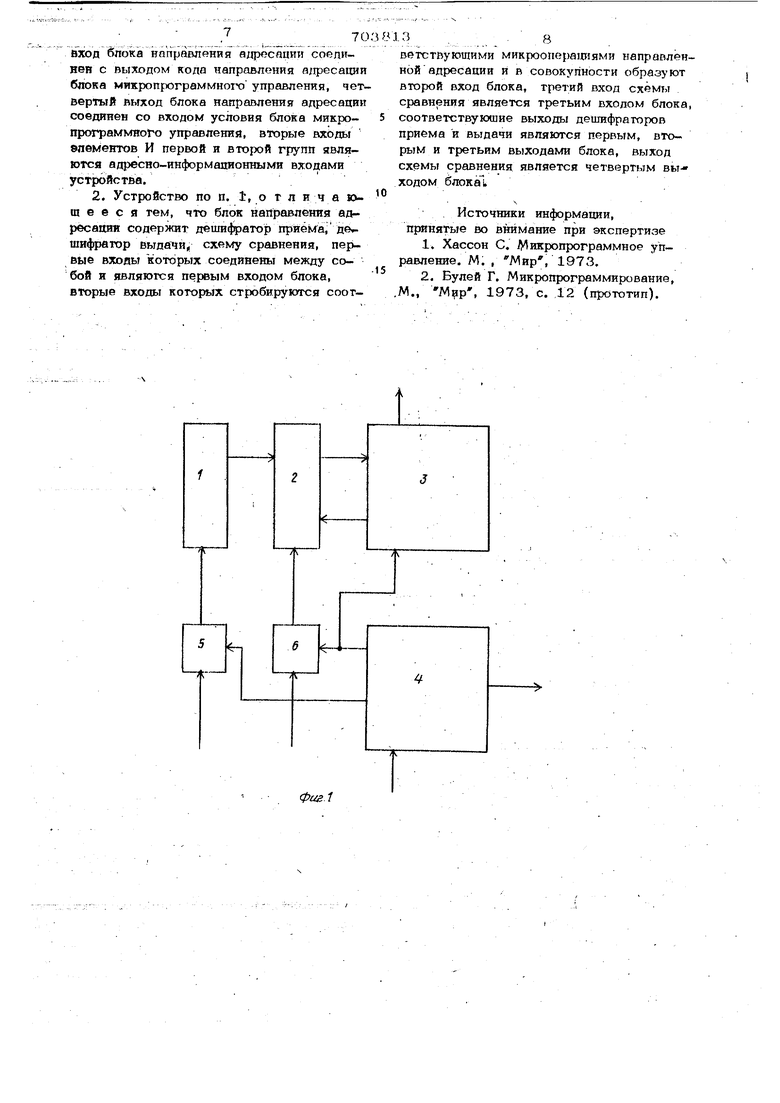

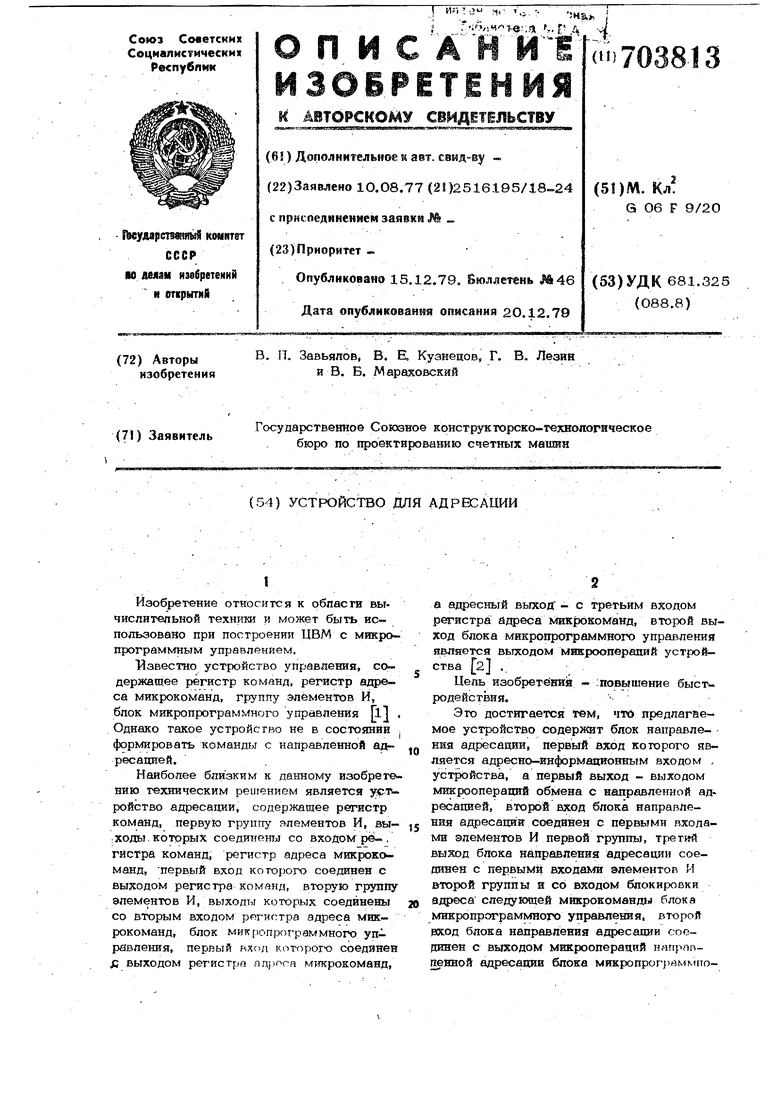

Изобретение относится к области вычислительной техщпот и может быть использовано при построении ЦВМ с микропрограммным управлением. Известно устройство управления, содержащее регистр команд, регистр адреса микрокоманд, группу элементов И, блок микропрограммного управления Г Однако такое устройство не в состогшии формировать команды с направленной адресацией. Наиболее близким к данному изобрете нию техническим решением является усРройство адресации, содержащее регистр команд, первую группу элементов И, вы- ..ходы, которых соединены со входом ре-, гйстра команд, регистр адреса микрокоманд, первый вход которого соединен с выходом регистра команд, вторую группу элементов И, выходы которых соединены со вторым входом регистра адреса микрокоманд, блок микропрограммного уп- рйвления, первый вход которог-о соединен К выходом регистра nujioca микрокоманд, а адресный выход - с третьим входом регистра адреса мик|Х)Команд, второй выход блока микропрограммного управления является выходом микроопераций устройства 2 , Цель изобретённая - ;повышение быстродействия.Это достигается тем, чти предлагаемое устройство содержит блок направления адресации, первый вход которого является адресно-информационным входом , устройства, а первый выход - выходом микроопераций обмена с направленной адресагщей, второй вход блока направления адресации соединен с первыми входами элементов И первой группы, третий выход блока направления адресации соединен с первыми входакга элементов И второй группы я со входом блокировки адреса следующей микрокоманды блока микропрограммного управления, второй исод блока направления адресации соединен с выходом микроопераций наггрпппенной адресации блока микропрогрймм то- 37О го управления, третий вход блока направ пёния йдресадйй соединен с выхо домко- данаправленная адресами блока микропрограммного управления, четвертый выход блока направления адресации соединен со входом условия блока микропрограммнЬго управления, вторые входы элемен трв И ,первой и второй групп являются . йдресно-информационнь7ми входами ус т йства, а также тем, что блок направления адресации содержит дешифратор приема, дешифратор выдачи, схему сравнения, йервые входы которых соединены между собой и являются первым входом блока, вторые входы которых стробируются соответствующими микрооперациями направленной адресация и в совокупности образуют второй вход блока, третий вход схемы сравнения является третьим входом .1блока, соответствующие выходы дешифраторов приёма и выдачи являются первым, и третьим выходами блока, выхо схёМы сравнения является четвертым выходом блока,. На фиг. 1 представлена блок-схема устройства; на ф11г. 2 - блок-схема блока направления адресации, которые содер жат регистр команд I, регистр адреса микрокоманд 2, блок микропрограммного управления 3, блок направления адресации 4,первую и вторую группы элементов И 5,6, дешифратор приема 7, дешифратор выдачи 8, схему сравнения 9. Устройство построено в расчете на то Ч1х в системе команд машины имеются спеинапьные гсо манды с направленной ад.ресациёй йпбрандоб, аи состав микрокоманды дпя реализаций этих команд введены три микрооперации: прием информа- НИИ в устройствос., его адресно-информационного; входа по направлению, определяе мому направленной адресацией, выдача информации из устройства на его адресноинформационный выход по направлению, определяемого направленной адресацией, анализ направления ащюсации, причем микрооперации анализ направления аа, ресации в мтсрокоманде соответствует код направление адресации. Выход микроопераций направленной адресации блока 3 микропрограммного управления представляет собой ймеяко эти микрооперации Выход кода напр авления адресации блока 3 микропрограммного управления предназначен дпя передачи на анализ в блок 4 направления адресации кода напдзавление адресапии из мик}Х)Команды для 34 сравнения с соответствующим кодом на адресно-нн(|хэрмационном входе блока 4, Четвертый выход блока 4 предназначен для передачи результата сравнения из блока 4 в блок 3 для выработки адреса следующей микрокоманды, в зависимости от результата сравнения. Примером команды с направленной адресацией может быть команда,, имеющая следующее содержание: выполнить операЩйо над значением, расположение которого задано в ячейке, указанной в адресном поле формата команды. Существенно, что в самой команде ofeyTCTByief указание о .типе устройства, в котором хранится значение. Это указание вместе с адресом подготавливается в процессе счета по программе в ячейке, адрес которой указан в адресном поле формата команды и уже сформировано в этой ячейке к моменту выполнения команды. . Содержимое ячейки, в свою очередь. Делится на два поля: направление-адресации и адрес. В поле направление адресации указьтвается .вид адресуемого устройства (одно из запоминающих, усгройств п юграмм и данных, например, ОЗУ или ПЗУ, блок ввода-вывода информации,, память микрокоманд и т.д.). В поле адрес указывается расположение информации внутри устройства. Выполнение команды, содержащей направлённую афесацию, начинается обычнымобразом с передачи кода операции, заданного в команде, из регистра 1 команд в регистр 2 адреса микрокоманд. Блок 3 микропрограммного управления по этому коду формирует на регистре 2 начальный адрес микропрограммы, реализующей команду. Способ получения этого Щрёса определяется выбранными для машины принципами кодирования операций в кбманд)ах,принципами построения к/ икр опрограммного автомата. , Пусть, например, ячейка, адрес которой задан в адресном поле формата исполняемой команды, расположена в запоминающем устройстве. Первая микрокоманда включает передачу адреса из регистра 1 команд в запоминающее устройство и подает сигнал в это устройство выдать на адресно-информационные входы содержимое ячейки по заданному адресу. Существенно, что адресация запоми - - , г ,, ; vis-;, 1 н.ающего устройства осуществляется под 57О непосредственный управлением блока 3 микропрограммного управления, минуя блок направления адресации 4. . Следующая микрокоманда включает об мен информацией между устройством для направленной адресации и устройством, заданным направленной адресацией. В этой микрокоманде (в зависимости от вида исполняемой команды) должна быть активизирована одна из трех микроопераций, подключающих блок 4 направл,ения адресации к полю направление адресации по адр но-информационному входу. Предположим, что если активизирован одна из двух или сразу обе микроопераци включающие, один из видов обмена йнформацие й: прием устройством информации с его адресно-информационного входа, выда чу информации устройством на его адресно- инфррмационный выход или обмен информацией между устройством и его адресно-информационным входом-выходом. Код, определяю щий устройство, задан йолем направления адресации, поэтому активизированным оказывается один из выходов дешифраторов 7, 8, и в сортветствующее устройство посылаются сигналы управления, включающие операцию обмена, В этот момент на адресно-информационных входах устройства полем адрес задан код адреса. Если, например, поспе исполнения предыдущей микрокоманды на адресно-информационных входах в попе направления адресации указан код запоминающего устройства, а в исполняемой микрокоманде активизирована одна из тре микроопераций обмена, то сигналом на выходе 1 блока 4 запоминающее устройство будет подключено для приема кода адреса и последующего примера или выдачи информации по этому адресу. Использование схемы направленной ад ресации для управления адресно-информационными входами регистра команд и регистра 2 адреса микрокоманд позволяет вводить в память микропрограмм блока 3 микропрограммного управления добавочные микропрограммы, расширяющие функциональные возможности машины и повыша1ощие ее быстродействие без изменений команд. . Пусть, например, в системе команд машины отсутствует команда, код операции которой включает вычисление функции sin (А), где А - число, записанное в запом шБщем устройстве nQ адресу, заданному в формате коматгаы. Предполагается, что 36 емкость памяти мтфопрограмм в блоке 3 микропрограммного управления превышает минимальную величину, необходимую для реализации системы команд, В добавочной емкости памяти микропрограмм записана, в частности, микропрограмма, реализующая вычисление синуса. Предполагается, , также, что разрядность слова в запоминающем устройстве достаточна для записи кодов: направление адресации, адрес микропрограммы вычисления синуса. Таким образом,- введение блока направления адресации и соответствующих связей позволяет вводить в память микропрограмм блока 3 микропрограммного управления добавочные микропрограммы, расширяющие фуйкциональные возможности устройства и ЭВМ, в которой данное усiv ройство будет применено, а .также повысить быстродействие без изменения системы команд. .Формула изобретения 1. Устройство для адресации, содержащее регистр команд, первую группу элементов И, выходы которых соединены со входом регистра команд, регистр адреса микрокоманд; первый вход которого соединен с выходом регистра команд, вторую группу элементов И, выходы которых соединены со вторым входом регистра ад- реса микрокоманд, блок микропрограммного управления, первый вход которого со;единен с выходом регистра адреса микрокоманд, а адресный выход - с третьим входом регистра адреса микрокоманд, второй выход блока микропрограммного управления является выходом микроопераций устройства, отличающееся тем, что, с целью повышения быстродействия, устройство содержит блок направления адресации, первый вход которого является адресно-информационным входом устройст ва, а первый выход - выходом микроопераций обмена с направленной адресацией, второй выход блока направления адресации соединен с первыми входами элементов И первой группы, третий выход блока направления адресации соединен с перрыми входами элементов И второй группы и со входом блокировки адреса следующей микрокоманды блока микропрограммного управления, второй вход блока направления адресации соединен с выходом микроопераций направленной адресации блока микропрограммного управления, третий 7 ,7о вход блока нппра М1йния ядресянии соединен с выходом кода направления ялресации блока микропрограммного управления, чет вертый блока направления адресации соединен со входом условия блока микропрограммного управления, вторые вхЬды впементов И первой и вто|х й групп являются адресно-информаотоннымн входами устройства. 2. Устройство по п. 1, о т л н ч а е е с я тем, что блок направления адресация содержит дешис атор приёма, де,. шифратор выдат1И, схему сравнения, первые входы которых соединены между собой и являются первым входом блока, вторые входы которых стробируются соот38ветстпующими микроо11ераш1ями иаправленнойадресации и в совокупности образуют второй вход блока, третий вход схемы сравнения является третьим входом блока, соответствующие выходы дешифраторов приема и выдачи являются первым, вторым и третьим выходами блока, выход схемы сравнения является четвертым вы-ходом блока. Источники информации, принятые во внимание при экспертизе 1.Хассон С. Д икропрограммное управление. М. , Мир, 1973. 2.Булей Г. Микропрограммирование, М., , 1973, с. 12 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство управления микропрограм-МНыМи пЕРЕХОдАМи | 1979 |

|

SU813428A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

П

Авторы

Даты

1979-12-15—Публикация

1977-08-10—Подача