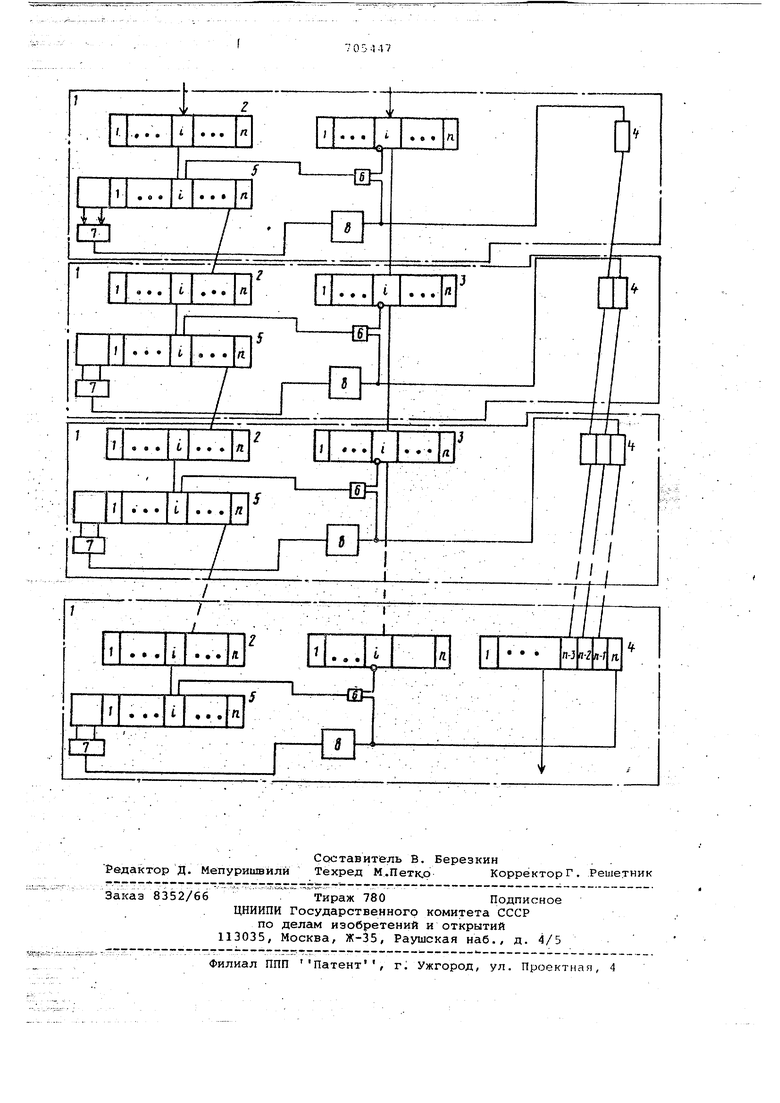

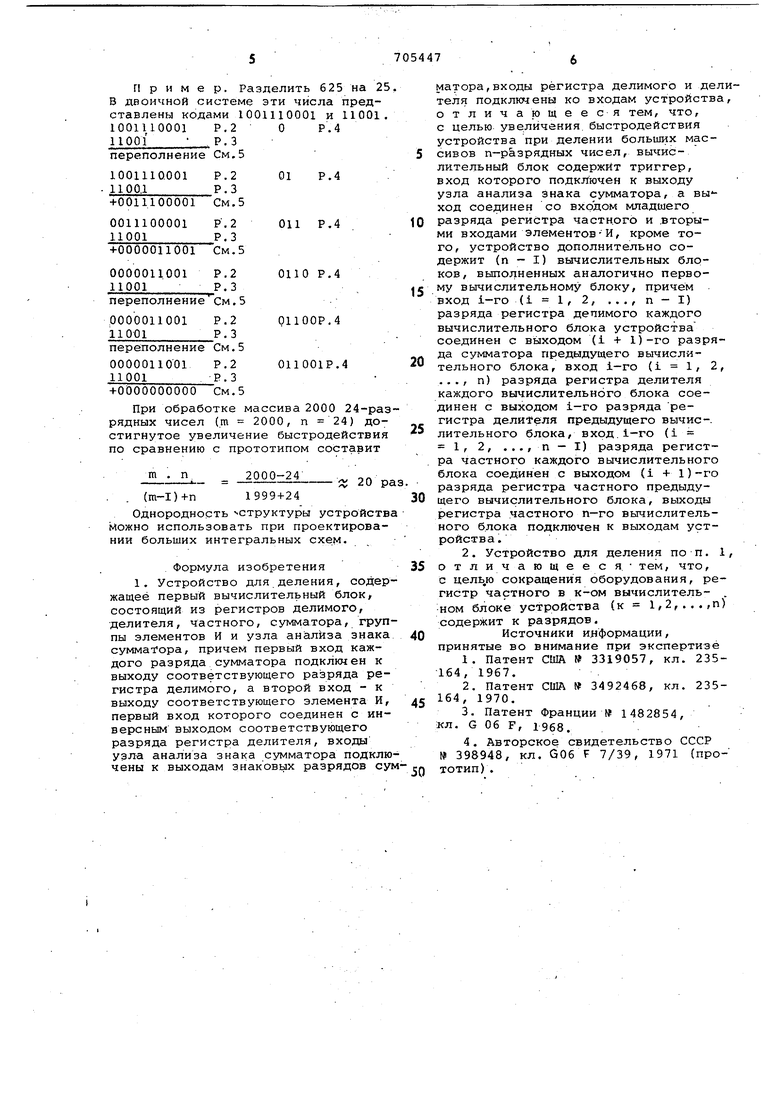

(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ пол{ енных аналогично первому вычислительному блоку, причем вход i-ro (, 2, ..,n-l) разряда регистра делимого каждого вычислитель ного блока устройства соединен с выходом (i + 1)-го разряда сумматора предыдущего вычислительного Элока, вход i-ro (1 1, 2, ,., п) разряда регистра делителя каждого вычислительного блока соединен с вы ходом i-го разряда регистра делителя предыдущего вычислительного блок вход i-ro (,2,...,n-I) разряда регистра частного каждого бглчислительного блока соединен с вы ходом (i + 1)-го разряда регистра частного предыдущего вычислительног блока, выходы регистра частного п-г вычислительного блока подключен к выходам устройства. Кроме того, с целью сокращения оборудования, регистр частного в к-ом вычислительном блоке устройства (к. 1, 2, . . . , п) содержит к разрядов. На чертеже представлена функциональная схема устройства для деления. Устройство для деления содержит п вычислительных блоков 1, каждый из которых содержит регистры делимо го 2., делителя 3 и частного 4, сумматор 5, группу элементов И б, узел анализа, знака сумматора 7,триггёр 8 Выходы регистра 2 соединены с первыми входами сумматора 5, вторые входы которого подключены к выходам группы элементов И.б, первые входы которых подклкнены к инверсным выходам регистра 3, а вторые входы выходу триггера 8, который подклине также ко входу младшего разряда регистра частного 4.Выходы знаковых р рядов сумматора 5 соединены со входами узла анализа знака сумматора 7 выход которого подключен ко входу триггера 8.Входы i-x разрядов (1 1, 2, ..., п - I) регистра 2 кажд вычислительного блока 1, начиная со второго, подключены к выходам (1 + + 1)-X разрядов сумматора 5 предыду щего вычислительного блока 1. Выходы i-x разрядов (i 1, 2, - п) регистра 3 каждого вычислительного блока 1, начиная со второго, подключены к выходам 1-хразрядов регистра 3 предыдущего вычислительного блока 1 . дакоды; i-х 5азрядов (i l, 2, ..., n-I) регистра 4 каждого вычислительного блока 1, начиная со второго, .подключены к вы ходам (1 + 1)-X разрядов регистра 4 предыдущего вычислительного блока1. Входы регистров 2 и 3 первого -вычислительного блока 1 подклинены входам устройства, выходы регистра 4 .п-го вычислительного блока 1 подклю«ены к выходам устройства. Регис 4 к-го вычислительного блока 1 (к 1, 2, .1., п) содержит к разрядов. Деление выполняется без восстановления остатка в два полутакта следующим образом. В первом полутакте первого такта в регистр 2 первого вычис:пительного блока 1 записывают первое делимое, а в. регистр 3 - первый делитель. Из делимого вычитается делитель.. При этом триггер 8 сброшен и единица на его выходе не препятствует сложению в обратном коде. Одновременно,содержимое регистра 3 переписывается в регистр 3 последующего вычислительного блока. Во втором полутакте происходит анализ знака сумматора 5 узлом анализа знака сумматора 7 и запись первого разряда частного в младший разряд регистра 4. Если остаток получился положительный, частное равно единице и элементы И б останутся открытыми. Если остаток отрицательный, разряд частного равен нулю, триггер 8 опрокинется и элементы И б закро- , ются, вычитания не произойдет (на все входы сумматора 5 вместо делителя поступят нули) и на комбинационном сумматоре 5 восстановится первоначальное значение делимого. Со сдвигом влево значения сумматора 5 перепишется в регистр 2 последующего вычислительного блока 1, а значение регистра 4 - в регистр 4 последующего вычислительного блока 1. , В первом полутакте второго такта в освободившиеся регистры 2 и 3 первого вычислительного блока 1 запишутся нов.ые числа, которые вычитают в сумматоре 5 первого вычислительного блока 1 для получения первого остатка второй пары чисел. Одновременно в сумматоре 5 в.торого вычислительного блока 1 получают второй остаток первой пары чисел. Во втором полутакте второго такта получают первый разряд результата деления второй пары чисел в регистре 4 первого вычислительного блока 1 и второй разряд результата деления первой пары чисел в регистре 4 второго вычислительного блока 1. Затем содержимое предыдущих вычислительных блоков 1 переписываю,т в последующие, освобождая первый вычислительный блок для принятия следующей третьей пары чисел. Результат деления каждой пары чисел образуется за п тактов, причем в каждом вычислительном блоке 1 образуется очередная цифра частного, аналогично тому, как-это было описано выше. Пример. Разделить 625 на В двоичной системе эти числа пре ставлены кодами 1001110001 и 110 1001110001 Р.2 О Р.4 11001 . Р.З См. 5 переполнение 011 Р,4 +0000011001 См.5 0000011001 Р.2 ОНО Р.4 11001 переполнение См. 5 РО00011001 Р.2 01100Р,4 11001 Р .3 переполнение См.5 0000011001 Р.2011001Р.4 11001 Р-3 +0000000000 См.5 При обработке массива 2000 24рядных чисел (т 2000, п 24) д стигнутое увеличение быстродейств по сравнению с прототипом состави 2000-24 20 . . (т-1)+п 1999+24 Однородность «структуры устройс можно использовать при проектиров нии больших интегральных схем. Формула изобретения 1. Устройство для деления, сод жащее первый вычислительный блок состоящий из регистров делимого, делителя, частного, сумматора, гр пы элементов И и узла анализа зна сумматора, причем первый вход каж дого разряда сумматора подклкнен выходу соответствующего ра:зряда р гистра делимого, а второй вход выходу соответствующего элемента первый вход которого соединен с и версным выходом соответствующего разряда регистра делителя, входы узла анализа знака сумматора под чены к выходам знаковых разрядов матора,входы регистра делимого и делителя подклкиены ко входам устройства, отличающееся тем, что, с целью увеличения, быстродействия устройства при делении больших массивов п-р&зрядных чисел, вычислительный блок содержит триггер, вход которого подключен к выходу узла анализа знака сумматора, а соединен со входом младшего разряда регистра частного и .вторыми входами элементов-И, кроме того, устройство дополнительно содержит (п - I) вычислительных блоков, выполненных аналогично первому вычислительному блоку, причем вход i-ro (, 2, ..., n-I) разряда регистра делимого каждого вычислительного блока устройства соединен с выходом (1 + 1)-го разряда сумматора предыдущего вычислительного блока, вход 1-го (, 2, ..., п) разряда регистра делителя каждого вычислительного блока соединен с выходом 1-го разряда регистра делителя предыдущего вычис-. лительного блока, вход.1-го (i 1, 2, ..,,п- I) разряда регистра частного каждого вычислительного блока соединен с выходом (i + 1)-го разряда регистра частного предыдущего вычислительного блока, выходы регистра .частного п-го вычислительного б.лока подключен к выходам устройства. 2. Устройство для деления по п. 1, отличающееся тем, что, с цель.ю сокращения оборудования, регистр частного в к-ом вычислитель- . ном блоке устройства (к 1,2,...,п) содержит к разрядов. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3319057, кл. 235164, 1967. 2.Патент США № 3492468, кл. 235164, 1970. 3.Патент Франции № 1482854, кл. G 06 F, 1968. 4.Авторское свидетельство СССР № 398948, кл. G06 F 7/39, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1980 |

|

SU898425A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

Авторы

Даты

1979-12-25—Публикация

1976-07-09—Подача