(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ДИФФЕРЕНЦИАЛЬНЫХ

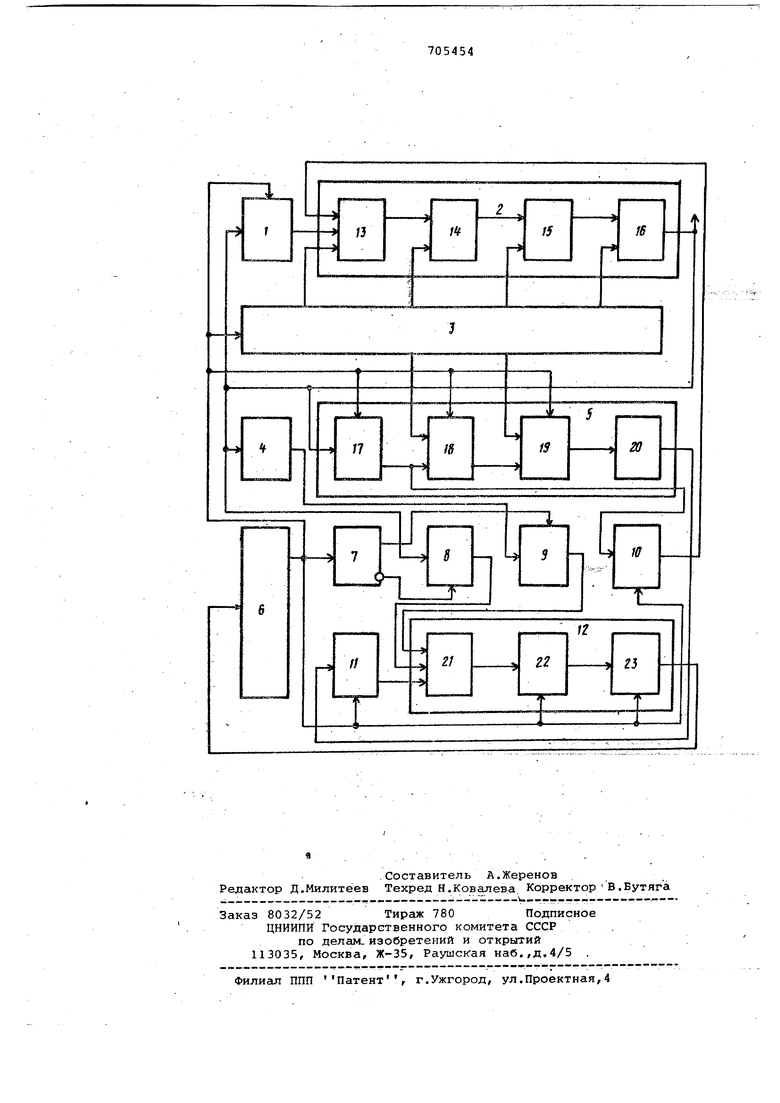

УРАВНЕНИЙ pa правых частей, либо к увеличению инструментальной погрешности. Целью настоящего изобретения является повышение- точности устройст ва, С этой целью в него введены реккурентно-вычислительный блок, блок памяти, блок инвертирования, накопительно-сдвигаюв1ий блок и накопительно-сравнивающий блок, причем первый и второй выходы блока памяти подключены соответственно, к.первому и второму входам накопительно, сдвиганэгаего блока, третий, четверты .пятый и шестой выходы блока памяти подключены соответственно к первому второму, третьему и четвертому входам реккурентно-вычислительного бло ка, пятый вход которого соединен с выходом первого блока коммутации, выход реккурентно-вычислительного блока подключен к третьему входу накопительно-сдвигающего блока, ко входам первого и второго блоков коммутации и ко входу блока инверти рования, выход которого соединен со входом третьего блока коммутации, выходы накопительно-сдвигающего бло подключены соответственно ко входам четвертого и пятого блоков коммутации, выход четвертого блока коммута ции соединен с шестым входом реккурентно-вычислительного блока, выходы второго, третьего и пятого блоков коммутации соединены соответственно с первым, вторым и третьим Ьходами накопительно-сравнивающего блока, выход которого подключен ко входу блока управления, выход которого соединен с управляющими вх дами блока памяти, накопительносдвигающего блока, накопительно-сра нивающего блока, первого, четвертого и пятого блоков коммутации и триггера, первый и второй выходы которого соединены соответственно с управляюидами входами второго и третьего блоков коммутации. Кроме того, реккурентно-вычислительный блок устройства содержит два нноясителя, сумматор и группу элементов ИЛИ, входы которых подключ ны соответственно к первому, пятому и шестому входам блока, второй, тре тий и четвертый входы которого подключены соответственно к первым входам первого множителя, сумматора и второго множителя, выход группы элементов ИЛИ подключен ко второму входу первого множителя, выход кото рого через к сумматор соединен со вторым входом второго множителя, выход которого подключен к выходам блока. На чертеже представлена схема устройства для решения систем дифференциальны. уравнений, со сле ющими обозначениями: блок 1 коммутации, реккурентно-вычислительный блок 2, блок 3 памяти, блок 4 инвертирования, накопительно-сдвигающий блок 5, блок 6 управления, триггер 7, блоки 8,9,10 и 11 коммутации и накопительно-сравнивающий блок 12. Реккурентно-вычислительный блок 2 содержит группу элементов 13 ИЛИ, множитель 14, сумматор 15, множитель 16, Накопительно-сдвигающий блок 5 включает: накапливающий сумматор 17,г регистры 18,19, узел 20 инвертирования. Накопительно-сравнивающий блок 12 состоит из группы элементов 21 ИЛИ, накапливающего сумматора 22 и схемы 23 сравнения.; Работу устройства можно пояснить на примеререшения систем дифференциальных -уравнений вида )(tl,)((o)rx (i) - время. XW - вектор неизвестных, А - матрица постоянных коэффициентов, iW - вектор правых частей, хСо) - начальное значение X(-t) при . Для того, чтобы быть решенной рассматриваемым устройством, система дифференциальных уравнений (1) должна быть представлена путем подразделения интервала интегрирования (О,Т) на N равных частей (подинтер валов) Hr-TN в влле системы локальных уравнений (г) -д --vAx:j(c)-f(t), x.(o)x(iH), ostrsHC S:) где (гV-t(H-fгX-i oИ,..., N-H, . которая получается из исходной системы дифференциальных уравнений (1) путем переноса начала координат из точки io f в точку iH , . причем С имеет смысл локального времени, изменяющегося от Т О до Т Н. Связи между 1-м и ( i + 1)-м локальными уравнениями определяются из условия непрерывности iCHV- i4 to)Далее на следующем этапе подготовки исходной системы дифференциальных уравнений.(1) для решения система локальных дифференциальных уравнений (2) должна быть представлена на основе правил и формул преобразо- ваний Тейлора (Т- преобразований), определяк)щих связи между оригиналом x(t) и его Т-изображением Х{к) на основе соотношений tVxck,(3) где i - символ перехода от x(t) к Х(к) и, наоборот, от Х{к) к x(t), К - аргумент, принимакяцйй целоч ленные значения 0,1.2... оо ,в виде соответствующего этой системе локальных уравнений Т - изображения -)-((1) )-х(ц), (/ где Х 10вектор к-х дискрет изображающей вектор х,-(f) вектор - функц F W - вектор к-х дискрет изо ражающей вектор №) вектор - фун ции. Устройство работает следующим образом. В соответствии с выражени (4) для каждого-подынтервала интер вала О,Т интегрирования устройство вычисляет совокупность векторов дискрет на основе соотношения ))-:АХ(1),х(о1--хии (5 то есть определяет векторы дискрет Число учитываемых дискрет и величина шага интегрирования контроли-руются в устройстве в соответствии с формулой , П(НГХ.(М:Х, ,(о) (6) -о ЕСЛИ число совпадающих цифр :(разрядов) в правой и левой частях выражения (6) недостаточно, то устройство повторяет вычисления при .уменьшенном шаге Н либо определяет большое число дискрет. Если условие (6), которое представляется в виде S (..(VVX. () где Е - заданная величина, характеризующая требуемую точность вычислений, выполняется с удовлетворительной точностью, то устройство осувтествляет вычисление вектора первых дискрет следующего подУнтер ла интегрирования в соответствии с выражением. . ) x.Ctl --В. (И) после чего в устройстве определяются векторы дискрет.Вычисления . повторяются аналогично до достиже ния конца интервала интегрйровайй Работа устройства начинается с в дачи сигналов управления с выхода блока б управления на управляющие входы блока 3 памяти, первого 18 и второго 19 регистров. При поступлении этих сигналов происходит считывание из блока 3 памяти этих сигИалов происходит ачитывание из блока 3 памяти и запись в регистры 18 и 19.начальных условий: в регистр 18 заносит.ся код нуля, в регистр 19 заносится значение вектора дискрет X (0) . Одновременно из блока 3 памяти на входы элементов 13 ИЛИ поступает вектор -дискрет XQ (0) - Хо . По сигналам управления из блока б, поступающим на управляющие входы триггера 7, схемы 23 сравнения, накапливающего сумматора 17 и накапливающего сумматора 22, осуществляется установка в них кодов нуля-нулевых начальных условий. По, сигналам управления, поступающим . с выхода блока б на управляющий вход блока 11 коммутации, инвертированный вектор дискрет с выходов, блока 4 через блок 9 колмутации поступает на входы элементов 21 ИЛИ. По сигналам управления, поступающим из блоЛа б на управляющий вход сумматора 22, осуществляется суммирование занесенного первоначального в него кода нуля и значения векторе дискрет. По сигналамУправления, поступающим из блока 6 управления на управляющий вход блока 3 памяти,- из последнего считываются: на первые входы множителя 14 значения компонент матрицы (А) постоянных коэффициентов, на первый вход сумматора 15 значения компонентов вектора дискрет правых частей, на первый вход второго множителя 16 значение коэффициента H/k- . Таким образом, устройство реализует зависимость (5) при и к « О - вычисляет значение вектора дисррет, которое с выхода второго множителя 16 поступает на входы блока 1, блока 4, накапливающего сумматора 17, блока 8. По сигналу управления из блока б на управляющий вход накапливающего 17 осуществляется суммирование, в соответствии с (8), первоначально занесенного в него кода нуля с вектором Хо(1). Одновременно вектор X о (О через открытый единичным сигналом с первого выхода триггера 7 блок 8 поступает через элементы 21 ИЛИ на вход накапливающего сумматора 22, в котором по сигналу управления из блока б осуществляется вычисление текущего значения левой асти условия (7), поступающей на вход схемы 23 сравнения. По сигналу правления, поступающему из блока б а управляющий вход схемы 23 сравения проверяется выполнение условия (Т) . Если условие (7) выполнено, то с выхода схемы 23 сравнения на вход блока б управления поступает код выполнения условия (7) и сигнал управления с выхода блока б поступает на управляющей вход блока 10, разраиая прохождение вектора, полученного в соответствии с выражением (И) i с выхода накапливающего сумматора 17 на входы элементов 13 ИЛИ, Таким образом, в следующем цикле работы устройства яа второй вход первого множителя 14 поступает векторX,(o-) Одновременно, по сигналу управления .с выходов блока б осуществляется запись в регистр 18 вектора (8) с выхода накапливающего сумматора 17. Следующим сигналом управления, поступающим с выхода бло.ка 6 на упра1вляющий вход регистра .19, осущес вляется перезапись (сдвиг) вектора (8) из регистра 18 в регистр 19. После этого, по сигналам управления из блока б управления осуществляется установка .начальных (нулевых) условий (установка в .нуль) триггер 7 схемы 23 сравнения, накапливающих сумматоров 17 и 22, и если.конец интервала интегрирования не достигнут ТО осуществляется следующий Цйкй : работы устройства аналогично описанному ваше. Если условие (7) не выполнено, .то подачей сигнала из б управления на вход триггера 7 :11оследний пе Е5еводит ся в противоположное состо ние1в рассматриваемом случае - единичное): единичный сигнал со второг . выхода триггера 7 открывает блок 9коммутации, а нулевой сигнал с перво го выхода триггера 7 закрывает блок 8. Аналогично описанному выше, устройство вычисляет следующий вект дискрет, но на входы накапливающего сумматора 22 поступают с выхода бло ка 4 через блок 9, элементы 21 ИЛИ его инвертированное-значение в соот ветствии с выражениями (б) и (7), В дальнейшем работа устройства аналогично описанному выше, В зависимост от результата проверки условия (7) осуществляется либо переход к следу ющему подынтервалу интегрирования, либо вычисление следующего на текущем подынтервале вектора дискрет неизвестных. На основе жесткого контроля точности результатов на каждом этапе вычислений обеспечиваются путем увеличения числа определяемых дцйкрет или уменьшением шага интегрирования любые заданные малые величины остаточных членов при суммировании конечного числа дискрет, т.е. обеспечивается практи чески любая требуемая точность вычи лений. ; Формула изобретения 1.Устройство для решения систем дифференциальных уравнений,содержащ блоки коммутации,; блок управления, триггер , отлйчающееся гём,что, с целью повышения точносл ти, в него введены реккурентновычи слит ел ьный блок, блок памяти, блок инвертир ования, накопительносдвигающий блок и накопительносравнивающий блок, причем первый и . второй выходы блока памяти подключены соответственно к первому и второму входам накопительно-сдвигающего блока, третий, четвертый, пятый и шестой выходы блока памяти подключены соответственно к первому, второму, третьему и четвертому входам реккурентн вычйслительн ого блока, пятый вход которого соединен с выходом первого блока коммутаций, выход реккурентно-вычислитёль.ного блока пЬдКлйчен к третьему входу накопительно-сдвигающего блока, ко входам первого и второго блоков коммутации и ко входу блока инвертирования, выход которого соединен со входом третьего блока коммутации, выходы накопительно-сдвигающего блока подключены соответственно ко входам четвертого и пятого блоков коммутации, выход чё вертого блока ко.ммутации соединен с шестым входом реккурёнтно-вычислительного блока, выходы второго, третьего и блоков коммутации соединены соответственно с первым, вторым и третьим входами накопительно-сравнивающего блока, выход которого подключен ко входу блока управления, выход которого соединен с управляющими входами блока памяти,накопительно-сдвигающего «„„t,a ,г,.:;„„„,,„j блока, накопительно-сравнивающего блока,первого,четвертого и пятого блоков коммутации и триггера, первый и вто- рой выходы которого соединены соответственно с управляющими входами второго и третьего блоков коммутации, . . 2, Устройство по п.1, отличаю ще е с я тем,что .реккурентновычислител.ьный блок содержит два множителя, сумматор и группу элементов ИЛИ, входы кдторых подключены соответственно к первому, пятому и .шестому -входам блока, второй, .третий и четвертый входы которого подклю чены соответственно к первым входам . первого множителя,сумматора и второго множителя,выход группы элементов ИЛИ подключен ко второму входу первого множителя,выход которого через сумматор. соединен со вторым входом второго мнрисителя/выход которого подключен к выходу блока. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 526905, кл.О Об F 15/32, 1974, 2,Авторское свидетельство СССР 481041,кл. G06 F 7/34, 1973 (прототип) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем дифференцильных уравнений | 1977 |

|

SU717778A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714407A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714406A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU674030A1 |

| УСТРОЙСТВО для МОДЕЛИРОВАНИЯ ГИДРОФИЗИЧЕСКИХ | 1973 |

|

SU369580A1 |

| Цифровое устройство для решения систем линейных алгебраических уравнений | 1976 |

|

SU648988A1 |

| Цифровое устройство для решения систем линейных алгебраических уравнений | 1975 |

|

SU559241A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Устройство для решения систем алгебраических уравнений | 1977 |

|

SU682902A1 |

Авторы

Даты

1979-12-25—Публикация

1977-07-13—Подача