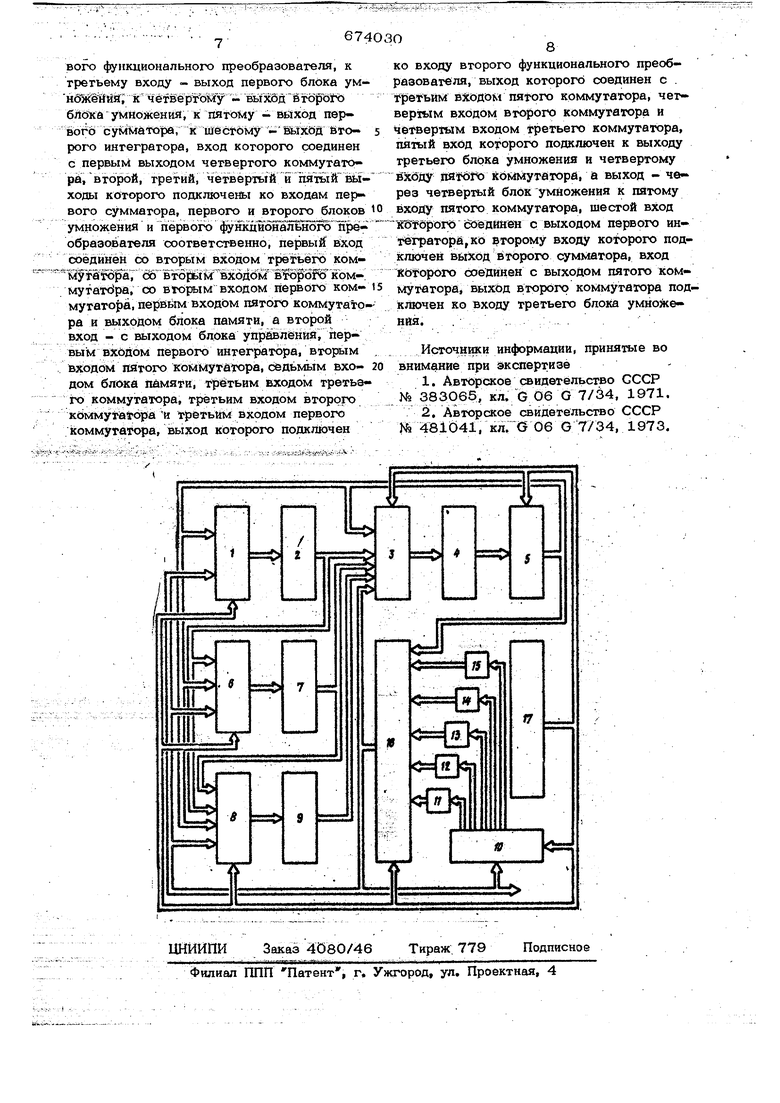

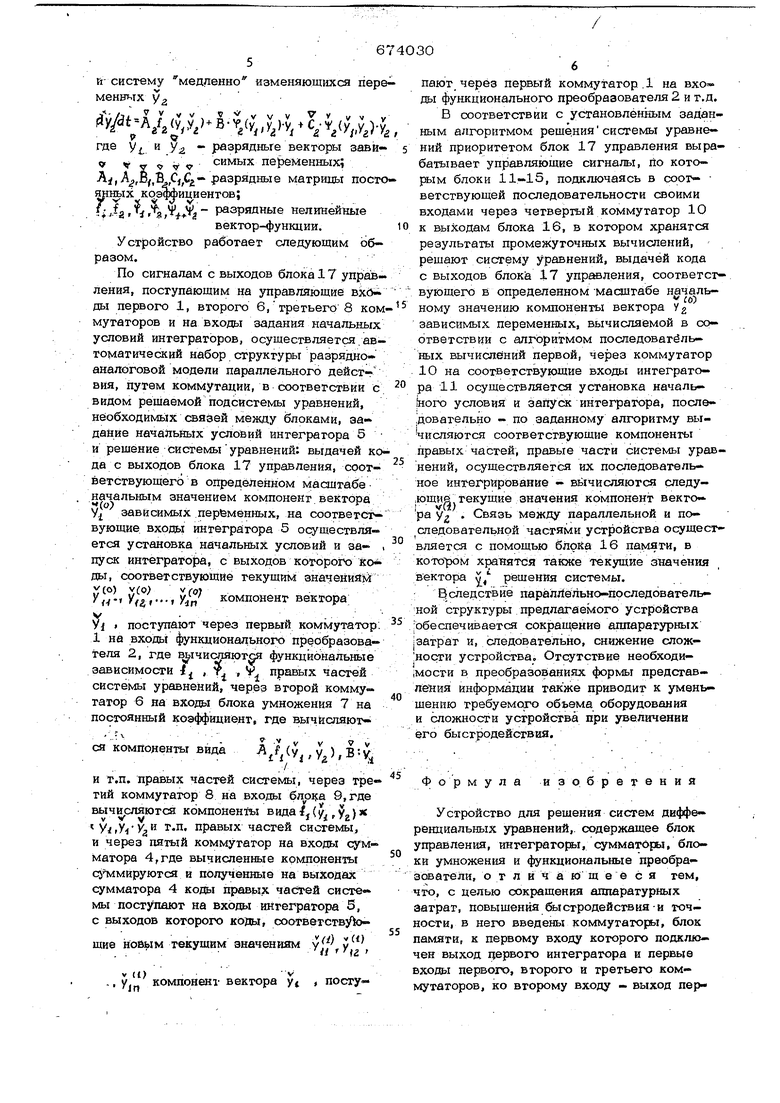

сгемь моделируются параллельно во времени и пространстве), растет с увеличением порядка решаемой системы пропорционально количеству моделируемых уравнений. Однако для ряда актуальных задач, Шя й 1Ь1% ЖГрййёр t; йсШёдШ намики объектов управления, в частнбсти йетательнкгх аппаратов, динамические характеристики известных устройств д;ля решения систем дифференциальных уравнений, имекэших аналогично прототипу параллель ную структуру, оказываются значительно превышающими динамические характеристики объектов моделирования. В этих случаях построени е устройств для моделированйя систем дъ фференциальных уравнений с параллельной структурой параллельным принципом функционирования не оправдывает себя из-за необоснованной их сложности - больших затрат оборудования при решении систем диф(}юренциалъных уравнений высокого порядка. Существенным недос татком известного устройства является также необз бдймосгь многократных преобразований .аналог-код и код-аналог фор мы представления информации в процессе {5ейёния задачи, что существенно ограничивает его быстродействие и требует до п6Лййтельнь1х iaiiiiapaiTypHb№ затрат - ана.3 :пого-цифровых и цифро-аналоговых пре образователей. К недйс-ратйам прототипа еле дуе отнести и то, что связи между вычислитель:ными блоками являются жестко усТйнреленными и не могут автоматичео1сИ-ЙзШШ1тьс при йЭмененйи задачи конкрётного вида правых частей решаемой системы уравнений. ЭТр не позволяет пол, ностью автоматизировать процесс набора вычислительной структуры и решения при ; расширений кла-ссарёшаемьтх задач. . . Целью настоящего изобретения являет.; ся сокращение аппаратурных затрат, повышение &1стродействия и точности устройства. Поставленная цель достигается тем, что в предлагаемое устройство введены коммутаторы, блок памяти, к первому вхо ду которЪгхэпбдключен выход первого .тегратора и первые входа первого,второ гЬ и третьего коммутаторов, ко второму входу - выход первого функционального преобразователя, к третьему входу -выход первого блока умножения, к четвертому - выход второго блока умножения, к пятому - выход первого сумматора, к piebi Wy :-вЙ7 ;Ш Твт«р:яЧГ 1 вход которого соединен с первым выходом четвертого коммутатора, второй, тре« тий, четвертые и пятый выходы которо-го подключены ко входам первого сумматора, первого и второго блоков умножения и первого функционального преобразователя соответственно, первый вход соединен со вторым входом третьего коммуraixjpa, со вторым, входом второго коммутатора, со вторым входом первого коммутатора, первым входом пятого коммутатора и выходом блока памяти, а вто- рой вход - с выходом блока управления, пёрвым входом первого интегратора, втоpeiM входом пятого коммут/атора, седьмым входом блока памяти, третьим входом третьего коммутатора, третьим входом второго коммутатора и третьим входом первого коммутатора, выход которого подключен ко входу второго функционального преобразователя, выход которого соединен с третьим входом пятого коммутатора. четвертым входом второго коммутатора и четвертым входом третьего коммутато- ра, пятый вхбд которого подключен к выходу третьего блока умножения и четвертому входу пятого коммутатора, а выходч рёа четвёртай блок умножения -к пятоiviy входу пятого коммутатора, шестой вход которого соединен с выходом первого интегратора, ко второму входу каторого подключён выход второго сумматора, вход которого соединен с выходом пято коммутатора, выход второго коммута р подключен ко входу третьего блока умножения. На чертеже представлена блок-схема устройства для решения систем дифферен„«альных уравнений. - Устройство содержит первый коммутатор 1, .второй функциональный преобразователь 2, пятый коммутатор 3, второй сумматбр 4, первый интегратор 5, втор коммутатор 6, третий блок 7 умножения, третий коммутатор 8, четвертый блок 9 умножения, четвертый коммутатор Ю, второй интегратор 11, первый сумматор 12, второй блок умножения 13, первый блок умноягения 14, первый функциональный преобразователь 15, блок 16 памяти, блок 17 управления, выход блока 16 является выходом устройства. Решаемая система дифференциальных уравнений cfy/dt-Af((y).y представляется в разрядной форме и подразделяется на две системы - систему быстроизменяюшихся переменных у V ,, 5 Jf V V V V Vt v vv „ Jdl A,f, (y,, X, ) B,- , У,)-У,С,(У,,УЛ й-систему медленно изменяющихся пере менньтх d v/fJf-A // IR V 1 ,y)(ypy)-y , где У и у.2 - разрядные векторы зави- s ff чг V V V симых переменных; Ai,A,B|,B,,C,,C2-разрядные матрицы посте Hpiuix крэдфициентов; ,l, разрядные нелинейные вектор-функции. Устройство работает следующим образом. По сигналам с выходов блока 17 управления, поступающим на управляющие вхб ; ды первого 1, второго 6,третьего 8 коммутаторов и на входы задания начальных условий интеграторов, осуществляется.ав томатический набор структуры разрядноаналоговой модели параллельного деист- ВИЯ, путем коммутации, в соответствии с видом решаемой подсистемы уравнений, нёобходимь1Х связей между блоками, задание начальных условий интегратора 5 и решение системы уравнений: выдачей ко да с выходов блока 17 управления, соответствующегб в определенном масштабеначальным значением компонент.вектора У зависимых переменных, на соответствующие входь интегратора 5 осуществляется установка начальнь1х условий и запуск интегратора, с выходов которогч 1со ды, соответствующие текущим значенияй .(о) v(. У{, компонент вектора У I поступают через первый коммутатор 1 на вхоДы функционального преобразователя 2, где ш,1чиспяют функциональные зависимости 1 , Т , V правых частей системы уравнений, через второй коммутатор 6 на входы блока умножения 7 на постоянный коэффициент, где вычйсляются компоненты вида Д f (у у ),Ву и т.п. правых частей системы, через тре тий коммутатор 8 на входы 9, где вычисляются компоненты вида1(/ ,y,j)« yiiYiV правых частей сисгемы, и через пятый коммутатор на входы сумматора 4,где вычисленные компоненты c5 v миpyютcя и полученные на выходах сумматора 4 коды npaBbix частей системы поступают на входы интегратора 5, с выходов которого коды, cooTBeTCTBjfltoщие HOSbiM текущим значениям yff, , компонент вектора yt , посту10паюг через первый коммугагор.1 на входы функционального преобразователя 2 и г.д. соответствии с установленным заданным алгоритмом решениясистемы уравне ний приоритетом блок 17 управления вырабатывает управляющие сигналы, lio кото рым блоки 11-15, подключаясь в соот- ветствующей последовательности своими входами через четвертый коммутатор 10 к выходам блока 16, в котором хранятся результаты промежуточных вычислений, рещают систему уравнений, выдачей кода с выходов блока 17 упр ления, соответствуюшего в определенноммасштабе начальному значению компоненты вектора У зависимых переменных, вычисляемой в соответствии с алгоритмом последовательных вычислений первой, через коммутатор 10 на соответствующие входы интегратора 11 осуществляется установка начальkoro условия и запусж интегратора, после,довательно - по заданному алгоритму вычисляются соответствующие компоненты правых частей, правые части системы уравнений, осуществляется их последовательное интегрирование - вьгчисляются следу- ,ющий Текущие значения компонент векто- v(l) pa у . Связь между параллельной и по следовательнрй частями устройства осуществляется с помощью блока 16 памяти, в котором хранятся также текущие значения вектора у решения системы. В. следствие паралйельно-последователь:ной структуры предлагаемого устройства обеспечивается сокращение аппаратурных iзатрат и, следовательно, снижение слож- ности устройства. Отсутствие необходиjMocTH в преобразованиях формы представления информации также приводит к уменьшению требуемого объема оборудования и сложности устройства при увеличенви его быстродействия. Формула изобретения Устройство для решения систем дифференциальных уравнений,, содержащее блок управления, интеграторы, сумматоры, блоки умножения и функциональные преобразователи, о т л и ч а ю щ её с я тем, что, с целью сокращения аппаратурных затрат, повышения быстродействия-и точности, в него введены коммутаторы, блок памяти, к первому входу которого подключен выход цервого интегратора и первые входы первого, второго и третьего коммутаторов, ко второму входу - выход пер

Авторы

Даты

1979-07-15—Публикация

1977-03-28—Подача