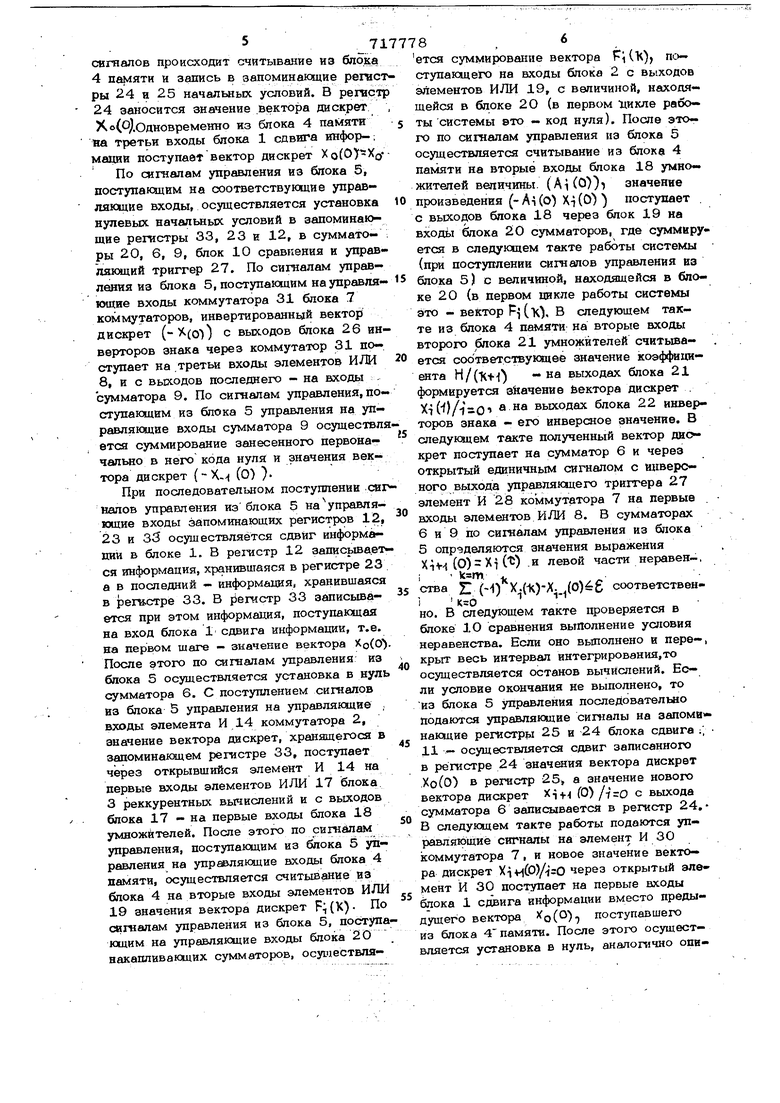

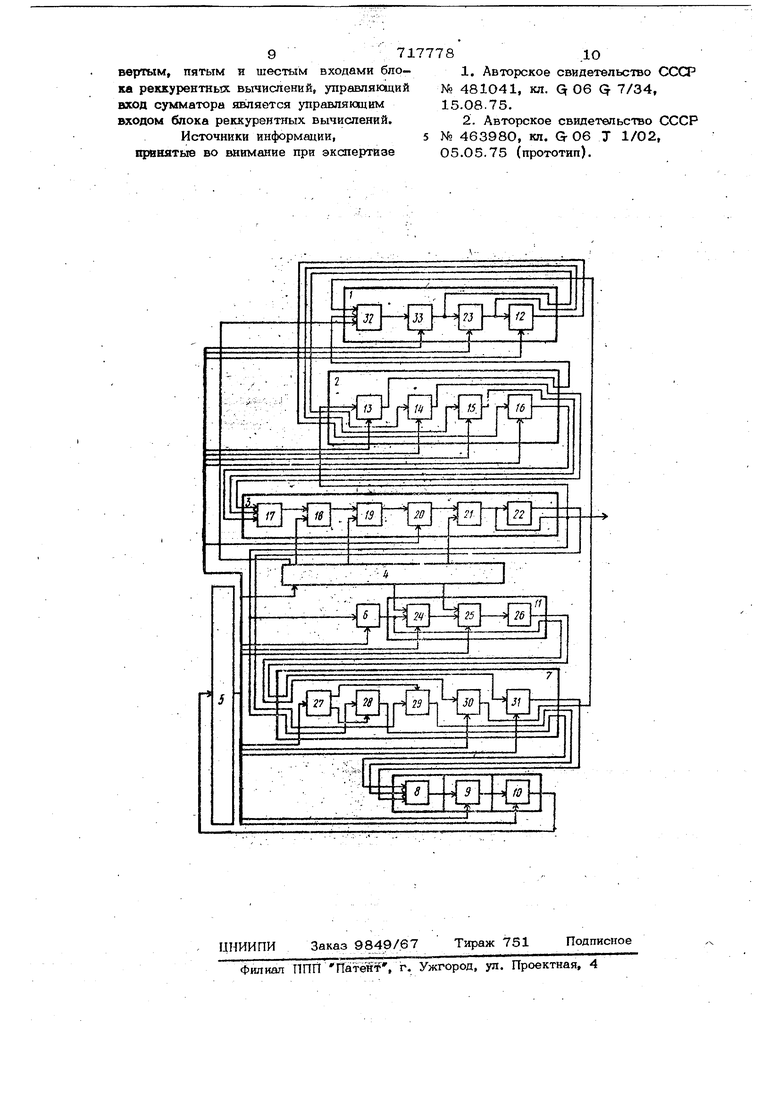

(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ OiCTEM УРАВНЕНИЙ ДИФФЕРЕНЦИАЛЬНЫХ , ; , 3 717 riepBoiX) блока сдвига, первый, второй и третий Выходы которого соединены с бторым, третьим и четвертым входами первого коммутатора, второй, третий и вертый выходы которого подключенык четвертому, пятому и шестому входам блока реккурентных вычислений, второй выход которотю соединен с первым входом второй 14) коммутатора, второй вход которого подключен к входу первого сулшатора и к первому выходу блбка реккурентных вычислений, вькод первого сушлатора соединен с гЁэрвьгм входом второго блока сдвига и с .вторым .входом второго коммутатора, первый, второй и третий выходы которого подключены к первому, второму и третьему входам элемента ИЛИ, выход которого соединен с входом второго сумматора. Выход которого подключен к входу блока , сравнения, выход которого соединен с входом блока управления, четвертый и выходы блока Памяти подключен соответ ctBeSHo к второму и третьЪму входам .второго блока сдвиге, выход которого соединен с третьим входом второго коммута I- тора, четвертаки взсбд koibofiolxj поЩйючен к второму выходу блока реккурентных вы1 числений, четвертый вШ:рд второго ком- ; мутатора соединен с вторым входом первого коммутатора, третий вход которого ; йЬДкЯЮчен к шестому выходу блока памят%уп рЙвЛЙКЙ1№ входы первого и второго блока сдвигов, блока памяти, блока реккуреатных вычислений, первого и второго йШтОрШгперво1ю и второй) коммутато ров, бйШй сравншия сюеДинены с соответствующими выходами блока управления. Кроме того блой рё&курентных вычислений содержит блоки (умножения, сумматор, инвертор и элементы ИЛИ, выход первого из которых подключен к первому входу первого блока умножения, второй (ВХОД кбтЪрогоЛвляётся первым входом бл ка реккурентных вычислений, выход блока умножения подключен k первому Ьходу f рого элемента ИЛИ, ВьгХОД которого оЬе ДййёЙ с ЪхЬДом суьШа ора, выход которого подклШёй к iSejpfiowy вхОДу второго е«(ШУКйе ний,:ЙШЩ кОторо ся первым выходом блока реккурентных вычислений и соедин с входом инвертор ра, выход которого йзйляется вторым выходом блока реккурентных выч«кяений, вторые входы второго элемента ИЛИ и второго блока умножения являются соответственно вторым и третьим кхолвмл блока реккурентных вычислений, пе1шый, второй и третий входы первого .. 4 ЛИ являются ооответственно четвертым, ятым и шестым входами блока реккурена ных вычислений, управляющий вход сумма- тора является управляющим входом блока реккурентных вычислений, На чертеже представлено предлагаеое устройство.. Устройство содерншт блок 1 сдвига информации, блок 2 коммутаторов, блок 3 реккурен-гаых вычислений, блок 4 памяти, блок 5 управления, сумматор 6, блок 7 коммутаторов, элемент ИЛИ 8, сумматор 9, блок 10 сравнения а блок 11 сдви га. Блок 1 сдвига информации состоит из элементов ИЛИ 32, запоминающих решст ров 12, 23 и 33. Блок 2 коммутаторов состоит из элементов И 13-16. Блок 3 реккурентаых вычислений состоит из элементов ИЛИ 17, первого блока 18 умножителей, элементов ИЛИ 19, бло- ка 2О накапливающих сумматоров; блока знака. Блок 11 сдвига состоит из запомина- ющих регистров 24 и 25 и блока 26 ин-i верторов знака. Блок 7 коммутаторов состоит из управляющего триггера 27 и коммутаторов 28-31. Работа предлагаемой в)ьгчислительной системы гоясня1ется на примере решения систем ди«||ференциальных уравнений вида где g в1й орйей Л (т;- матрице переменных коэффициентов;i(-t) - вектор правых частей; t - время; (0) - начальное значение X(t) . Используя Т-преобразование Тейлора, данная система приводится к виду ;. . ), А,(е)Х. .(K),x.,((4H), гдеХ.(К) - вектор 1с -л дискрет, изображающий вектор Чт(t) векторфункции;F,(H) вектор X -X дискрет, изображающий вектор f i(t) векторфункции;А(е).. матрица -х дискрет, изображаюшая матрицу Av(t) матричной функции. Работа вьгчислительной системы нaчинa ется с выдачисигналов управления с выходов блока 5 управления на управляющие входы блока 4 памяти- и запоминающих регистрой 24 и 25. При поступлении этих сигналов происходит считывание из блока 4 памяти и запись в запоминающие регис ры 24 и 25 начальных условий. В регист 24 заносится значение вектора дискрет оСЯ-Одновременно из блока 4 памяти ва третьи входы блока 1 сдвига инфор-; мации поступает вектор дискрет По сигналам управления из блока 5, поступающим на соответствующие управляющие входы, осуществляется установка нулевых начальных условий в запоминающие регистры 33, 23 и 12, в сумматоры 20, 6, 9, блок 10 сравнения и управ лякядий триггер 27. По сигналам управления из блока 5,поступающим науправляющие входы коммутатора 31 блока 7 коммутаторов, инвертированный вектор дискрет (-(0)) с выходов блока 26 ий верторов знака через коммутатор 31 поступает на третьи входы элементов ИЛИ 8, и с выходов последнего - на входь , сумматора 9. По сигналам управления, поступающим из блока 5 управления на управляющие входы сумматора 9 осуществля ется суммирование занесенного первоначально в него кода нуля и значения вектора дискрет (Х-( (о) } При последовательном поступлении сиг налов управления из блока 5 науправляющие входы запоминающих регистров 12, 23 и ЗЗ осуществляется сдвиг информации в блоке 1. В ретастр 12 записьша.ет- ся информация, хранивщаяся в регистре 23 а в последний - информация, хранившаяся в регистре 33. В регистр 33 записывается при этом информация, поступающая на вход блока 1 сдвига информации, т.е. на первом шаге - значение вектора ХоСО). После этого по сигналам управления из блока S осуществляется установка в нуль сумматора 6. С поступлением сигналов из блока 5 управления на управляющие . входы элемента И 14 коммутатора 2, значение вектора дискрет, хранящегося в запоминаюцем регистре 33, поступает через открывщийся элемент И 14 на первые входы элементов ИЛИ 17 блока 3 реккурентных вьгчислений и с выходов блока 17 - на первые входы блока 18 умножителей. После этого по ситайлам управления, поступающим из блока 5 управления на управляющие входы блока 4 памяти, осуществляется считывание из блока 4 на вторые входы элементов ИЛИ 19 значения вектора дискрет Fi(X) По сигналам управления из блока 5, пос;тупающим на управляющие входы блока 20 накапливающих сумматоров, осуществля- ется суммирование вектора Fi (), поступающего на входы блока 2 с выходов элементов ИЛИ 19, с величиной, находящейся в блоке 20 (в первом Шкле работы системы ВТО - код нуля). После этого по сигналам управления из блока 5 осуществляется считывание из блока 4 памяти на вторые входы блока 18 умножителей величины. (Ai(0)) значение произведения (- А (О) Xi (О) ) поступает с выходов блока 18 через блок 19 на входЬ блока 20 сумматоров, где суммируется в следующем такте работы системы (при поступлении сигаалов управления вз блока 5) с величиной, находящейся в бпоке 20 (в первом цикле работы системы это - вектор Р{(ху В следующем такте из блока 4 памяти на вторые входы второго блока 21 умножителей считьшацтся соответствующее значение коэффициента H/(Kt-| - на выходах блока 21 формируется значение Вектора дискрет . X-}()/isO а на выходах блока 22 инверторов знака - его инверсное значение. В следующем такте полученный вектор диокрет поступает на сумматор 6 и через открытый единичным сигналом с инверсного выхода управляющего триггера 27 элемент И 28 коммутатора 7 на первые входы элементов ИЛИ 8. В сумматорах 6 и 9 по сигналам управления из блока 5 определяются значения выражения Хтн (0) Х| (i) .и левой части неравен-, 11 ства 21 (Н) Х.(К)-Х. ,(0)6 соответственi 0 НО. в следующем такте проверяется в блоке 1О сравнения выполнение условия неравенства. Если оно выполнено и пере-, крыт весь интервал интегрирования,то осуществляется останов вычислений. Если условие окончания не выполнено, то из блока 5 управления последовательно подаются управляющие сигеалы на запоми нающие регистры 25 и 24 блока сдвига ;, 11 - осуществляется сдвиг записанного в регистре 24 значения вектора дискрет Хо(0) в регистр 25, а значение нового вектора дискрет (О) с выхода сумматора 6 записывается в регистр 24,следующем такте работы подаются управляющие сигналы на элемент ИЗО оммутатора 7 , и новое значение вектоа дискрет XiviCO) через открытый элеент И 30 поступает на первые входы лока 1 сдаига информации вместо предыущег о вектора fo(O) поступавшего з блока 4 памяти. После этого осущестляется установка в нуль, аналогично опи771санному выше, регастров 33, 23 и 12 сумматоров 20, 6 и 9 блока 10 сравнения и управляющего триггера (возврат в метку №1), и производится следукмций, шаг вычислений: определяется вектор /шй крет Х;. (1с). Если условнае окончания не выполнено, то осуществляется установка в цуль блока 20 накагахивакщих сумматоров и иамен Шё соЬтояния управляющего триггера 27 на противоположное - единичный сих нал с его прямого выхода открывает второй элемент И 29, а нулевой d нвверс ногоТвыхода - закрывает первыми элемент И 28 коммутатора 7 в следующем цикле вычислений, на вход сумматора 9 поступает инверсное значение вектора дискрет с выходов блока 22 инверторов. По сиг.налу утфавления из блока, 5 открывается элемент И 13 коммутатора 2 и значение вектора дискрет с вторых вь ходов блока 3 раккурен-гаых вычислений через открытый элемент И 13 поступает на вторые входы блока 1 сдвига информации. После этого осуществляется возврат в метку № 2 алгоритма работы си- сталы;в регистр 23 блока 1 записывает ся значение вектора дискрет )Co(0)j в ре гистр 33 - значение вектора дискрет оС) и аналогично описаЕтому выше вычисляется вектор тскрет Хо ( 2). Описываемое устройство благодаря наличию новьлх элемевтов и связей между ними позволяет повысить точность решения систем дифференциальных уравнений. Формула азоб р ё Т е н в я 1. Устройство для решения систем диф ференциальных уравнений, содержсшее блок управления, блок памяти, iotepB и второй коммутаторы, 6 т Л и ч а ю щ е е с я Тем, что, с целью повышения точности устройства, в него дополнительно введены первый и второй блоки сдвига, блок рек- курентных вычислений, первый и второй сумматоры, элементы ИЛИ и блок сравнения, причем первый, второй и третий выходы блока памётИ подключены ооот- вё1чявенно к первому, второму и третьему входам блока реккурентвых вычислений первый вь1ход которого соединш с первым .входом первого коммутатора, первый вы ХОД которого подключён к первому вхойу первого бпокв сдвига, первый, второй и третий вьосоды которого соединёаы с вто- 1РЙМ, TtpeTbBM н четвертым входами го коммутатора, второй, третий и четвертый выходы которого подключены к чет вертому, пятому и шестому входам блока реккурентных вычислений, второй выход которого соединен с первым входом второго коммутатора, второй вход которого подключен к входу первого сумматора и к первому, выходу блока реккурентных вычирлений., выход первого сумматора, соединен с первым входом второго блока сдвига и с вторым входом BTqporo коммутатора, первый, второй и третий выходы которо- то подключены к первому, второму и третьему входам элемента ИЛИ, выход которого соединен с входом второго сумматора, выход которого подключен к входу блока сравнения, выход которого соединен с входом блока управления, четвертый и пятый выходы блока памяти подключены соответственно к второму и третьему входам вто.рого блока сдвига, .выход которого соединш с третьим входом второго коммутатора, четвертый вход которого подключен к второму выходу блока рекку- рентньк вычислений, четвертый выход второго коммутатора соединен с вторым входом первого коммутатора, третий вход кйтброго подключен к шестому вьрсоду блока памяти, управляющие входы первого и второго бйока сдвигов, блока памяти, блока реккурентных вычислений, первого и второго сумматора, первого и второго коммутатора, блока сравнения соединены с соответствующими выходами блока управления, 2. Устройство по п. 1, отличающее с я тем, что блок реккурентных вычислений содержит блоки умножения. сумматор, инвертор и элементы ИЛИ, выход первого из которых подключен к первому входу первого блока умножения, второй вход которого является первым входом б;лока реккурйитньЬс вычислений, выход блока умножения подключен к первому входу второго элемента ИЛИ, выход зкоторого соединен с входом сумматора, выход которого подключен к первому вхо™, ду второго блока умножения, выход которого является первым выходом блока реккурентных вычислений и соединен с входом инвертора, выход которого является вторым выходом блока реккурентных вычислений, вторые входы второго элемента ИЛИ и второго блока умножение являются соответственно вторым и третьим входами блока реккуренттилх вычислений, первый, второй и третий входы первого элемента ИЛИ являются соответственно чет9 71777810

вертым, пятым и шестым входами бло-1. Авторское свидетельство СССР

ка реккурентных вычислений, управляющий№ 481041, кл. Q 06 Q 7/34,

вход сумматора является управляющим15.08.75.

входом блока реккурентных вычислений.2. Авторское свидетельство СССР

Источники информации,5 № 463980, кп. G- 06 Т 1/02,

првнятые во внимание при экспертизе05.05.75 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714407A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU705454A1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Устройство управления векторным процессом | 1979 |

|

SU866559A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| УСТРОЙСТВО ОБРАБОТКИ ЦВЕТНЫХ ИЗОБРАЖЕНИЙ | 1999 |

|

RU2159958C1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714406A1 |

| Устройство для решения системы алгебраических уравнений | 1982 |

|

SU1024932A2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

±г

-

« - г /

РЛг ГчА. JLJ т

±1 2ii- -Zl 25

ш

иЦл,Цл

и

Авторы

Даты

1980-02-25—Публикация

1977-10-03—Подача