Изобретение относится к вычислительной технике и может быть использовано в подсистемах обмена информацией в вычислительных системах и многомашинных комплексах с шинной архитектурой в качестве унифицированного буферного запоминающего устройства (ЬЗУ).

Целью изобретения является расширение области применения устройства за счет возможности организации его резервирования.

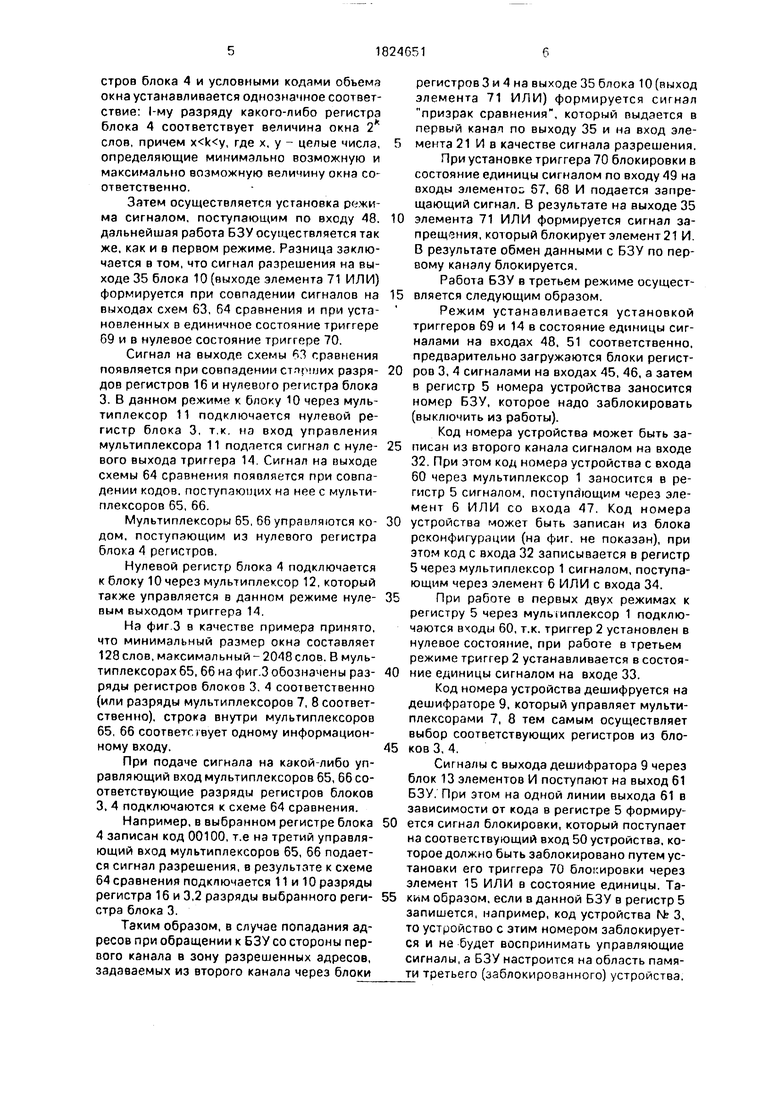

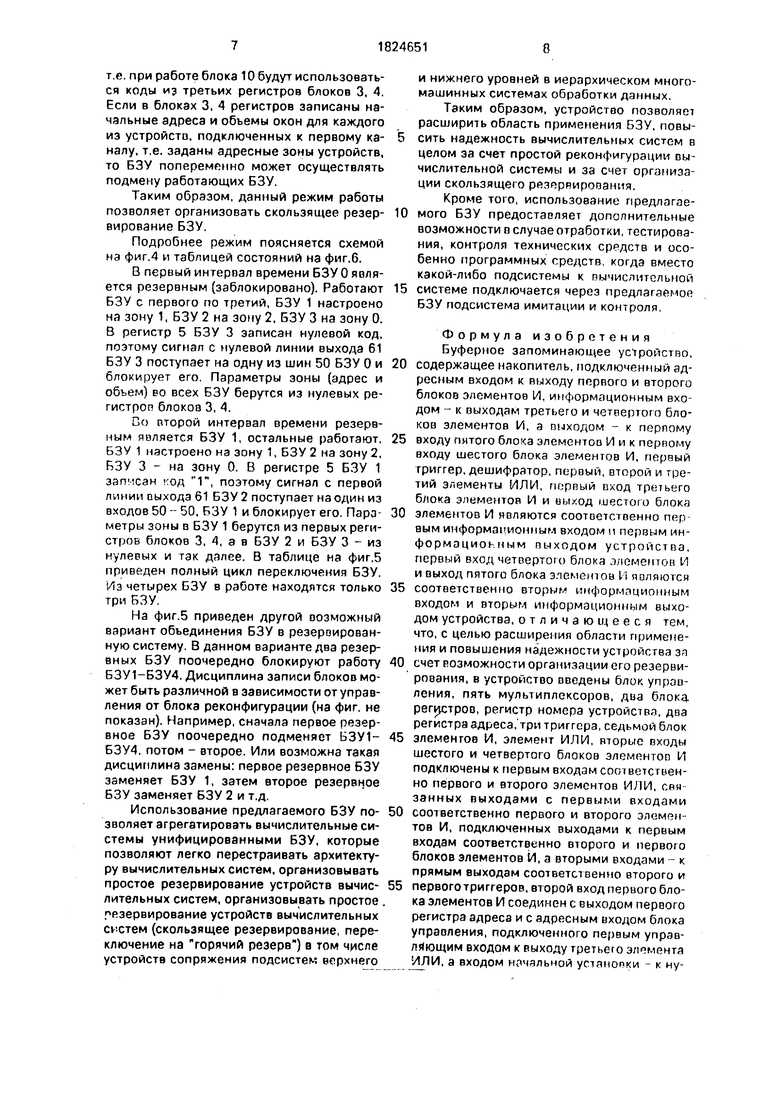

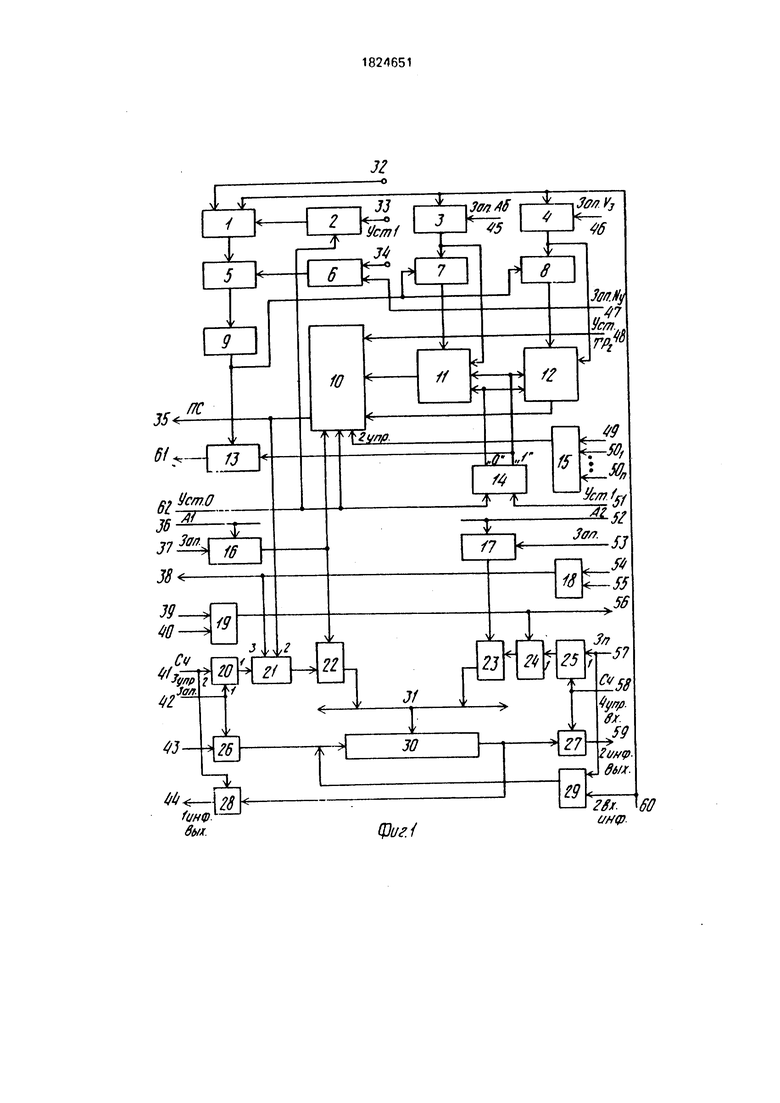

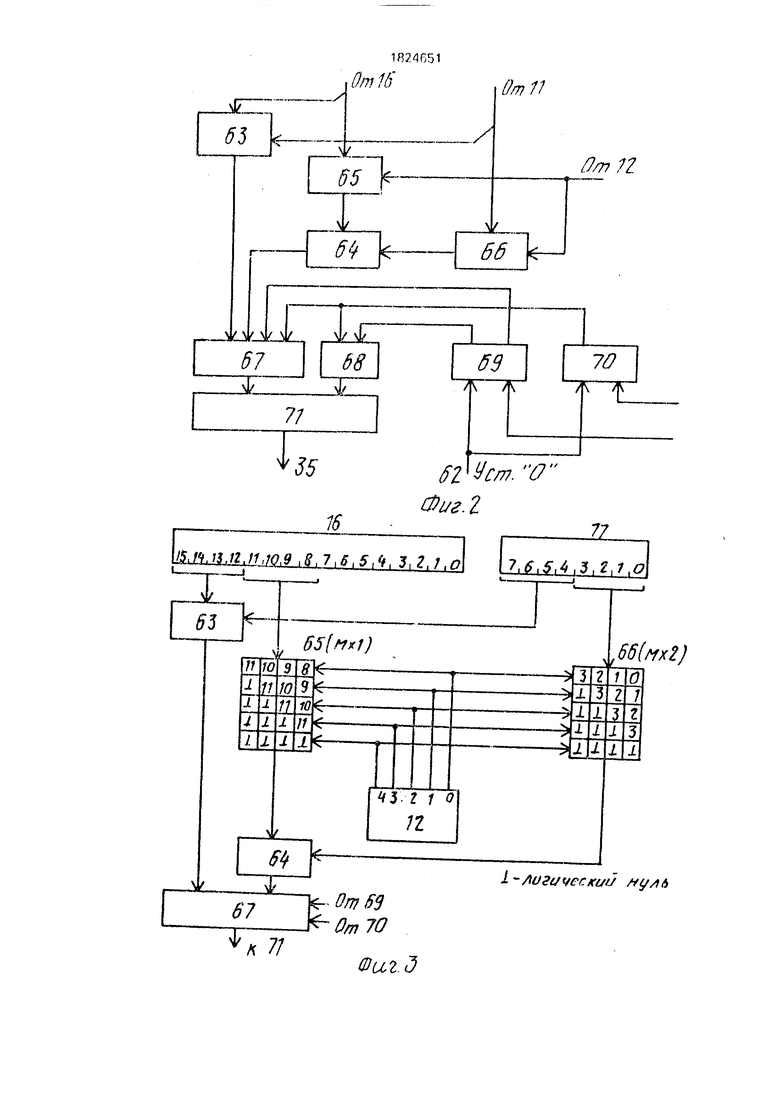

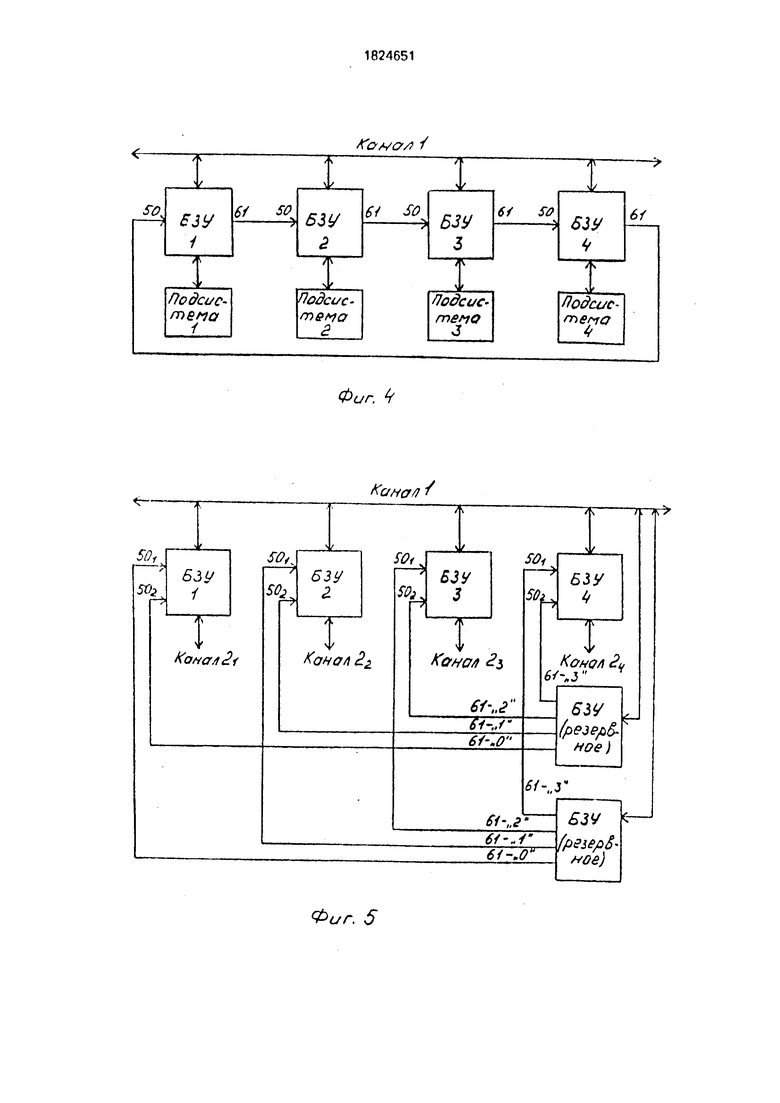

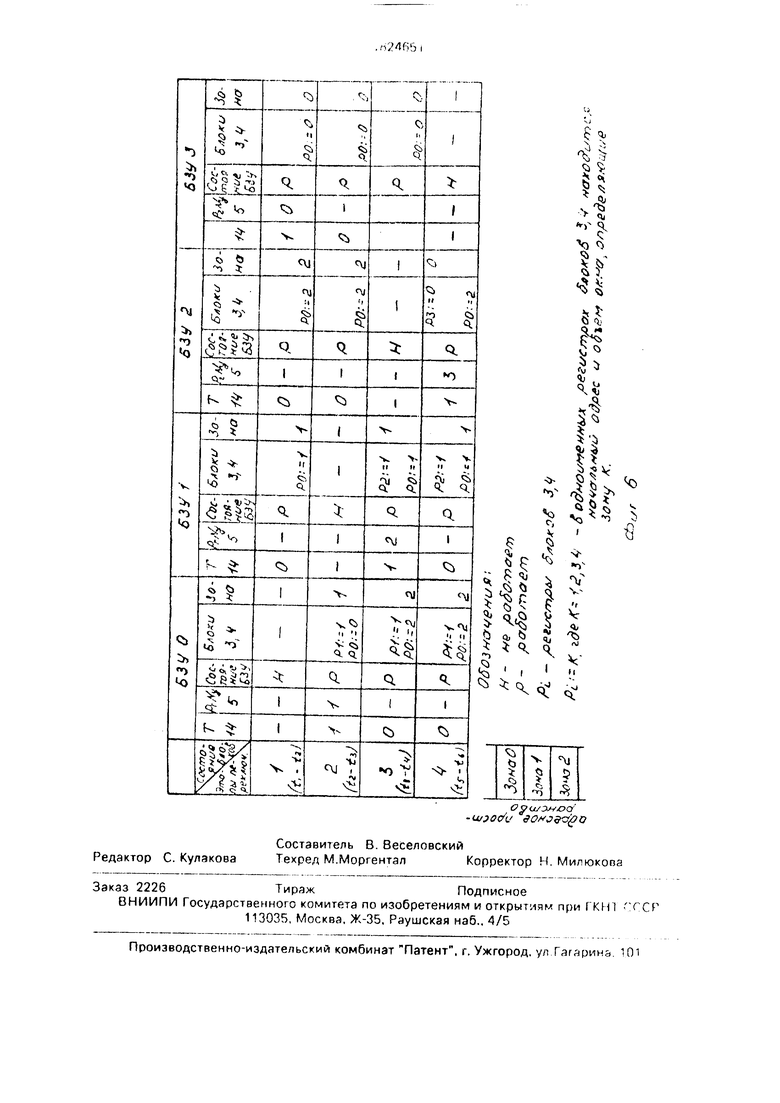

На фиг.1 представлена схема устройства; на фиг.2 - схема блока управления; на фиг.З - схема, поясняющая логику управления окном; на фиг.4, 5 - пример объединения БЗУ в резервированную систему; на фиг.6 - таблица состояния БЗУ, поясняющая работу БЗУ в схеме, приведенной на фиг.4.

Устройство содержит пятый мультиплексор 1, четвертый триггер 2, первый и второй блоки 3,4 регистров, регистр 5 номера устройства, четвертый элемент 6 ИЛИ, третий и четвертый мультиплексора 7, 8, дешифратор 9, блок 10 управления, первый и второй мультиплексоры 11, 12, седьмой блок 13 элементов И, третий триггер 14, третий элемент 15 ИЛИ, первый и второй регистры 16, 17 адреса, второй и первый триггеры 18, 19, первый элемент ИЛИ 20, первый элемент И 21, первый и второй блоки 22, 23 элементов И, элемент И 24, второй элемент ИЛИ 25, третий, пятый, шестой и четвертый блоки 26-29 элементов И. накопитель 30, адресный вход 31 накопителя,

оэ

ю

-Ьь

о ел

пины 32-34 управления, третий информационный пход устройства 32, установочные входы 33, 34. второй управляющий выход 35, первый адресный вход 36, первый управляющий вход записи 37, третий управляющий выход 38, установочные входы 39, 40, шестой и второй управляющие входы 41,42, первые информационные вход 43 и выход 44 устройства, третий четвертый управляющий входы 45, 46 записи, девятый управляющий вход 47, установочный вход 48, пятый управляющий вход 49, блокирующие входы 50.1- 50.п, установочный вход 51. второй адресный вход 52, второй управляющий вход записи 53, установочные входы 54, 55, первый управляющий выход 56, седьмой управляющий вход 57, перпый управляющий вход 58, второй информационный выход 59, второй информационный вход 60, четвертый управляющий выход 61 устройства, вход начальной установки 62. Блок управления (фиг.2) включает схемы сравнения 63- 64, мультиплексоры 65, 66, элементы И 67, 68, триггер режима и блокировки 69, 70, элемент И 71.

Устройство работает следующим образом,

Возможна работа БЗУ в следующих режимах:

а) режим без ограничения окна, С) pf жим обмена через управляемое окно.

в) режим скользящего резервирования, Обращение к ПЗУ осуществляется через

Д.-Л - JiS- ЯЛП.

Обращение к накопителю 30 осуществляется по адресам, которые записываются в регистры 16, 17 адреса и поступают в накопитель 30 через блоки 22, 23 элементов И, из другие входы которых подаются управляющие сигналы.

При работе в первом режиме БЗУ обменивается данными через оба канала одинаково. При этом местоположение разрешенная зона адресов окна не з. дается. В случае обращения к данному БЗУ в устройство поступают сигналы управления по шинам 41, 42 (57, 58).

Перед началом работы БЗУ устанавливается я исходное состояние. Триггер 69 режима и триггер 70 блокировки, триггеры 14, 2, триггеры 19, 18 (разрешения обращения) устанавливаются в нулевое состояние.

БЗУ начинает обмен данными с активным каналом после прихода управляющего сигнала по входу 39 (54) установки разрешения обращения (активный канал - это канал, который находится в состоянии обмена данными с БЗУ). При этом триггер 19 (18) устанавливается в единичное состояние.

. эя второму каналу (первому) сигналом на входе 56 (38) обращение в БЗУ. Одновременно разрешается прохождение сигналов управления через элемент

24 (21) И.

В процессе обмена данными через активный канал на вход 58 (41) поступает сигнал, обеспечивающий считывание данных по адресу из регистра 17(16). Ее вывод производится в канал по выходу 59 (44). На вход 57 (42) поступает сигнал, обеспечивающий запись принимаемой из активного канала по входу 60 (43) данных по адресу из регистра 17 (16). При этом с выхода элемента ИЛИ

5 25 (20) и единичного выхода триггера 19(18) на входы элемента И 24 (21) подаются разрешающие сигналы. Разрешающий сигнал на выходе 35 блока 10 (выход элемента 71 ИЛИ) (в случае обраа1енип к БЗУ от первого

0 канала) формируется при условии наличия сигнала на выходе элемента И 68, т.е. когда триггеры 69, 70 находятся в нулевом состоянии.

После окончания обмена по активному

5 каналу осуществляется сброс триггера 19 (18) сигналом на входе 40 (55) в нулевое состояние. Тем самым запрещается обращение к БЗУ со стор.оны канала, который был актиьным.

0 Затем осуществляется установка в состояние единицы триггера 18 (19) сигналом на входе 54 (39). Тем сзмым разрешается обращение к БЗУ со стороны канала, который был пассивным (т .е. не осуществлял об5 мен данными). Таким образом, активным становится другой канал, который осуществляет обмен данными с БЗУ аналогично, т .е, как описано выше, только по сигналам, указанным в скобках

0 Работа ЬЗУ во нтором режиме осуществляется следующим образом.

Для обмена данными между двумя каналами в адресном пространстве первого ка-г нала отводится зона адресов (окно).

5 Величина окна задается для каждого конкретного случая. БЗУ осуществляет обмен данными по первому каналу между устройства, подключенными к первому каналу (на фиг.1,2.3 не показаны), и БЗУ через любые

0 заданные окна.

Режим устанавливается сигналом на входе 48. При этом триггер 69 устанавливается в единичное состояние. В блок регистров 3 предварительно заносятся адреса

5 окон сигналами, поступающими по входу 45 и в блок 4 регистров заносятся условные коды обьемов окон сиг налами, поступающими по входу 46.

Условные коды объема окна задаются в позиционном коде. Между разрядами рогистрое блока 4 и условными кодами объема окна устанавливается однозначное соответствие: l-му разряду какого-либо регистра блока 4 соответствует величина окна 2 слов, причем , где х, у - целые числа, определяющие минимально возможную и максимально возможную величину окна соответственно.

Затем осуществляется установка режима сигналом, поступающим по входу 48. дальнейшая работа БЗУ осуществляется так же, как и в первом режиме. Разница заключается в том, что сигнал разрешения на выходе 35 блока 10 (выходе элемента 71 ИЛИ) формируется при совпадении сигналов на выходах схем 63, 64 сравнения и при установленных в единичное состояние триггере 69 и в нулевое состояние триггере 70.

Сигнал на выходе схемы 3 сравнения появляется при совпадении старших разрядов регистров 16 и нулевого регистра блока 3. В данном режиме к блоку 10 через мультиплексор 11 подключается нулевой регистр блока 3, т.к. на вход управления мультиплексора 11 подается сигнал с нулевого выхода триггера 14. Сигнал на выходе схемы 64 сравнения появляется при совпадении кодов, поступающих на нее с мультиплексоров 65, 66.

Мультиплексоры 65, 66 управляются кодом, поступающим из нулевого регистра блока 4 регистров.

Нулевой регистр блока 4 подключается к блоку 10 через мультиплексор 12, который также управляется в данном режиме нулевым выходом триггера 14.

На фиг 3 в качестве примера принято, что минимальный размер окна составляет 128 слов, максимальный-2048 слов. В мультиплексорах 65,66 на фиг.З обозначены разряды регистров блоков 3, 4 соответственно (или разряды мультиплексоров 7, 8 соответственно), строка внутри мультиплексоров 65, 66 соответглвует одному информационному входу.

При подаче сигнала на какой-либо управляющий вход мультиплексоров 65, 66 соответствующие разряды регистров блоков 3, 4 подключаются к схеме 64 сравнения.

Например, в выбранном регистре блока 4 записан код 00100, т.е на третий управляющий вход мультиплексоров 65, 66 подается сигнал разрешения, в результате к схеме 64 сравнения подключается 11 и 10 разряды регистра 16 и 3,2 разряды выбранного регистра блока 3.

Таким образом, в случае попадания адресов при обращении к БЗУ со стороны первого канала в зону разрешенных адресов, задаваемых из второго канала через блоки

регистров 3 и 4 на выходе 35 блока 10 (выход элемента 71 ИЛИ) формируется сигнал призрак сравнения, который выдается в первый канап по выходу 35 и на вход эле- 5 мента 21 И в качестве сигнала разрешения. При установке триггера 70 блокировки в состояние единицы сигналом по входу 49 на входы элементов 57, 68 И подается запрещающий сигнал. В результате на выходе 35

0 элемента 71 ИЛИ формируется сигнал запрещения, который блокирует элемент 21 И. В результате обмен данными с БЗУ по первому каналу блокируется.

Работа БЗУ в третьем режиме осущест5 вляется следующим образом.

Режим устанавливается установкой триггеров 69 и 14 в состояние единицы сигналами на входах 48. 51 соответственно, предварительно загружаются блоки регист0 ров 3, 4 сигналами на входах 45, 46, а затем в регистр 5 номера устройства заносится номер БЗУ, которое надо заблокировать (выключить из работы).

Код номера устройства может быть за5 писан из второго канала сигналом на входе 32. При этом код номера устройства с входа 60 через мультиплексор 1 заносится в регистр 5 сигналом, поступающим через элемент 6 ИЛИ со входа 47. Код номера

0 устройства может быть записан из блока реконфигурации (на фиг. не показан), при этом код с входа 32 записывается в регистр 5 через мультиплексор 1 сигналом, поступающим через элемент 6 ИЛИ с входа 34.

5 При работе в первых двух режимах к регистру 5 через мульишлексор 1 подключаются входы 60, т.к. триггер 2 установлен в нулевое состояние, при работе в третьем режиме триггер 2 устанавливается в состоя0 ние единицы сигналом на входе 33.

Код номера устройства дешифруется на дешифраторе 9, который управляет мультиплексорами 7, 8 тем самым осуществляет выбор соответствующих регистров из бло5 ков 3, 4.

Сигналы с выхода дешифратора 9 через блок 13 элементов И поступают на выход 61 БЗУ. При этом на одной линии выхода 61 в зависимости от кода в регистре 5 формиру0 ется сигнал блокировки, который поступает на соответствующий вход 50 устройства, которое должно быть заблокировано путем установки его триггера 70 блокировки через элемент 15 ИЛИ в состояние единицы. Та5 ким образом, если в данной БЗУ в регистр 5 запишется, например, код устройства № 3, то устройство с этим номером заблокирует- ся и не будет воспринимать управляющие сигналы, а БЗУ настроится на область памяти третьего (заблокированного) устройства.

т.е. при работе блока 10 будут использоваться коды из третьих регистров блоков 3, 4, Если в блоках 3, 4 регистров записаны начальные адреса и объемы окон для каждого из устройсто, подключенных к первому каналу, т.е. заданы адресные зоны устройств, то БЗУ попеременно может осуществлять подмену работающих БЗУ.

Таким образом, данный режим работы позволяет организовать скользящее резервирование БЗУ.

Подробнее режим поясняется схемой на фиг.4 и таблицей состояний на фиг.6.

В первый интервал времени БЗУ 0 является резервным (заблокировано). Работают БЗУ с первого по третий, БЗУ 1 настроено на зону 1, БЗУ 2 на зону 2, БЗУ 3 на зону 0. В регистр 5 БЗУ 3 записан нулевой код, поэтому сигнал с нулевой линии выхода 61 БЗУ 3 поступает на одну из шин 50 БЗУ 0 и блокирует его. Параметры зоны (адрес и объем) во всех БЗУ берутся из нулевых ре- гистроп блоков 3, 4.

Со второй интервал времени резервным является БЗУ 1, остальные работают. БЗУ 1 настроено на зону 1, БЗУ 2 на зону 2, БЗУ 3 - на зону 0. В регистре 5 БЗУ 1 запмсан код 1, поэтому сигнал с первой линии выхода 61 БЗУ 2 поступает на один из входов 50 -- 50, БЗУ 1 и блокирует его. Параметры зоны в БЗУ 1 берутся из первых регистров блоков 3, 4, а в БЗУ 2 и БЗУ 3 - из нулевых и гак далее. В таблице на фиг,5 приведен полный цикл переключения БЗУ. I/is четырех БЗУ в работе находятся только три БЗУ,

На фиг.5 приведен другой возможный вариант объединения БЗУ в резероирован- ную систему. В данном варианте два резервных БЗУ поочередно блокируют работу БЗУ1-БЗУ4. Дисциплина записи блоков может быть различной в зависимости от управления от блока реконфигурации (на фиг, не показан). Например, сначала первое резервное БЗУ поочередно подменяет БЗУ1- БЗУ4. потом - второе. Или возможна такая дисциплина замены: первое резервное БЗУ заменяет БЗУ 1, затем второе резервное БЗУ заменяет БЗУ 2 и т,д.

Использование предлагаемого БЗУ позволяет агрегатировать вычислительные системы унифицированными БЗУ, которые позволяют легко перестраивать архитектуру вычислительных систем, организовывать простое резервирование устройств вычислительных систем, организовывать простое резервирование устройств вычислительных систем (скользящее резервирование, переключение на горячий резерв) в том числе устройств сопряжения подсистем верхнего

и нижнего уровней в иерархическом многомашинных системах обработки данных.

Таким образом, устройство позволяет расширить область применения БЗУ, повысить надежность вычислительных систем в целом за счет простой реконфигурации вычислительной системы и за счет организации скользящего резервирования.

Кроме того, использование предлагаемого БЗУ предоставляет дополнительные возможности в случае отработки, тестирования, контроля технических средств и особенно программных средств, когда вместо какой-либо подсистемы к пычислительной

системе подключается через предлагаемое БЗУ подсистема имитации и контроля.

Формула изобретения Буферное запоминающее устройство,

содержащее накопитель, подключенный адресным входом к выходу первого и второго блоков элементов И, информационным входом - к выходам третьего и четвертого блоков элементов И, а выходом - к перпому

входу пятого блока элементов И и к первому входу шестого блока элементов И, первый триггер, дешифратор, первый, второй и третий элементы ИЛИ, пг-рпый сход третьего блока элементов И и выход шестого блока

элементов И являются соответственно первым информационным входом п первым информационным выходом устройства, первый вход четверток) блока ллеметов И и выход пятого блока элементов Л являются

соответственно вторым информационным входом и вторым информационным выходом устройства, отличающееся тем, что, с целью расширения области применения и повышения надежности устройства за

счет возможности организации его резервирования, в устройство введены блок управления, пять мультиплексоров, два блока, регистров, регистр номера устройствл, два регистра адреса, три триггера, седьмой блок

элементов И, элемент ИЛИ, вторые входы шестого и четвертого блоков элементов И подключены к первым входам соот ветствен- но первого и второго элементов ИЛИ, CRH занных выходами с первыми входами

соответственно первого и второго элементов И, подключенных выходами к первым входам соответственно второго и первого блоков элементов И, а вторыми входами - к прямым выходам соответственно второго и

первого триггеров, второй вход первого блока элементов И соединен с выходом первого регистра адреса и с адресным входом блока управления, подключенного первым управляющим входом к выходу третьего элемента ИЛИ, а входом начальной установки - к нулевому входу третьего триггера, связанного инверсным выходом с первыми управляющими входами первого и второго мультиплексоров, а единичным выходом - с первым входом седьмого блока элементов И и с вторыми управляющими входами первого и второго мультиплексоров, подключенных выходами соответственно к первому и второму информационным входам блока управления, первыми информационными входами соответственно - к выходам первого и второго блоков регистров и к информационным входам соответственно третьего и четвертого мультиплексоров, соединенных выхо ;ами с вторыми информационными входами соответственно первого и второго мультиплексоров, а управляющими входами - с вторым входом седьмого блока элементов И и с выходом дешифратора, связанного входом с выходом регистра номера устройства, подключенного входом разрешения записи к выходу четвертого элемента ИЛИ, а информационным входом - к выходу пятого мультиплексора, соединенного управляющим входом с прямым выходом четвертого триггера, первым инфор, ционным входом с информационными входами первого и второго блоков регистров и с первым входом четвертого блока элементов И, второй вход второго блока элементов И подключен к выходу второго регистра адреса, второй вход второго элементов ИЛИ и второй вход пятого блока элементов И объединены и являются первым управляющим входом устройства, второй вход первого элемента ИЛИ и второй вход третьего

блока элементов И объединены и являются вторым управляющим входом устройства, нулевой и единичный входы первого, второго триггеров и единичные входы третьего триггера и четвертого триггера, установочный вход блока управления являются соответствующими установочными входами устройства, а нулевые входы третьего и четвертого триггеров являются входом нэчальнойустановкиустройства,

информационные входы первого и второго регистров адреса являются соответственно первым и вторым адресными входами устройства, входы разрешения записи первого

и второго регистров, первого и второго блоков регистров являются соответственно первым, вторым, третьим и четвертым управляющими входами записи устройства, второй информационный вход пятого мультиплексора является третьим информационным входом устройства, первый вход и группа входов третьего элемента ИЛИ являются соответственно пятым управляющим входом устройства и группой блокирующих

входов устройства, первые входы первого и второго элементов ИЛИ, первый и второй входы четвертого элемента ИЛИ являются соответственно шестым, седьмым, восьмым и девятым управляющими входами устройствэ, прямой выход первого триггера, объединенные выход блока управления и третий вход первого элемента И, прямой выход второго триггера и выход седьмого блока элементов И являются соответственно первым,

вторым, третьим и четвертым управляющими выходами.

Фиа.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1990 |

|

SU1711233A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278981A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Многоканальное запоминающее устройство | 1990 |

|

SU1805497A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

Изобретение относится к вычислительной технике, в частности к подсистемам обмена информацией вычислительных систем и многомашинных комплексов с шинной архитектурой. Буферное запоминающее устройство представляет собой унифицированное устройство, которое может применяться для агрегатирования обычных и высоконадежных резерьированных вычислительных систем. Изобретение позволяет эффективно применять его в подсистемах контроля и в высоконадежных многомашинных комплексах. Цель изобретения - расширение области применения устройства за счет возможности организации его резервирования. Буферное запоминающее устройство содержит накопитель, два регистра адреса, четыре триггера, два элемента ИЛИ, два элемента И, семь блоков элементов И. блок управления, пять мультиплексоров, два блока регистров, регистр номера устройства, дешифратор. 6 ил. (Л С

Фиг.З

ю

Ј ЧГ см со

h i

a

o

с ъ

в

ч

3

| Буферное запоминающее устройство | 1976 |

|

SU583476A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-06-30—Публикация

1991-01-25—Подача