Изобретение относится к вычислительной технике и может быть использовано в подсистемах обмена информацией в вычислительных системах и многомашинных комплексах с шинной архитектурой в качестве буферного запоминающе- го устройства (БЗУ).

Целью изобретения является расширение области применения устройства за счет управления положением и веля-- чиной зоны в адресном пространстве вычислительной системы.

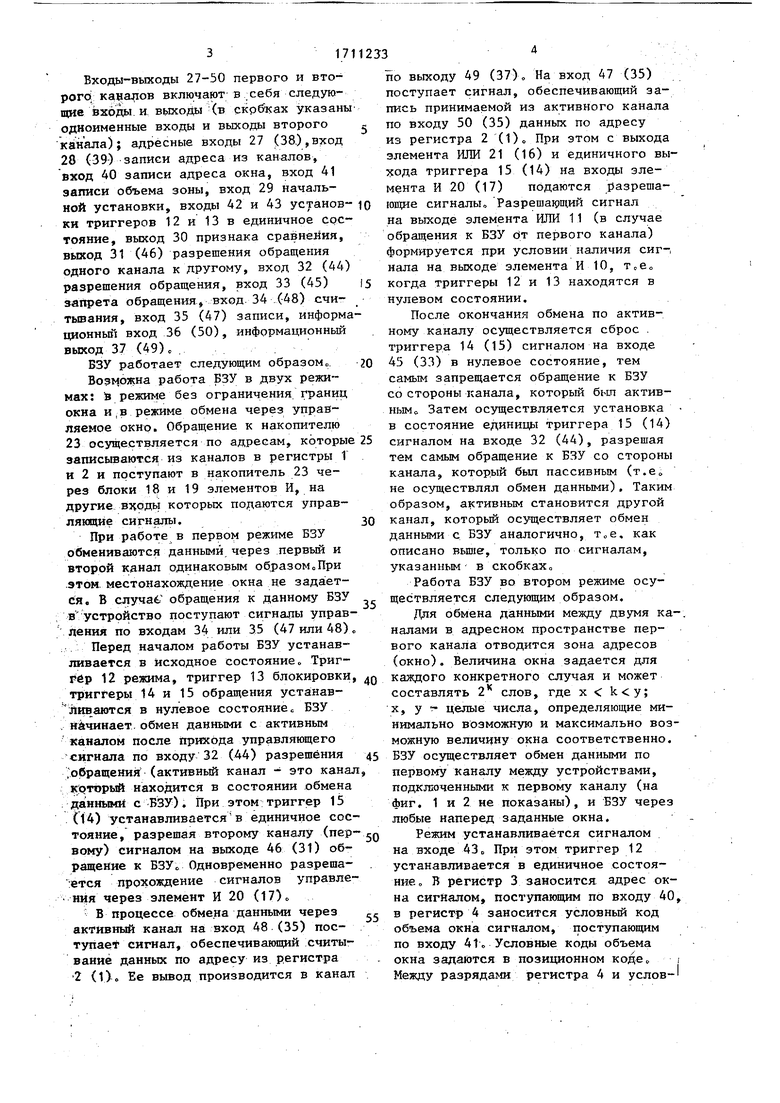

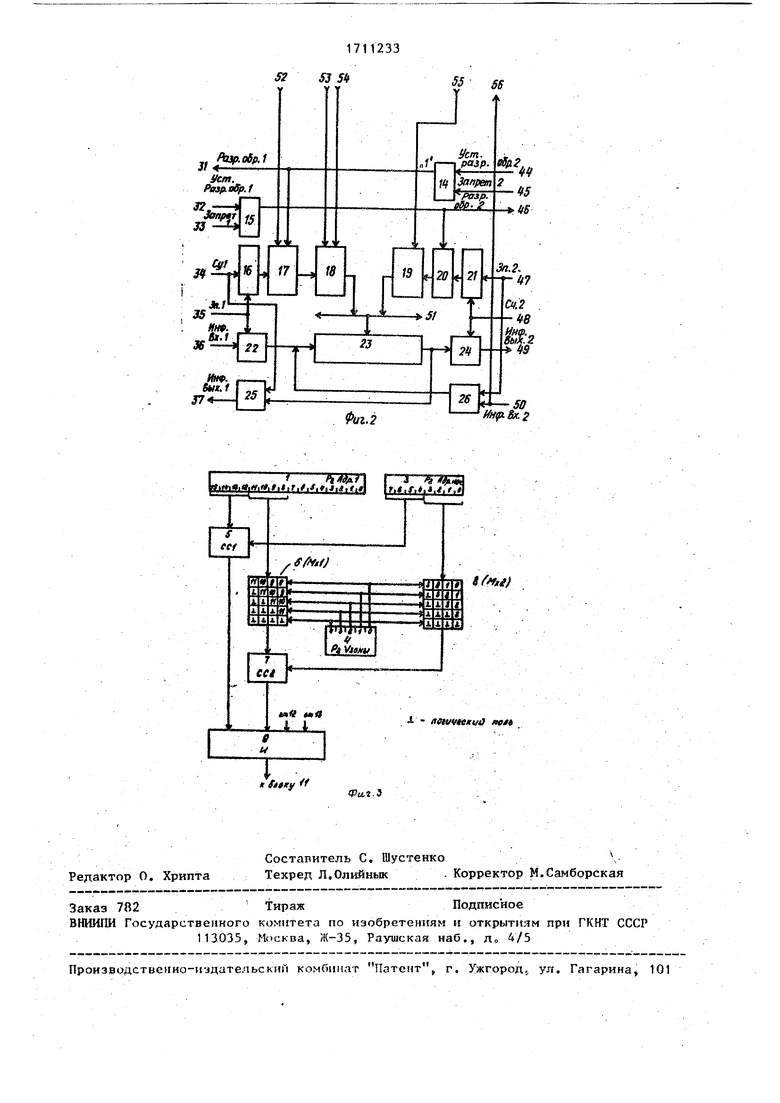

На фиго 1 и 2 представлена схема устройства; на фигс 3 - схема, поясняющая логику управления окном.

БЗУ содержит регистр 1 адреса первого канала, регистр 2 адреса второго канала, регистр 3 адреса окна, регистр 4 объема зоны (окна), блок 5 сравнения, мультиплексор 6/ блок 7 сравнения, мультиплексор 8, элементы И 9 и 10, элемент ИЛИ 11, триггер 12 режима, триггер 13 блокировки БЗУ, триггеры 14 и 15 обращения, эле мент ИЛИ 16, элемент И 17, блоки 18 .и 19 элементов И, элемент И 20, элемент ИЛИ 21, блок 22 элементов И, на копитель 23, блоки 24-26 элементов И входы-выходы 27-37 первого канала, входы-выходы 38-50 второго канала, адресные входы 51. Линии 52-56 обозначены для связи блоков частей БЗУ, приведенных на разных листах фиг,1,2

0

х

со

Входы-выходы 27-50 первого и второго кзцаров включают в себя следующие входы, и выходы -(в скобках указаны одноименные входы и выходы второго канала); адресные входы 27 (38.),вход 28 (39) записи адреса из каналов, вход 40 записи адреса окна, вход 41 записи объема зоны, вход 29 начальной установки, входы 42 и 43 уставов- ки триггеров 12 и 13 в единичное состояние, выход 30 признака сравнения, выход 31 (46) разрешения обращения одного канала к другому, вход 32 (44) разрешения обращения, вход 33 (45) запрета обращения, вход 34-..(-48) счи- тьгоания, вход 35 (47) записи, информационный вход 36 (50), информациейный выход 37 (49)с

БЗУ работает следующим образом.

Возможна работа БЗУ в двух режимах: в режиме без ограничения, границ окна и,в режиме обмена через управляемое окно. Обращение к накопителю 23 осуществляется по адресам, которые записываются из каналов в регистры 1 и 2 и поступают в накопитель 23 через блоки 18. и 19 элементов И, на другие входы которых подаются управляющие сигналы.

При работе в первом режиме БЗУ обмениваются данными через первый и второй канал одинаковым образом„При .этом, местонахождение окна не задается, В случай обращения к данному БЗУ в устройство поступают сигналы управления по входам 34 или 35 (47 или 48)„ -..:.:. Перед началом работы БЗУ устанавливается в исходное состояние Триг

pep 12 режима, триггер 13 блокировки, 4Q каждого конкретного случая и может

триггеры 14 и 15 обращения устанав- ливаютея в нулевое состояние о БЗУ начинает.обмен данными с активным каналом после Прихода управляющего сигнала по входу 32 (44) разрешения обращения (активный канал - это канал, который находится в состоянии обмена

данными с БЗУ). При этом триггер 15 (14) устанавливается в единичное состояние, разрешая второму каналу (первому) сигналом на выходе 46 (31) обращение к БЗУо Одновременно разрешается прохождение сигналов управления через элемент И 20 (17)о

7 В процессе обмена данными через активный канал на вход 48 (35) поступает сигнал, обеспечивающий считывание данных по адресу из регистра 2 (1)„ Ее вывод производится в канал

где х k у;

определяющие ми45

50

55

составлять 2 слов, х, у целые числа, нимально возможную и максимально воз можную величину окна соответственно БЗУ осуществляет обмен данными по первому каналу между устройствами, подключенными к первому каналу (на фиг. 1 и 2 не показаны), и БЗУ через любые наперед заданные окна.

Режим устанавливается сигналом на входе 43„ При этом триггер 12 устанавливается в единичное состояние о В регистр 3 заносится адрес ок на сигналом, поступающим по входу 40 в регистр 4 заносится условный код объема окна сигналом, поступающим по входу 41 о Условные коды объема окна задаются в позиционном кодес Между разрядами регистра 4 и услов

0

5

по выходу 49 (37), На вход 47 (35) поступает сигнал, обеспечивающий запись принимаемой из активного канала по входу 50 (35) данных по адресу из регистра 2 (1)„ При этом с выхода элемента ИЛИ 21 (16) и единичного выхода триггера 15 (14) на входы элемента И 20 (17) подаются разрешающие сигналы Разрешающий сигнал на выходе элемента ИЛИ 11 (в случае обращения к БЗУ Ьт первого канала) формируется при условии наличия сиг-, нала на выходе элемента И 10, тсе0 когда триггеры 12 и 13 находятся в нулевом состоянии.

После окончания обмена по активному каналу осуществляется сброс . триггера 14 (15) сигналом на входе 45 (33) в нулевое состояние, тем самым запрещается обращение к БЗУ со стороны канала, который был актив- нымо Затем осуществляется установка в состояние единицы триггера 15 (14) сигналом на входе 32 (44), разрешая тем самым обращение к БЗУ со стороны канала, который был пассивным (т.е0 не осуществлял обмен данными), Таким образом, активным становится другой канал, который осуществляет обмен данными с БЗУ аналогично, т„е, как описано выше, только по сигналам, указанным в скобках

Работа БЗУ во втором режиме осуществляется следующим образом.

Для обмена данными между двумя ка-, налами в адресном пространстве первого канала отводится зона адресов (окно). Величина окна задается для

где х k у;

определяющие ми5

0

5

составлять 2 слов, х, у целые числа, нимально возможную и максимально возможную величину окна соответственно. БЗУ осуществляет обмен данными по первому каналу между устройствами, подключенными к первому каналу (на фиг. 1 и 2 не показаны), и БЗУ через любые наперед заданные окна.

Режим устанавливается сигналом на входе 43„ При этом триггер 12 устанавливается в единичное состояние о В регистр 3 заносится адрес окна сигналом, поступающим по входу 40, в регистр 4 заносится условный код объема окна сигналом, поступающим по входу 41 о Условные коды объема окна задаются в позиционном кодес Между разрядами регистра 4 и условными кодами объема окна устанавливается однозначное соответствие: i-му разряду регистра 4 соответствует

личина окна 2 слов, причем-х k у. где х, у - целые числа, определяющие минимально возможную и максимально возможную величину окна соответст- (Венноо

Затем осуществляется установка ре- жима сигналом, поступающим по входу 43„ Дальнейшая работа БЗУ осуществляется так же, как и в первом режиме. , Разница заключается в том, что сигнал разрешения на выходе элемента ИЛИ 11 формируется при совпадении сигналов на выходах блоков 5 и 7 сравнения и при установленных в единичное состояние триггера 12 и в нулевое состояние триггера 130

Сигнал на выходе блока 5 сравнения появляется при совпадении старших разрядов регистров 1 и 3. Сигнал на выходе блока 7 сравнения появляется при совпадении кодов, поступающих на него с Мультиплексоров 6 и 8. Мультиплексо- ры 6, 8 управляются кодом, поступающим из регистра 4 объема окна0 Ра фиг с 2 в качестве примера принято, что минимальный размер окна составляет 128 слов, максимальный - 2048 слов В мультиплексорах 6 и 8 на фиго 2 обозначены разряды регистров 1 и 3 соответственно, строка внутри мультиплексоров 6 и 8 соответствует одному информационному входу„ При подаче сигнала на какой-либо управляющий вход мультиплексоров 6, 8 соответствующие разряды регистров 1, 3 подключаются к блоку 7 сравнения

Например, в регистр 4 записан код 00100, т.е. на третий .управляющий вход мультиплексоров 6, 8 подается игнал разрешения, в результате к блоку 7 сравнения подключаются 11 и 10 разря- ды регистра- 1 и 3, 2 разряды регистра Зо Таким образом, в случае попадания адресов при обращении к БЗУ со стороны первого канала в зону разре-т шенных адресов, задаваемых из второго канала через регистры 3 и 4, на выходе 30 элемента ИЛИ 11 формируется сигнал Признак сравнения, который выдается в первый канал по шине 30 и на вход элемента И 17 в качестве сигнала разрешения.

При установке триггера 13 блокировки в состояние единицы сигналом по входу 42 на входы элементов И 9, 10

. j,- о

50 Q

5 j

5

5

подается запрещающий сигнал, в результате на выходе 30 элемента ИЛИ 11 формируется сигнал запрещения, который блокирует элемент И 17. В результате, обмен данными с данным БЗУ по первому каналу блокируется

Использование БЗУ позволяет агрега- тировать вычислительные, системы унифицированными БЗУ, которые позволяют легко перестраивать архитектуру вычислительных систем,организовать простое . резервирование устройств вычислительных систем, (переключение на горячий резерв), в том числе устройств сопряжения подсистем верхнего и нижнего уровней в иерархических многомашинных системах обработки данных

Формула изобретения

Буферное запоминающее устройство, содержащее первый и второй регистры адреса, первый триггер обращения, первый и второй элементы ИЛИ, первый и второй элементы И, накопитель, блоки элементов И с первого по шестой, информационный вход шестого блока „ элементов И является вторым информационным входом устройства, управляющий вход шестого блока элементов И. подключен к первому входу второго элемента ИЛИ и является вторым входом записи устройства, выход шестого блока элементов И подключен к информационному входу накопителя и к выходу третьего блока элементов И, информационный вход которого является пер- вым информационным входом устройства, управляющий вход третьего блока элементов И является первым входом записи устройства и подключен к первому входу первого элемента ИЛИ, второй вход которого является первым входом считывания устройства и подключен к управляющему входу пятого блока элементов И, выход которого является первым информационным выходом устройства, информационный вход пятого блока элементов И подключен к информационному выходу накопителя и к информационному входу четвертого, блока элементов И, выход которого является вторым информационным выходом устройства, управляющий вход четвертого блока элементов И является вторым входом считывания и подключен к второму вхо- - ду второго элемента ИЛИ, выход которого подключен к первому входу второго элемента И, второй вход которого

является вторым выходом разрешения обращения устройства и подключен к выходу первого триггера, вход установки и вход сброса которого являются с соответственно входом разрешения обращения и входом запрета обращения, выход второго элемента И подключен к управляющему входу второго блока элементов И, информационный вход кото- ю poro подключен к выходу второго регистра адреса, информационный и управляющий входы которого являются соответственно адресным входом и вторым входом записи адреса, выход второго t5 блока элементов И подключен к адресному входу накопителя и к выходу первого блока элементов И, первый и второй информационные входы которого соединены соотвественно с первым и 20 вторым выходами первого регистра адреса, информационный и управляющий входы которого являются первым адресным входом и первым входом записи адреса устройства, управляющий вход .первого блока элементов И подключен ,к выходу первого элемента И, первый вход которого подключен к выходу первого элемента ИЛИ, отличающееся тем, что, с целью расширения области применения устройства за счет управления положением и величиной зоны в адресном пространстве вычислительной системы, оно содержит второй триггер обращения, выход кото- рого является первым выходом разрешения обращения устройства и подключен к второму входу первого элемента И, входы установки и сброса второго триггера обращения являются соответственно первыми входами разрешения обращения и запрета обращения устройства, регистр адреса окна, регистр объе- ма зоны, первый и второй блоки срав- дс нения, первый и второй мультиплексоры, третий и четвертый элементы И, триггер режима, триггер блокировки и тре25

30

с 50 дс

5

0

тий элемент ИЛИ, выход которого является выходом признака сравнения устройства и подключен к третьему входу первого элемента И, первый и второй входы третьего элемента ИЛИ Подключены соответственно к выходу третьего элемента И и к выходу четвертого элемента И, первый вход которого подключен к. инверсному выходу (триггера режима, вход сброса которого является входом начальной установки устройства и подключен к входу сброса триггера блокировки, выход которого подключен к второму входу четвертого элемента И и к первому входу третьего элемента И, второй вход которого подключен к прямому выходу триггера режима, входы установки триггеров режима и блокировки являются соответствующими входами устройства, третий и четвертый входы третьего элемента И подключены соответственно к выходу первого блока сравнения и к выходу второго блока сравнения, первый и второй входы которого подключены соответственно к выходам первого и второго мультиплексоров, первые входы которых подключены к выходу регистра объема зоны, вход записи которого является входом записи объема зоны устройства, второй вход второго мультиплексора подключен к первому выходу регистра адреса окна, вход записи которого является входом записи адреса окна устройства, информационные входы регистра адреса окна и регистра объема зоны подключены к информационному входу шестого блока элементов И, второй выход регистра адреса окна подключен к первому входу первого блока сравнения, второй вход которого подключен к первому выходу первого регистра адреса, второй вход первого муль- .типлексора подключен к второму выходу (первого регистра адреса

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1991 |

|

SU1824651A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Многоканальное запоминающее устройство | 1990 |

|

SU1805497A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278981A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

Изобретение относится к вычислительной технике, в частности к подсистемам обмена информацией вычислительных систем и многомашинных комплексов с шинной архитектурой. Цель изобретения - расширение области применения устройства за счет управления положением и величиной зоны в адресном пространстве вычислительной системы. Буферное запоминающее устройство содержит накопитель, два регистра адреса, два триггера обращения, три . элемента ИЛИ, четыре элемента И, . шесть блоков элементов И, регистр адреса окна, регистр объема зоны, два блока сравнения, два мультиплексора, триггер режима, триггер блокировки. Цель достигается тем, что в регистр адреса окна записывается начальный адрес используемой зоны в памяти вычислительной системы, а в регистр объема зоны - величина объема этой зоны В процессе работы осуществляются сравнение текущего адреса с объе- .мом записанных массивов и выявление границ зоны памяти« 3 ил. 8 fe

| Авторское свидетельство СССР | |||

| Буферное запоминающее устройство | 1979 |

|

SU834766A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-02-07—Публикация

1990-04-02—Подача