1

. Изобретение относится к области вычислительной техники, электроники автоматики и, в частности, может быть использовано при разработке больших интегральных схем на дополняющих МДП-транзисторах,

Известны инверторы на дополняющи МДП-транзисторах и логические элеметы, выполняющие различные логические функции, существенными признаками которых является наличие пар дополняющих транзисторов, ц- и р-канальных, в которых сток п-канального транзистора подключен к стоку рканального транзистора и к логическому выходу элемента, затвор м-канального транзистора подключен к затвору р-канального транзистора и к логическому входу элемента, истоки п-канальных транзисторов и их подложки подключены к общей шине, истоки р-канальных транзисторов и их подложки подключены к плюсовой шине l .

Недостатком известных логических элементов является наличие.только одного выхода.

Известен логический элемент, содержащий ряд инверторов на дополняющих МДП-транзисторах, первый инвертор подключен между шинами источника питания, а следующий - между одной из щин источника питания и выходом предыдущего инвертора, причем вход и выход каждого из инверторов являются соответственно входом и выходом элемента, в каждом из инверторов подложки и-канальных транзисторов подключены к общей шине, а под0ложки р-канальных транзисторов - к плюсовой шине 2 .

Недостатком известного элемента является то, что на выходе каждого инверторареализуется только функция

5

,НЕ-И. (либо HiE-ИЛИ) для входных сигналов этого инвертора и всех предшествующих.

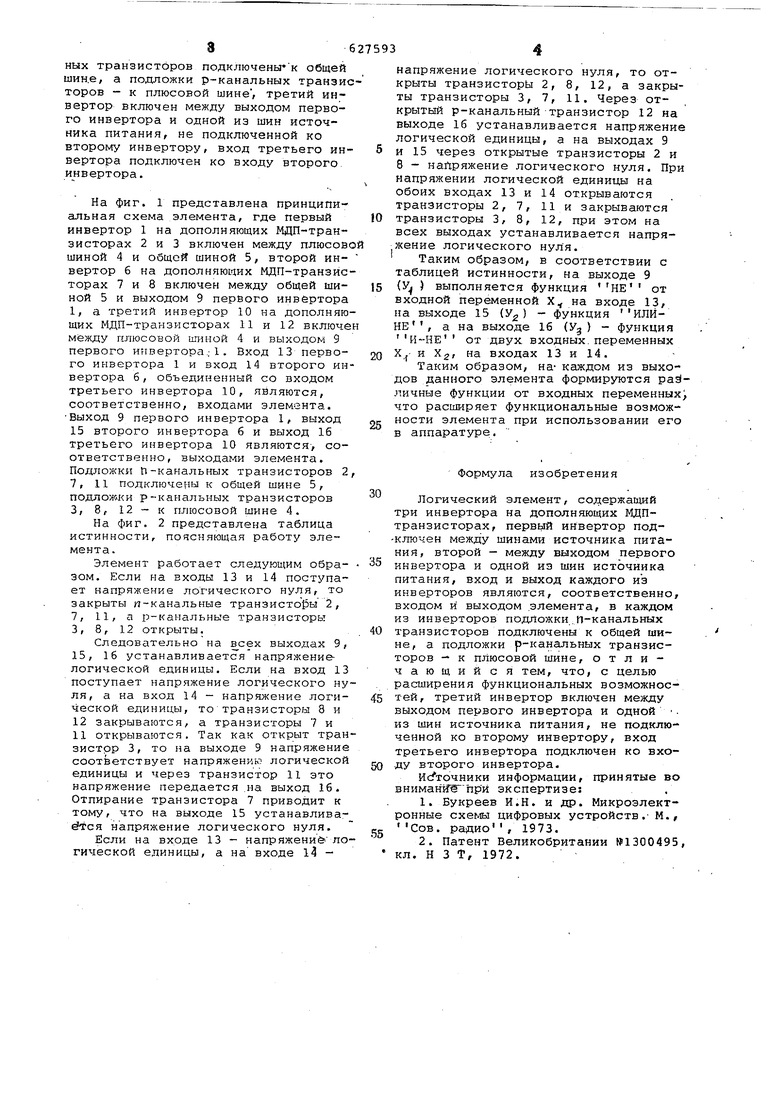

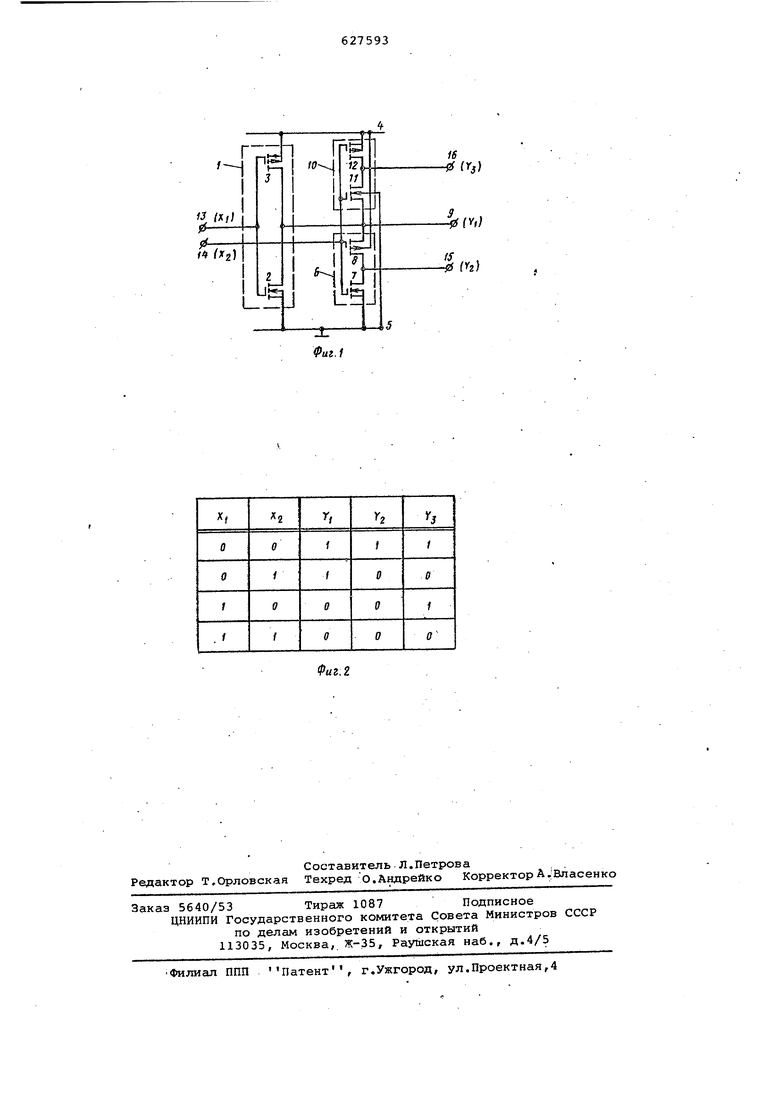

Цель изобретения-- расширение функциональных возможностей элемента. Для достижения поставленной цели в логическом элементе, Содержащем три инвертора на дополняющих МДПтранзисторах, в котором первый инвертор подключен между шинами источ5ника питания,,второй - между выходом первого и одной из шин источника питания, .вход и в.ыход каждого из инверторов являются соответственно входом и выходом элемента, и в каж.домИЗ инверторов подложки п-канальных транзисторов подключены к общей шин.е, а подложки р-канальных транзи торов - к плюсовой шине , третий инвертор включен между выходом первого инвертора и одной из шин источника питания, не подключенной ко второму инвертору, вход третьего ин вертора подключен ко входу второго. инвертора. На фиг. 1 представлена принципиальная схема элемента, где первый инвертор 1 на дополняющих МДП-транзисторах 2 и 3 включен между плюсов шиной 4 и общей шиной 5, второй инвертор 6 на дополняющих МДП-транзис торах 7 и 8 включен между общей шиной 5 и выходом 9 первого инвертора 1, а третий инвертор 10 на дополняю щих МДП-транзисторах 11 и 12 включе между плюсовой шиной 4 и выходом 9 первого инвертора,-1. Вход 13 первого инвертора 1 и вход 14 второго ин вертора 6, объединенный со входом третьего инвертора 10, являются, соответственно, входами элемента. Выход 9 первого инвертора 1, выход 15 второго инвертора б и выход 16 третьего инвертора 10 являются-, соответственно, выходами элемента. Подложки п-канальных транзисторов 2 7, 11 подключены к общей шине 5, ПОДЛОЖ.КИ р-канальных транзисторов 3, 8, 12 - к плюсовой шине 4. На фиг, 2 представлена таблица истинности, поясняющая работу элемента. Элемент работает следующим образом. Если на входы 13 и 14 поступает напряжение логического нуля, то закрыты п-канальные транзисторы 2, 7, 11, а р-канальные транзисторы 3, 8, 12 открыты. Следовательно на всех выходах 9 15, 16 устанавливается напряжениелогической единицы. Если на вход 13 поступает напряжение логического ну ля, а на вход 14 - напряжение логической единицы, то транзисторы 8 и 12 закрываются, а транзисторы 7 и 11 открываются. Так как открыт тран зистор 3, то на выходе 9 напряжение соответствует напряжению логической единицы и через транзистор 11 это напряжение передается .на выход 16. Отпирание транзистора 7 приводит к тому, что на выходе 15 устанавливается напряжение логического нуля. Если на входе 13 - напряжение ло гической единицы, а на входе 14 напряжение логического нуля, то открыты транзисторЬг 2, 8, 12, а закрыты транзисторы 3, 7, 11. Через открытый р-канальный-транзистор 12 на выходе 16 устанавливается напряжение логической единицы, а на выходах 9 и 15 через открытые транзисторы 2 и 8 - напряжение логического нуля. При напряжении логической единицы на обоих входах 13 и 14 открываются транзисторы 2, 7, 11 и закрываются транзисторы 3, 8, 12, при этом на всех выходах устанавливается напряжение логического нуля. Таким образом, в соответствии с таблицей истинности, на выходе 9 {У| ) выполняется функция НЕ от входной переменной Х на входе 13, на выходе 15 (У) - функция ИЛЙНЕ, а на выходе 16 (Уд) - функция И-НЕ от двух входных.переменных на входах 13 и 14. Х.- и Х2/ Таким образом, на- Кс1ждом из выходов данного элемента формируются pasiличные функции от входных переменных; что расширяет функциональные возможности элемента при использовании его в аппаратуре. Формула изобретения Логический элемент, содержащий три инвертора на дополняющих МДПтранзисторах, первь1й инвертор подключен между шинами источника питания, второй - между выходом первого инвертора и одной из шин источника питания, вход и выход каждого из инверторов являются, соответственно, входом и выходом .элемента, в каждом из инверторов подложки.п-канальнык транзисторов подключены к общей шине, а подложки р-канальных транзисторов - к плюсовой шине, отличающийся тем, что, с целью раанирения функциональных возможностей, третий инвертор включен между выходом первого инвертора и одной из шин источника питания, не подключенной ко второму инвертору, вход третьего инвертора подключен ко входу второго инвертора. Ис точники информации, принятые во вниман1Г€ при экспертизе: 1.Букреев И.Н. и др. Микроэлектронные схеьлы цифровых устройств.- М., Сов. радио , 1973. 2.Патент Великобритании №1300495, кл. И 3 Т, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1977 |

|

SU627594A1 |

| Логический элемент | 1977 |

|

SU680173A1 |

| Элемент с тремя состояниями | 1982 |

|

SU1051721A1 |

| Согласующее устройство на мдптранзисторах | 1976 |

|

SU708512A1 |

| Элемент памяти для регистра сдвига | 1979 |

|

SU832600A1 |

| Триггер на взаимодополняющих мдп-транзисторах | 1980 |

|

SU875596A1 |

| Логический элемент И | 1981 |

|

SU951707A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Логический элемент на мдп-транзисторах | 1977 |

|

SU664297A1 |

| Многофункциональный логический элемент | 1981 |

|

SU1005313A1 |

Авторы

Даты

1978-10-05—Публикация

1977-05-06—Подача