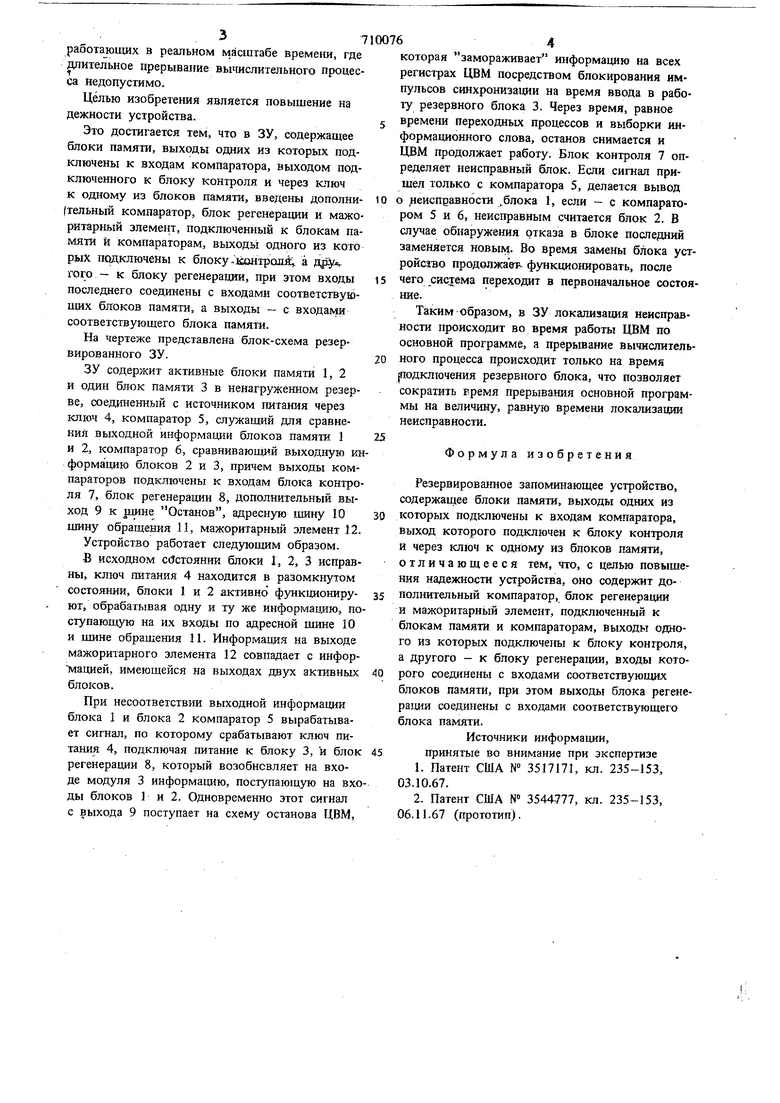

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах, работающих в реальном масштабе времени, с повышенными требованиями к ресурсу. Известно резервированное запоминающее устройство (ЗУ), содержащее однократную избыточность (дублирование), контроль работоспособности которого осуществляется методом сравнения выходной информации, а обнаруженная неисправность локализуется с помощью йоочередной тестовой проверки каждого ЗУ. Время восстановления неисправности в таком устройстве слагается из двух составляющих: вр мени локализации неисправности и времени замещения неисправного модуля исправным. Причем как локализапяя исправности, так и замещение неисправного модуля связаны с прерыванием вычислительного процесса по основной про грамме, что является существенным недостатком данного устройства при использовании в системах, работающих в реальном масщтабе времени 1. Однако такое устройство содсрншт большое количество избыточного оборудован я в нэгру женном резерве. Наибо.пее близким к изобретению является устройство, содержащее по крайней мере не менее дазх ЗУ, выходы с которых подаются па общий компаратор. До тех пор, пока на компаратор поступают и.5ентнчные выходные сигналы от всех ЗУ, система функщюнирует нормально, формируя общий выходной сигнал, подаваемый к центральному процессору. Когда обнаруживается, что выходные сигналы с oiдельшлх ЗУ отличаются друг от друга, то система переключается в режим анализа неисправности. После локализации неисправность итщинируется. Система может продолжить работу, используя другое неповрежденное ЗУ, либо после восстановления отказавшего ЗУ снова перейти в режим работы с двумя ЗУ 2. Таким образом, в прототипе, как и аналоге, локализацию неисправности проводят программными средствами, это приводат к значительным затрата.м непроизводительного времени, что является существенным недостатком для систем. работающих в реальном масштабе времени, где длительное прерывание вычислительного процесса Недопустимо. Целью изобретения является повышение на дежности устройства. Это достигается тем, что в ЗУ, содержащее блоки памяти, выходы одних из которых подключены к входам компаратора, выходом подключенного к блоку контроля и через ключ к одному из блоков памяти, введены дополни(тельный компаратор, блок регенерации и мажоритарный злемент, подключенный к блокам памяти и компараторам, выходы одного из кото рых подключены к блоку ..конхролй;. а nfy того - к блоку регенерации, при этом входы последнего соединены с входами соответствующих блоков памяти, а выходы - с входами соответствующего блока памяти. На чертеже представлена блок-схема резервированного ЗУ. ЗУ содержит активные блоки памяти 1, 2 и один блок памяти 3 в ненагруженном резерве, соединенный с источником питания через ключ 4, компаратор 5, служащий для сравнения выходной информащ1И блоков памяти 1 и 2, компаратор 6, сравнивающий выходную ин формацию блоков 2 и 3, причем выходы компараторов подключены к входам блока контро ля 7, блок регенерации 8, дополнительный выход 9 к ршне Останов, адресную шину 10 шину обращения 11, мажоритарный элемент 12. Устройство работает следующим образом. Б исходном сбстояник блоки 1, 2, 3 исправны, ключ питания 4 находится в разомкнутом состоянии, блоки 1 и 2 активно функщюнируют, обрабатывая одну и ту же информацию, по ступающую на их входы по адресной щине 10 и шине обращения 11. Информация на выходе мажоритарного элемента 12 совпадает с инфорт ацией, имеюще11ся на выходах двух активных блоков. При несоответствии выходной информации блока 1 и блока 2 компаратор 5 вырабатывает сигнал, по которому срабатывают ключ питания 4, подключая питание к блоку 3, и блок регенерации 8, который возобновляет на входе модуля 3 информацию, поступающую на вхо ды блоков 1 и 2. Одновременно этот сигнал с выхода 9 поступает на схему останова ЦВМ, которая замораживает информацию на всех егистрах ЦВМ посредством блок1фования импульсов синхронизации на время ввода в работу резервного блока 3. Через время, равное времени переходных процессов и выборки информационного слова, останов снимается и ЦВМ продолжает работу. Блок контроля 7 определяет неисправный блок. Если сигнал пришел только с компаратора 5, делается вывод неиспвавности .блока 1, если - с компаратором 5 и 6, неисправным считается блок 2. В случае обнаружения отказа в блоке последний заменяется новым. Во время замены блока устройсгас продолжаем функционировать, после чего система переходит в первоначальное состояние. Таким образом, в ЗУ локализация неисправности происходит во время работы ЦВМ по основной программе, а прерывание вычислительного процесса происходит только на время родключения резервного блока, что позволяет сократить время прерывания основной программы на величину, равную времени локализации неисправности. Формула изобретения Резервировшшое запоминающее устройство, содержащее блоки памяти, выходы одних из которых подключены к входам компаратора, выход которого подключен к блоку контроля и через ключ к одному из блоков памяти, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительный компаратор, блок регенерации и мажоритарный элемент, подключенный к блокам памяти и компараторам, выходы одного из которых подключены к блоку контроля, а другого - к блоку регенеращш, входы которого соединены с входами соответствующих блоков памяти, при этом выходы блока регенерации соединены с входами соответствующего блока памяти. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3517171, кл. 235-153, 03.10.67. 2.Патент США № 3544777, кл. 235-153, 06.11.67 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1983 |

|

SU1129657A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1037348A1 |

| Трехканальная резервированная вычислительная система | 1980 |

|

SU949864A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| Резервированная система | 1982 |

|

SU1084802A1 |

Авторы

Даты

1980-01-15—Публикация

1977-03-17—Подача