(5) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ПОКАЗАТЕЛЬНО-СТЕПЕННЫХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1985 |

|

SU1287150A1 |

| Устройство для нахождения экстремума аддитивной функции многих переменных | 1990 |

|

SU1765830A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для логарифмирования | 1981 |

|

SU962926A1 |

| Цифровое логарифмирующее устройство | 1980 |

|

SU918946A1 |

| Устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1363405A1 |

| Устройство для вычисления функций синуса и косинуса | 1974 |

|

SU531161A1 |

| Устройство для извлечения корня @ -й степени | 1987 |

|

SU1474644A1 |

1

Изобретение относится к цифровой вычислительной технике и может быть использовано в специализированных и универсальных ЦВМ, работающих с числами с фиксированной запятой.

Изёестно устройство для вычисления функции А , содержащее блок умножения, п-блоков постоянной памяти и (где m - число входов одного блока постоянной памяти) входов D3.

Недостатком данного устройства являются ограниченные функциональные возможности.

Наиболее близким к предлагаемому является устройство, содержащее основной регистр, сдвига, блок для извлечения квадратного корня, блок умножения, триггер, блок управления. Входы устройства по каждому разряду чисел х и у соединены со входами установки основного регистра и регистра сдвига соответственно. Выход младшего разряда регистра сдвига подсоединен к установочному входу триггера, выход которого соединен с первыми входами блока для извлечения корня и блока управления, выход блока для извлечения корня подключен к дополнительному входу основного регистра и третьему входу блока умно хения, ко второму входу которого подключен его выход, выход блока управления соединен с входами синхронизации блока для извлечения корня и блока умномения и с импульсным входом регистра сдвига, вторые входы блока для извлечения корня и блока умнох ения и выход триггера соединены с входами блока управления, входами устройства являются входы обоих регистров, выходом - выход блрка умножения f2J.

Недостатком данного устройства является низкое быстродействие.

Цель изобретения - увеличение быстродействия.

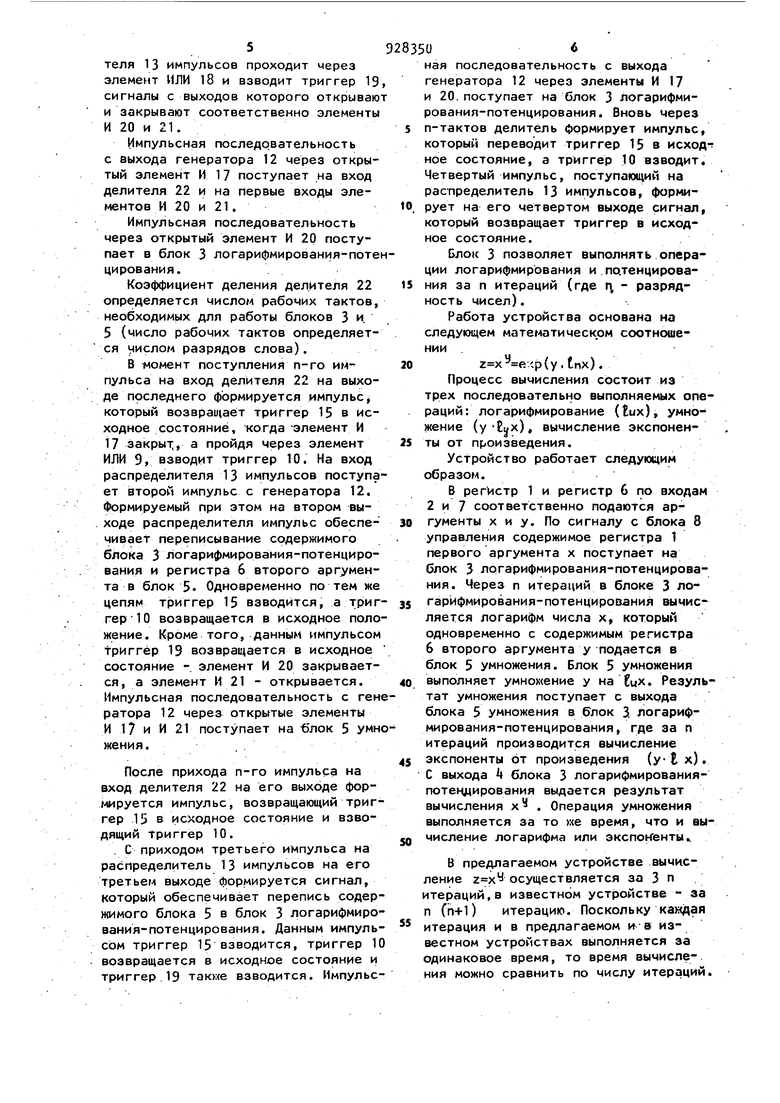

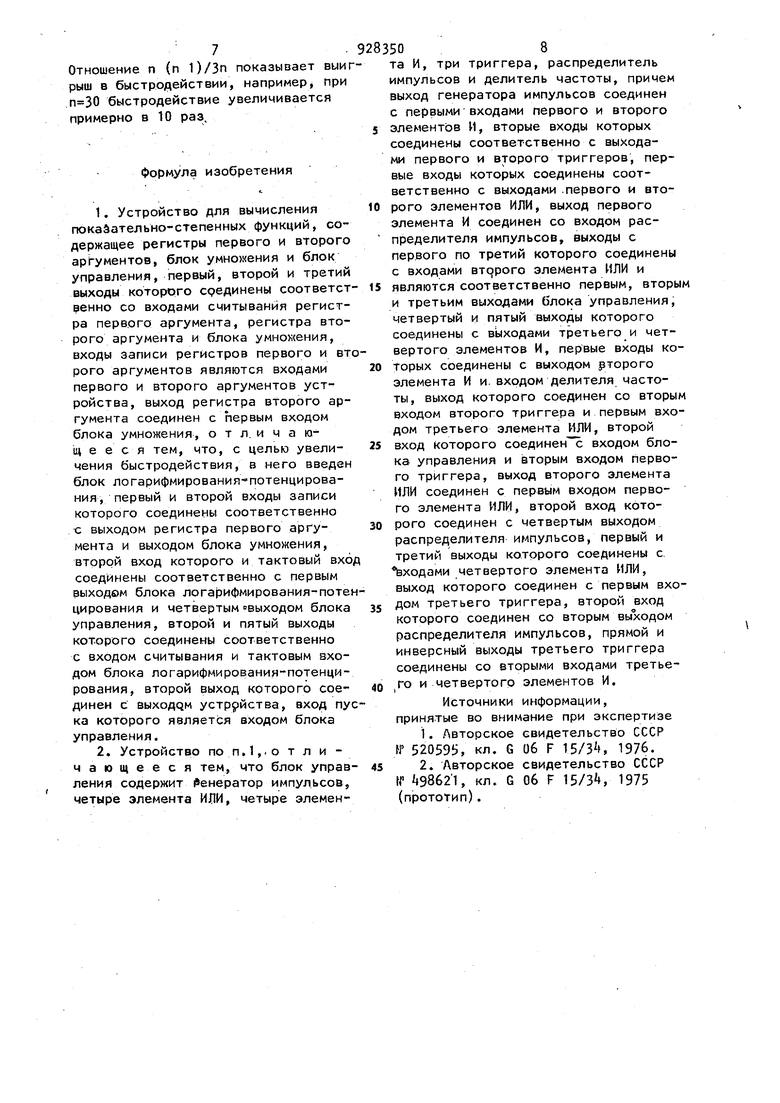

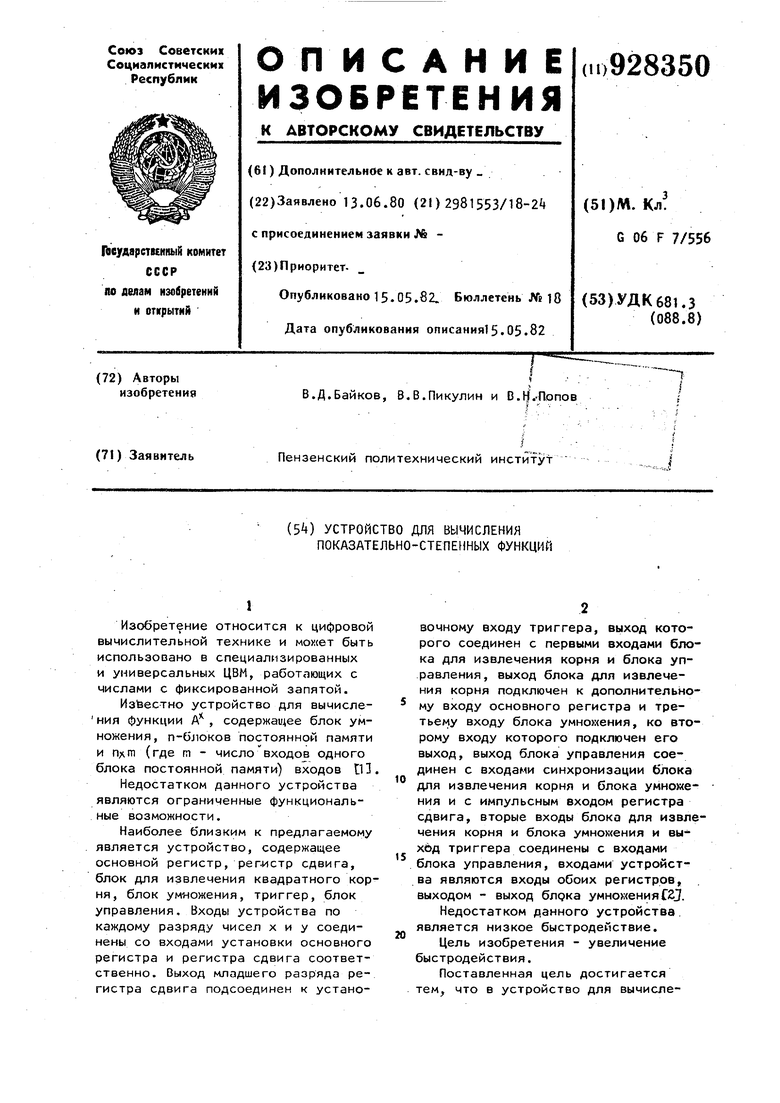

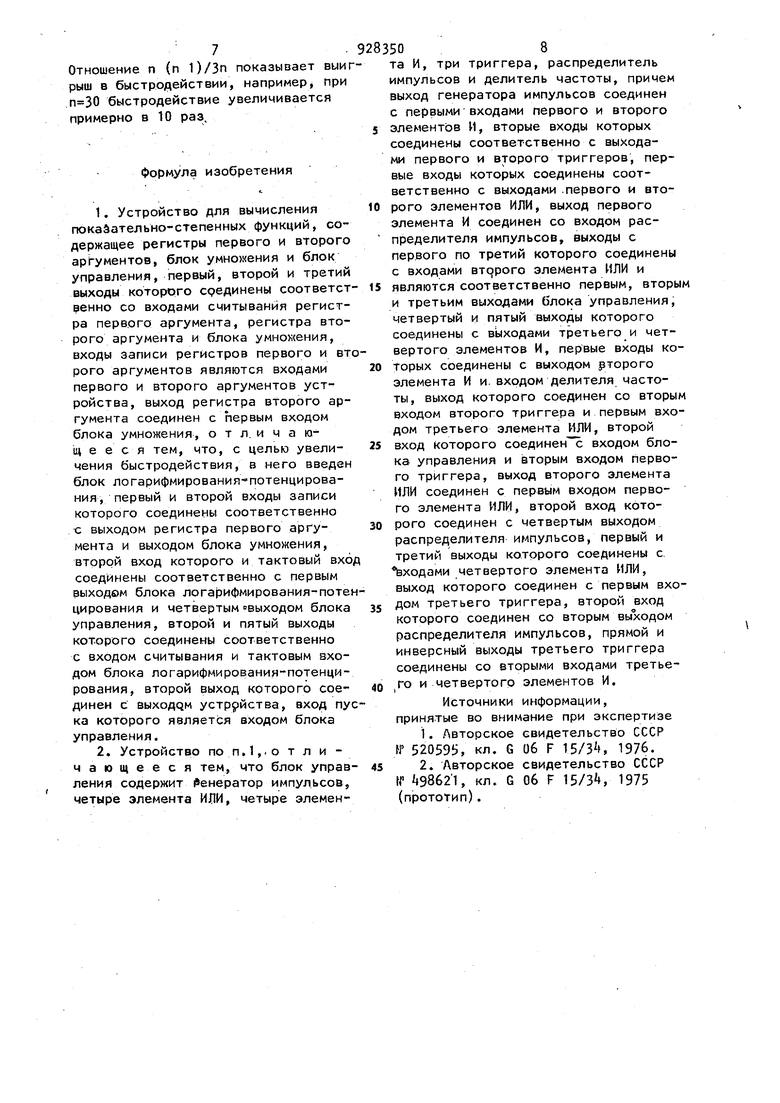

Поставленная цель достигается тем, что в устройство для вычисле35) мил показательно-степенных функций, содержащее, регистры первого и второ го аргументов, блок умно хения и блок управления, первый, второй и третий выходы которого, соединены со ответственно со входами считывания регистра первого аргумента, регистра второго аргумента и блока умножения, входы записи регистров первого и второго аргументов являются входами первого и второго аргументо устройства, выход регистра второго аргумента соединен с первым входом блока умножения, дополнительно введен блок логарифмирования-потенцирования, первый и второй входы за писи которого соединены соответствен но с выходом регистра первого аргумента и выходом блока умножения, вто рой вход которого и тактовый вход соединены соответственно с первым вы ходом блока логарифмирования-потенцирования и четвертым выходом блока управления, второй и пятый выходы которого соединены соответственно с входом считывания и тактовым входом блока логарифмирования-потенциро-i вания, второй выход которого соединен с выходом устройства, вход пуска которого является входом блока управления, причем блок управления содержит (Генератор) импульсов, четыр элемента ИЛИ, четыре элемента И, три триггера, распределитель импуль сов и делитель частоты, причем выход генератора импульсов соединен с первыми входами первого и второго элементов И, вторые входы которых со.еди нены соответственно с выходами первого и второго триггеров, первые входы которого соединены соответстве но с выходами первого и второго элементов ИЛИ, выход первого элемента И соединен со входом распределителя импульсов, выходы с первого по третий которого соединены с входами вто рого элемента ИЛИ и являются соответственно первым, вторым и третьим выходами блока управления, четвертый и пятый выходы которого соедине.ны с выходами третьего и четвертого элементов И, первые входы которых соединены с выходом второго элемента , И и входом делителя частоты, выход которого соединен со вторым вхо.дом второго триггера и первым входом третьего элемента ИЛИ, второй в;(;од которого соединен с входом блока управления и вторым входом первого триггера, выход второго элемента ИЛИ соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с четвертым выходом распределителя импульсов, первый и третий выходы которого соединены с входами четвертого элемента ИЛИ, выход которого соединен с первым входом третьего триггера, второй вход которого соединен со вторым выходом распределителя импульсов, прямой и инверсный выходы третьего триггера соединены со вторыми входами третьего и четвертого элементов И, Иа фиг.1 представлена блок-схема устройства для вычисления показательно-степенных функций i на фиг,2 - схема блока управления. Устройство для вычисления показательно-степенных функций содержит регистр 1 первого аргумента, вход 2 первого аргумента, блок 3 льгарифМирования-потенцирования, выход А устройства, блок 5 умножения, регистр 6 второго аргумента, вход 7 второго аргумента, блок 9 управления. Блок 8 управления содержит элемент 9 ИЛИ, триггер 10, элемент 11 И, генератор 12 импульсов, распределитель 13 импульсов, элемент 1t ИЛИ, триггер 15, .элемент 16 ИЛИ, элемент 17 И, элемент 18 ИЛИ, триггер 19, элементы 20 и 21 И, -делитель 22 частоты. Блок 8 управления работает следующим образом. Сигнал .Пуск через элемент ИЛИ 9 взводит триггер 10, который открывает элемент И 11. Импульс с выхода генератора 12 импульсов через открытый элемент И 11 поступает на вход распределителя 13 импульсов. На первом -выходе распределителя 13 импульсов формируется импульс, который обеспечивает перепись содержимого регистра 1 первого аргумента в блок 3 логарифмирования-потенцирования. Кроме того, данный импульс проходит через элемент ИЛИ 1 и взводит триггер t5. Импульс с выхода элемента ИЛИ Ц поступает на элемент ИЛИ 16, сигнал с выхода которого возвращает триггер 10 в исходное Состояние. При этом элемент И 11 закрыт сигналом с триггера 10, а элемент И 17 открыт триггером 15. Импульс с первого выхода распределителя 13 импульсов проходит через элемент ИЛИ 18 и взводит триггер 19 сигналы с выходов которого открывают и закрывают соответственно элементы И 20 и 21.

Импульсная последрвательность с выхода генератора 12 через открытый элемент И 17 поступает на вход делителя 22 и на первые входы элементов И 20 и 21.

Импульсная последовательность через открытый элемент И 20 поступает в блок 3 логарифмирования-потенцирования.

Коэффициент деления делителя 22 определяется числом рабочих тактов, необходимых для работы блоков 3 и. 5 (число рабочих тактов определяется числом разрядов слова).

В момент поступления п-го импульса на вход делителя 22 на выходе последнего формируется импульс, который возвращает триггер 15 в исходное состояние, когда -элемент И 1 закрыт;, а пройдя через элемент ИЛИ 9, взводит триггер 10. На вход распределителя 13 импульсов поступает второй импульс с генератора 12. Формируемый при этом на втором выходе распределителя импульс обеспечивает переписывание содержимого блока 3 логарифмирования-потенцирования и регистра 6 второго аргумента в блок 5. Одновременно по тем же цепям триггер 15 взводится, а триггер 10 возвращается в исходное положение. Кроме того, данным импульсом tpиггёp 19 возвращается в исходное состояние -. элемент И 20 закрывается, а элемент И 21 - открывается. Импульсная последовательность с генератора 12 через открытые элементы И 17 и И 21 поступает на блок 5 умножения.

После прихода п-го импульса на вход делителя 22 на его выходе фор 4ируется импульс, возвращающий триггер 15 в исходное состояние и взводящий Триггер 10.

С приходом третьего импульса на распределитель 13 импульсов на его третьем выходе формируется сигнал, который обеспечивает перепись содержимого блока 5 в блок 3 логарифмирования-потенцирования. Данным импульсом триггер 15 взводится, триггер 10 возвращается в исходное состояние и триггер 19 взводится. Импульсная последовательность с выхода генератора 12 через элементы И 17 и 20.поступает на блок 3 логарифмирования-потенцирования. Вновь через 5 п-тактов делитель формирует импульс, который переводит триггер 15 в исход-; ное состояние, а триггер 10 взводит. Четвертый импульс, поступающий на распределитель 13 импульсов, формирует на его четвертом выходе сигнал, который возвращает триггер в исходное состояние.

Блок 3 позволяет выполнять операции логарифмирования и патенцирова15 ния за п итераций (где t - разрядность чисел).

Работа устройства основана на следующем математическом соотношении .

0 (у .tnx).

Процесс вычисления состоит из трех последовательно выполняемых опе. раций: логарифмирование (tux), умножение (у ) , вычисление экспоненты от произведения.

Устройство работает следующим образом.

В регистр 1 и регистр 6 по входам 2 и 7 соответственно подаются аргументы X и у. По сигналу с блока 8 управления содержимое регистра 1 первого аргумента х поступает на блок 3 логарифмирования-потенцирования. Через п итераций в блоке 3 ло5 гарйфмирования-потенцирования вычисляется логарифм числа х, который одновременно с содержимым регистра 6 второго аргумента у подается в блок 5 умножения. Блок 5 умножения

0 выполняет умнох ение у на tux. Результат умножения поступает с выхода блока 5 умножения в блок 3 логарифмирования-потенцирования, где за п итераций производится вычисление

5 экспоненты от произведения (у-t х). С выхода 4 блока 3 логарифмированияпотенцирования выдается результат вычисления х . Операция умножения выполняется за то время, что и выQ числение логарифма или экспоКенты

В предлагаемом устройстве вычисление осуществляется за 3 п итераций,в известном устройстве - за п Сп+1) итерацию. Поскольку какадая итерация и в предлагаемом и в известном устройствах выполняется за одинаковое время, то время вычисления можно сравнить по числу итераций. Отношение n (n 1)/3n показывает вии рыш в быстродействии, например, при быстродействие увеличивается примерно в 10 раз. формула изобретения 1. Устройство для вычисления показательно-степенных функций, содержащее регистры первого и второго аргументов, блок умножения и блок управления, первый, второй и третий выходы которого срединены соответст венно со входами считывания регистра первого аргумента, регистра второго аргумента и блока умножения, входы записи регистров первого и вт рого аргументов являются входами первого и второго аргументов устройства, выход регистра второго аргумента соединен с первым входом блока умножения, о т л. и ч а ю14 е е с я тем, что, с целью увеличения быстродействия, в него введен блок логарифмирования потенцирования, первый и второй входы записи которого соединены соответственно с выходом регистра первого аргумента и выходом блока умножения, второй вход которого и тактовый вхо соединены соответственно с первым выходом блока лога|эифмирования-поте цирования и четвертым выходом блока управления, второй и пятый выходы которого соединены соответственно с входом считывания и тактовым входом блока логарифмирования-потенцирования, второй выход которого соединен с выходдм устррйства, вход пус ка которого является входом блока управления. 2. Устройство поп.1,-0 т л и чающееся тем, что блок управления содержит Ренератор импульсов, четыре элемента ИЛИ, четыре элемен508та И, три триггера, распределитель импульсов и делитель частоты, причем выход генератора импульсов соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с выходами первого и второго триггеров, первые входы которых соединены соответственно с выходами .первого и второго элементов ИЛИ, выход первого элемента И соединен со входом распределителя импульсов, выходы с первого по третий которого соединены с входами BTqporo элемента ИЛИ и являются соответственно первым, вторым и третьим выходами блока управления, четвертый и пятый выходы которого соединены с выходами третьего и четвертого элементов И, первые входы коТорых соединены с выходом рторого элемента И и. входом делителя частоты, выход которого соединен со вторым входом второго триггера и первым входом третьего элемента ИЛИ, второй вход Которого соединен входом блока управления и вторым входом первого триггера, выход второго элемента ИЛИ соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с четвертым выходом распределителя импульсов, первый и третий выходы которого соединены с. ходами четвертого элемента ИЛИ, выход которого соединен с первым входом третьего триггера, второй вход которого соединен со вторым выходом распределителя импульсов, прямой и инверсный выходы третьего триггера соединены со вторыми входами третье, и четвертого элементов И. Источники информации, принятые во внимание при экспертизе i. Авторское свидетельство СССР W 52059fi, кл. 6 Об F , 1976. 2. Авторское свидетельство СССР № Ц98621, кл. G Об F ТЗ/З, 1975 (протогип).

М

/

I

roi

«3

I

a

IE:

9:

Авторы

Даты

1982-05-15—Публикация

1980-06-13—Подача