:54) УСТРОЙСТВО ДЛЯ ПОТЕНЦИРОВАНИЯ ЛОГАРИФМОВ

(ментов И первой группы подключены к выходу элемента задержки, вход которого соединен с выходом первого элемента И, один из входов которого подключен к входной шине, причем, нулевой вход триггера соединен с шиной установки, к которой подключен вход сброса счетчика 2. Недостаток известного устройства заключается в том, что вычисляемые значения результатов потенцирования для двадцатиразрядных двоичных кодов логарифмов чисел в ряде случаев от своих истинных значений отличаются с третьего разряда.

Целью изобретения является повы1 ение точности устройства для потенцирования логарифмов.

Достигается это тем, что в устройство для потенцирования, содержащее счетчик, регистр сдвига и триггер, первые входы которых соединены с установочным входом устройства, выход триггера соединен с первыми входами элементов И первой группы и через первый элемент задержки - с первыми входами элементов И второй группы и первым входом первого элемента И, через .который тактирующий вход устройства соединен с входом блока регистров сдвига, выходы которого соединены с вторыми входами соответствующих элементов И второй группы, третьи входы которых и вторые входы элементов И первой группы соединены с соответствующими выходами детиифратора, входы которого соединеныС выходами регистра сдвига, выходы элементов И, второй группы через первый элемент ИЛИ соединены с входом сумматора, выходы элементов И первой группы через соответствующие узлы задания коэффициентов соединены с входами второго элемента ИЛИ,, выход которого соеди,нен с соответствующим входом сумматора, первый распределитель, вход которого соединен с управляющим входом устройства, второй элемент И, два элемента ИЛИ, элемент ЙЕ, введены два распределителя, три элемента ИЛИ элемент ИЛИ-НЕ, четыре элемента И, Два элемента задержки, причем, выход первого распределителя соединен с входом второго распределителя, выход которого через третий элемент ИЛИ соединен с входами второго и третьегЬ элементов И, выход третьего элемента И соединен с вторьм входом счейчика и через второй элемент задержки с входом третьего элемента ИЛИ, выходы счетчика через последовательно соединенные элемент ИЛИ-НЕ, второй элемент И и элемент НЕ соединны с входом третьего элемента И, выход второго элемента И через последовательно соединенные третий распределитель и четвертый элемент ИЛИ соединен с взводом четвертого элемента И, через Который выход сумматора coe

динен с выходом устройства, периам группа выходов первого распределителя через пятый элемент ИЛИ соедине- на с входом пятого элемента И, вторая группа выходов первого распределителя через шестой элемент ИЛИ соединена с входом пятого элемента ИЛИ и вторым входом регистра сдвига, група выходов второго распределителя через седьмой элемент ИЛИ соединена с -третьим входсм счетчика и через шестой элемент И - с четвертым входом счетчика, один из выходов группы второго распределителя соединен с вторым входом триггера, информационный вход устройства соединен с входом шестого элемента И и через пятый элемент И с третьим входом регистра сдвига и входом третьего элемента задержки, выход которого соединен с третьими входами элементов И первой группы.

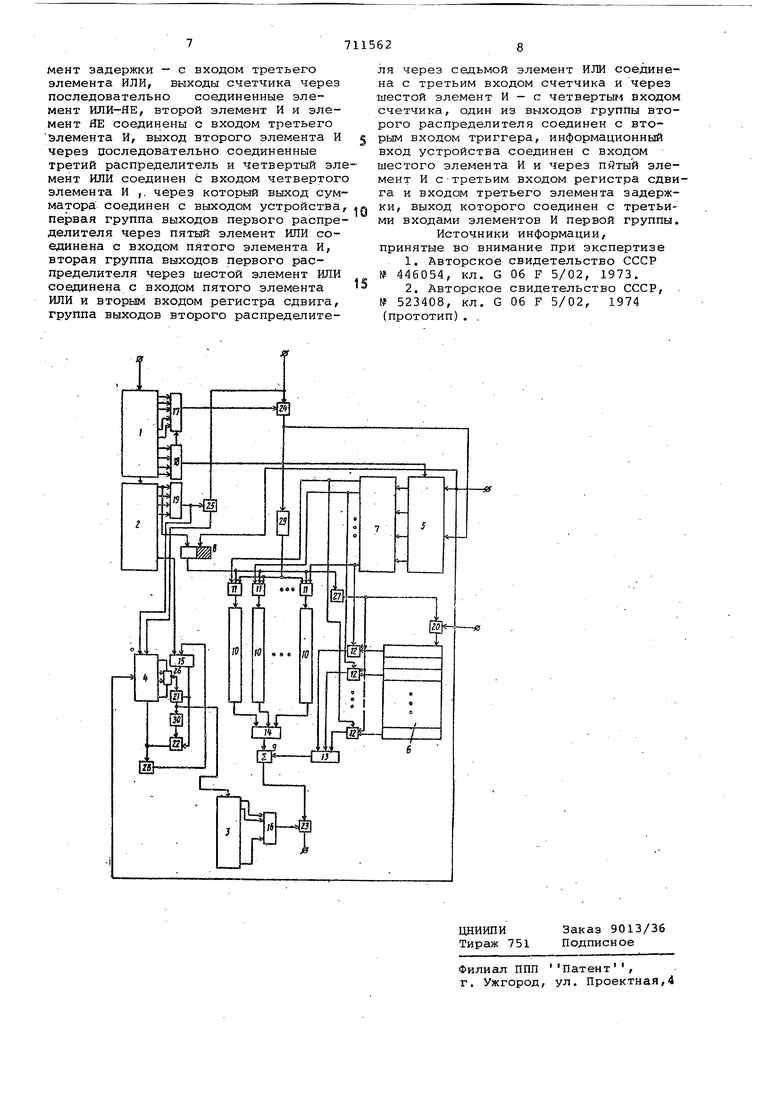

На чертеже приведена блок-схема устройства.

Устройство содержит распределители 1, 2,. 3, счетчик 4, регистр 5 сдвига, блок б регистров сдвига, дешифратор 7, триггер 8, сумматор 9, группу узлов 10 задания коэффициентов, группу элементов И 11, группу элементов И 12, элементы ИЛИ 13-19, элементы И 20-25, элемент ИЛИ-НЕ 26, элементы 27-29, элемент НЕ 30.

Функционирование устройства для потенцирования логарифмов двоичных чисел осуществляется следующим образом. В исходном состоянии счетчик 4, триггер 8 и регистр 5 установлены в нулевое состояние. На первом такте по управляющему входу на распределитель 1 подается единица. Одновременно, начиная с первого такта, на информационный вход подается сначала мантисса логарифма младшими разрядами вперед, а затем характеристика также младшими разрядами вперед. С первого по шестнадцатый такты с выхода элемента ИЛИ 17 выдается единица, которая подается на элемент И 24. В результате этого в элементе 29 запишется мантисса логарифма. Логические уровни последних четырех разрядов мантиссы логарифма заносятся в регистр 5 сдвига, так как на него с элемента ИЛИ 18 с тринадцатого по шестнадцатый такты подается единица. Вследствие этого на одном из выходов дешифратора 7 образуется единица, которая поступает на один из элементов И 11 и на один из элементов И 12 На семнадцатом такте по сигналу с соответствующего выхода распределителя 2 триггер 8 переводится в единичное состояние, и тем самым, разблокирует элементы И 11. В результате двоичный код мантиссы логарифма из элемента 29 через выбранный элемент И 11 постпает на вход соответствующего узла 10. Единица с выхода триггера 8 через элемент 27, время задержки которого равняется времени работы узлов 10, открывает элемент И 20, разрешая тем самым проход тактовых импульсов в блок 6. Через выбранные элементы И 12 и элемент ИЛИ 13 информация с соответствующего регистра блока 6 подается на один из входов сумматора 9, на другой вход которого через элемент ИЛИ 14 подается информация с выхода выбранного узла 10. На выходе сумматора 9 образуется мантисса двоичного числа по следующей системе уравнений:

х у + о ,01001010.110у + 0,101101010011 ,01000010101у + 0,101111001101 Хд у + 0,00111010010у + 0,110001000010 ,0011000ИООу + 0,110010110100 Х5 у + 0,00101000011у + 0,110100100001 Xj, y + 0,00011110111y + 0,110110001010 ,00010100111у + 0,110111101110 xg ;y+0 00001010011y + 0,111001001100

«9 - у + 0,111010011111 ,, 1,00001011111у + 0,111000110101 х 1,00010111101у + 0,110110111111 1,00100100001у + 0,110100110101 1,00110001000у + 0,110010011011 . 1,00111110100у + 0,101111101011 1,01001100101у + 0,10110,0100101 1,01011011010у + 0,101001001010

Первые два члена уравнений к, -Xg и первые члены уравнений формируются в узлах 10, а третьи члены уравнений и вторые члены уравнений Хд-х записаны в регистрах блока 6. При этом каждому узлу 10 соответствует один из регистров блока 6. С семнадцатого по двадцатый такты на выходе элемента ИЛИ 19 формируется единица, которая через элемент И 25 разрешает запись характеристики логарифма в счетчик 4. На двадцать вось мом такте с выхода распределителя 2 единица подается на вход элемента ИЛИ 15. Если хотя бы в одном разряде счетчика 4 записана единица, то на выходе элемента И 21 вырабатывается нулевой уровень, который через элемент НЕ 30 подается на вход элемента И 22. Единица с выхода элемента И 22 подается на вход счетчика 4 и происходит уменьшение содержимого счетчика 4 на единицу. Единица с выхода элемента И 22 через элемент 28 на последующем такте подается на вход элемента ИЛИ 15. Описанный цикл повторяется до тех пор, пока не произойдет обнуление содержимого счетчика 4. В этом случае на выходе элемента И 21 вырабатывается единичный уровень, который запускает распределитель 3, и вырабатывается единичный уровень на выходе элемента ИЛИ 16, который .разблокирует элемент И 23 и на выходе устройства начинается формирование двоичного кода искомого числа.

В изобретении достигается повышение точности вычисления по сравнении

с прототипом на четыре порядка, так как в известном устройстве вычисляемые значения результатов потенцирования для шестнадцатиразрядных двоичных кодов мантисс логарифмов в ряде случаев от своих истинных значений отличаются с третьего разряда, а в заявленном - с четырнадцатого.

По предлагаемому изобсетению оазработан технический проект, утвержденый Минприбором СССР. Согласно плану Минприбора СССР предложенное устройство для потенцирования логарифмов впервые будет внедрено на предприятии НПО Элва в 1978-1979 гг. в составе микро-ЭВМ и перестраиваемой управляющей логической машины. Экономический эффект, который может быть получен народным хозяйством в результате использования предполагаемого изобретения при серийном производстве указанных ЭВМ в год в количестве 100 штук каждая составит около 65 тыс. руб. в год.

Формула изобретения

Устройство для потенцирования лагрифмов содержащее счетчик, регистр сдвига и триггер,первые входы которы соединены с установочным входом устройства,выход триггера соединен с певыми входами элементов И первой группы и через первый элемент задержки с первыми входами элементов И второй группы и первБгм входом первого эле:мента И, через который тактирующий вход устройства соединен с входом блока регистров сдвига, выходы которого соединены с вторыми входами соответствующих элементов И второй, группы, третьи входы которых и вторые входы элементов И первой группы соединены с соответствующими выходами дешифратора, входы которого соединены с .выходами регистра сдвига, выходы элементов И второй группы через первый элемент ИЛИ соединены с входом сумматора, выходы элементов И первой группы через соответствующие узлы задания коэффициентов соединены с входами второго элемента ИЛИ, выход которого соединен с соответствующим входом сумматора, первый распределитель, вход которого соединен с управляющим входом устройства, второй элемент И, два элемента ИЛИ, элемент НЕ, о т личающеес я тем, что, с целью повышения точности, в него введены два распределителя, три элемента ИЛИ, элемент ИЛИ-НЕ, четыре элемента И, два элемента задержки, причем, выход первого распределителя соединен с входом второго распределителя, выход которого через третий элемент ИЛИ соединен с вхо.п.ами второго и третьего элементов И, выход третьего элемента И соединен с вторым входом счетчика и через второй эле- ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования и потенцирования | 1978 |

|

SU711561A1 |

| Устройство для логарифмирования | 1978 |

|

SU711560A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Устройство для преобразования двоичных чисел | 1973 |

|

SU446054A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ КОДОВ | 1972 |

|

SU330448A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для потенцирования | 1976 |

|

SU633017A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1179328A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

Авторы

Даты

1980-01-25—Публикация

1978-08-08—Подача