(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

| Устройство для контроля адресных цепей боков памяти | 1985 |

|

SU1274007A1 |

| Устройство для контроля блоков памяти | 1979 |

|

SU790019A1 |

| Устройство для контроля адресных цепей блоков памяти | 1984 |

|

SU1200347A1 |

| Устройство ввода-вывода информации | 1983 |

|

SU1226429A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920848A1 |

| Устройство для контроля постоянной памяти | 1978 |

|

SU748514A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

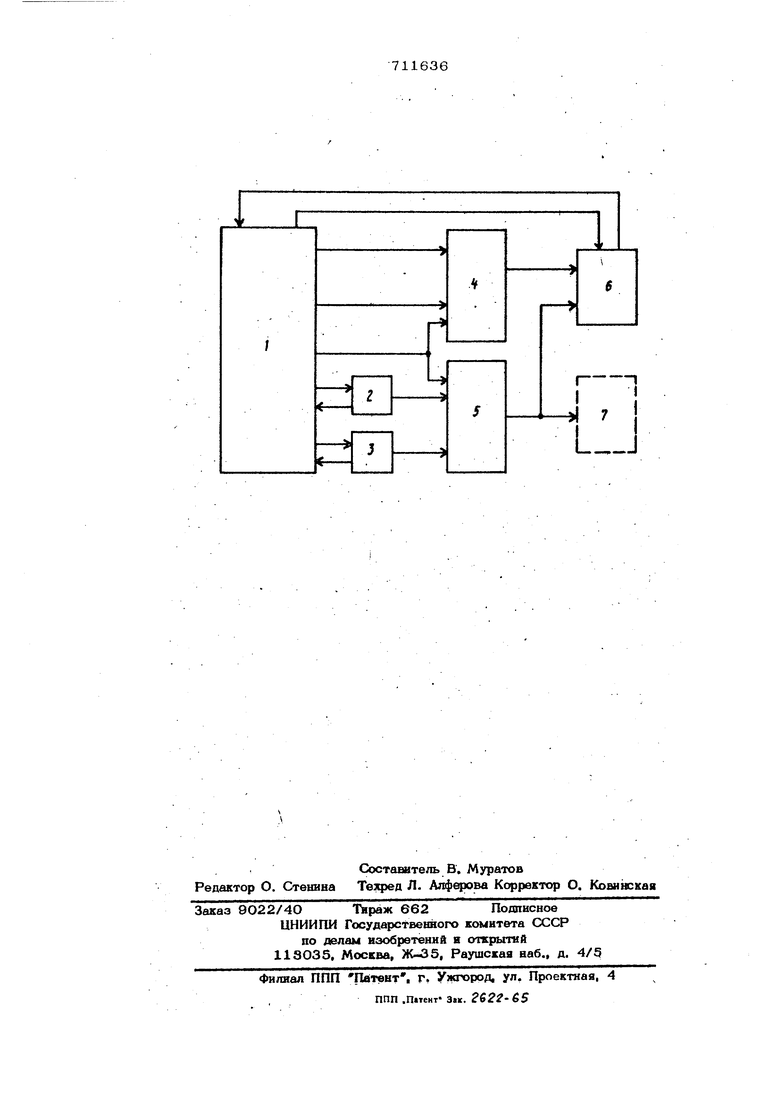

.- . Изобретение относится к области вы .числительной техники и может использоваться для контроля запоминающих устройств (ЗУ). Известно устройство для контроля запоминающих устройств, содержащее адресные блоки, блоки анализа, сравнения и регистрации, позволяющее форми ровать разные тестовые последователь- носта l . Н(вдостатком его является невозможность формирования режимов, обеспечи веющих диагностику сбоев и отказов. Наиболее близким техническим реше- вием к предлагаемому изобретению явл ется устройство для контроля блоков памяти, которое содержит счетчик, подключенный к блоку формирования адресов, .коммутатор, счетчик циклов, , ключенный к узлу сравнения циклов и узлу сравнения адресов, счетчик адресных операций и блок сравнения количес ва циклов 2.Принятая структура бло кй Ядресации позволяет реализовать динамические тесты,бегающая 1 или О, шахматный порядок и переменное циклирование. Недостатком известного устройства является то, что оно не может формировать режим циклического обращения к тестируемому блоку памяти по выбранной паре адресов., Целью изобретения является расишрение функциональнь1х возможностей путем формирования режима циклического обращения по паре адресов. Это достигается тем, что в устройстве для контроля блоков памяти, содержащее блок управления, соединенный со счетчиками и коммутатором адресных кодов, выход которого является выхо4ЬМ устройства, введены коммутатор адресов цикла, входы которого под1(лючеш 1 к выходам блока управления, и блок сравнения, первый вход которого подключен к выходу коммутатора адресных кодов, второй вход подключен к выходу коммута3тора адресов цикла, третий вход подклю нен к выходу блока управлегшя, вход ко рого подключен к выходу блока сравнения. , На чертеже представлена структурнй электрическая схема устройства для ; сонтроля блоков памяти. J.:/-; Устройство для контроля блоков памяти содержит блок управления 1, счетчик 2 (текущего адреса проверки А1 счетчик 3 (адреса хранения тестового, слова А2), коммутатор адресов цикла 4, коммутатор адресных кодов 5, блок сравнения 6, контролируемое запоминак)щее устройство 7. Устройство работает следующим образом. Для задания перечисленных тестоы 1Х программ обращения к запоминающему устройству 7 по адресам А1 и А2 должны чередоваться. Блок управления 1 в соответствии с алгоритмом выбранного теста выдает на коммутатор адрес ных кодов 5 сигнал, разрещающий поочередное прохождение к контролируемому запоминающему устройству 7 и блоку сравнения 6 адресного кода А1 или А2 счетчика 2 или 3, а также изменяе состояние счетчиков 2 и 3. По тому же сигналу с блока управления 1 через коммутатор адресов цикла 4 на блок сравнения 6 поочередно проходят два адреса, набранные на клавишах блока управления 1. Таким образом, на блок сравнения 6с коммутаторов 4 и 5 . переменно проходят или адрес А2 хранения тестового слова и первый адрес А1, набранный на клавищах блока управ ления 1, или текущий адрес А1 и второ адрес А2, набранный на клавишах блока управления 1. Когда адрес А2 становится первому адресу А1, на ранному на клавишах блока управления блок сравнения 6, по сигналу с блока управления 1, формирует сигнал равенс ва этих адресов и запоминает его до тех пор, пока не станут равным а/фес 1. И второй адрес .А2, набранный на клавишахблока управления 1. В момент, когда становятся равными обе пары вцрвсов, блок сравнения 6 формирует сигнал, по когорому блок управления 1 прекращает изменение состояния счет чйков 2 и 3. Обращение к запоминающему устройству 7 идет теперь по неизменным адаесам AJ. и А2, равным адреса), набранным на клавишах блока управления OcHOBHbOvf преимуществом изобретения является возможность формирования режима циклического обращения по паре адресов и контроля адресного перехода. Формула изобретения Устройство для контроля блоков памяти, содержащее блок управления, соединенный со счетчиками и коммутатором адресных кодов, выход которого является выходом устройства, отличающееся тем, что, с целью расщирения функциональных возможностей за счет формирования режима циклического обращения по даре адресов, в него введены коммутатор адресов цикла, входы которого подключены к выходам блок управления, и блок сравнения, первый вход которого подключен к выходу коммутатора адресных кодов, второй вход подключен к выходу коммутатора адресов цикла, третий вход подключен к выходу блока управления, вход которого подключен к выходу блока сравнения. Источники информации, принятые во внимание при экспертизе 1.Авторское, свидетельство СССР № 5О425О, кл. G 11 С 29/ОО, 25.02.76. 2..Авторское свидетельство СССР N9 526954, кл. Q 11 С 29/00, 30.08.76 (лрототип).

Авторы

Даты

1980-01-25—Публикация

1978-09-25—Подача