(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля адресных цепей боков памяти | 1985 |

|

SU1274007A1 |

| Устройство для контроля адресных цепей блоков памяти | 1984 |

|

SU1200347A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для формирования тестовой последовательности | 1986 |

|

SU1529293A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1683015A1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1261014A1 |

| Устройство для формирования теста блока оперативной памяти | 1990 |

|

SU1714609A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Устройство для приема и воспроизведения телеизмерений | 1986 |

|

SU1377888A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в аппаратуре контроля блоков памяти для формирования контролирующих тестов.

Известно устройство для контроля блоков памяти, содержащее .счетчик адреса и блок формирования чисел и формирующее тестовые программы для функционального контроля блоков памяти tl.

Недостаткомэтого устройства является низкое быстродействие.

Из известных устройств наиболее близким техническим решением к предлагаемому является устройство для контроля блоков памяти, содержащее блок формирования теста, блок управления, блок контроля считанной информации, блок сравнения, первый, второй и третий счетчики и выполняет провер.КУ блоков памяти тестовой программой падающий, дождь Г2Д.

Недостатком этого устройства является невысокое быстродействие, так как длительность тестовой программы пропорциональна третьей степени числа битов емкости блока памяти.

Цель изобретения - повышение быстродействия устройства за счет того.

что тестовая программа контроля состоит из 2п циклов записи по всем К адресам (с последующим считыванием и контролем) в каждый j-ый разряд блока памяти (где j 1, 2, ...,mномер разряда блока памяти) всех i-x разрядов кода адреса (где ,2, ..., п - номер разряда кода адреса), .длительность контроля этой теБтовой ,

10 программы пропорциональна N (где m разрядность блока памяти, п разрядность кода адреса, а m .J 2п) .

Поставленная цель достигается тем, что в устройство для контроля блоков

15 памяти, содержащее счетчик адреса, схему сравнения и блок управления, причем управляющие вход и выход счетчика адреса подключены к выходу и одному из входов блока управления, дру20гие входы которого соединены с выходам схемьл сравнения, выходы счетчика адреса и одни из входов схемы сравнения являются соответственно адресными выходами и входами устройства,

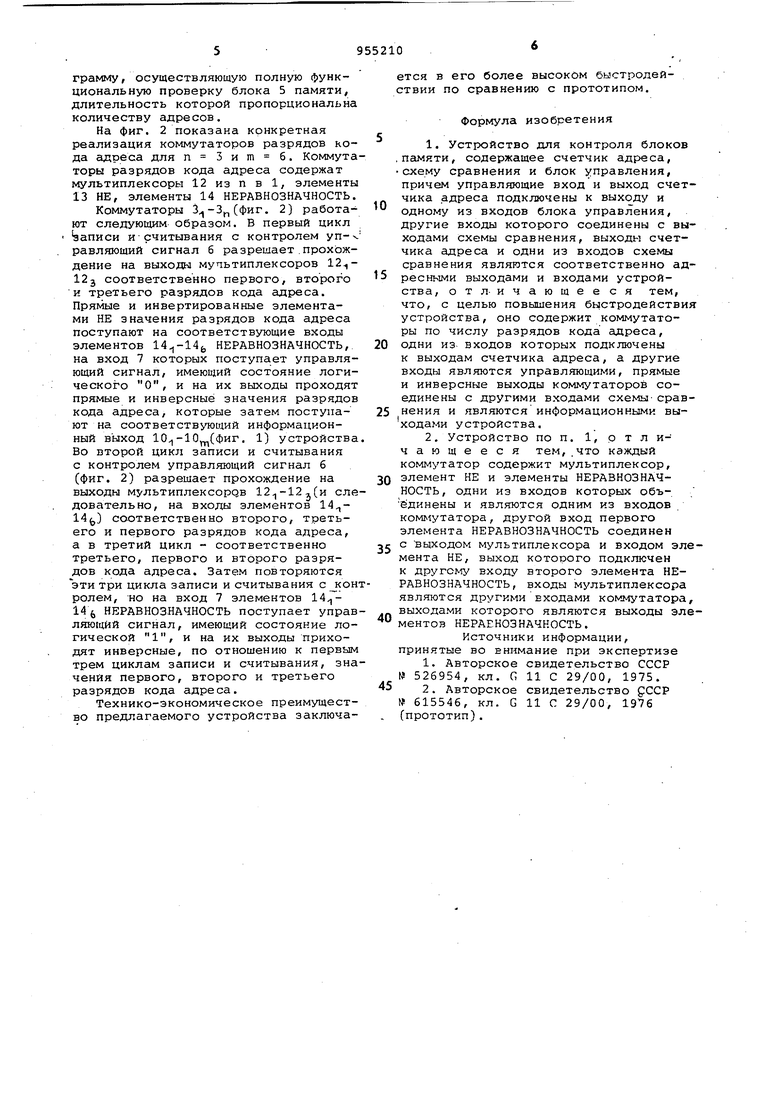

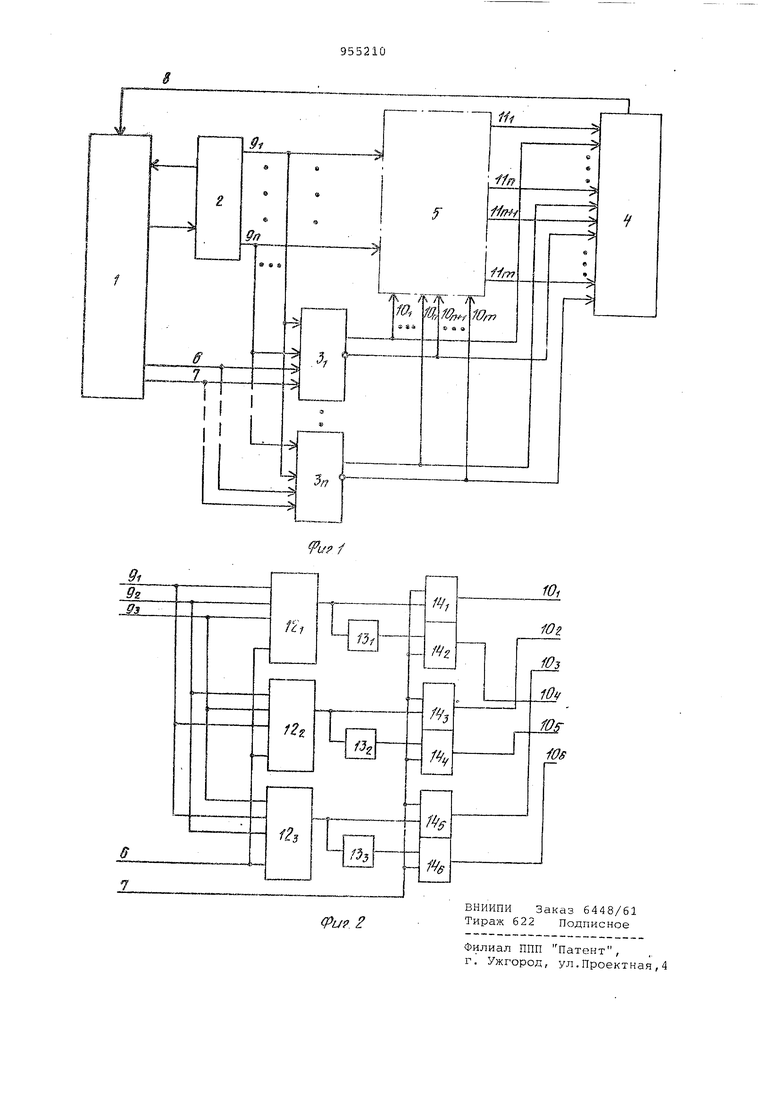

25 введены коммутаторы по числу разрядов кода адреса, одни из входов которых подключены к выходам счетчика , а другие входы являются управляющими, прямые и инверсные выходы коммутато30ров соединены с другими входами схеNKJ сравнения и являются информационньоми выходами устройства. Каждый коммутатор содержит мульти плексор, элемент НЕ и элемент НЕРАВ НОЗНАЧНОСТЬ, одни из входов которых объединены и являются одним из входо коммутатора, другой вход первого эле UeHTa НЕРЛВНОЗНАЧНрСТЬ соединен с вы ходом мультиплексора и входом элемен та НЕ, выход которого подключен к др гому входу второго элемента НЕРАВНОЗНАЧНОСТЬ, входы мультиплексора являются другими входами коммутатора, выходами которого являются выходы элементов НЕРАВНОЗНАЧНОСТЬ. На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема коммутатора для примера трехразрядного кола адреса, наиболее предпочтительный вариант вьшолнения. Предлагаемое устройство содержит (фиг. 1) блок 1 управления, счетчик 2 адреса, коммутаторы , предназ наченные для коммутации разрядов кода адреса, и схему 4 сравнения. На фиг. 1 показан также контролируемый блок 5 памяти, а также обозначены управляющие входы 6 и 7 коммутаторов выход 8 схемы сравнения, выходы счетчика адреса, информационные выходы и входы устройства, подключенные соответственно к входным и выходным разрядным шинам блока памяти. Каждый коммутатор содержит (фиг. 2) мультиплексор 12, элементы НЕ 13 и элементы НЕРАВНОЗНАЧНОСТЬ 14. Устройство работает следующим об разам. Блок 1 (фиг. 1) управления задает счетчику адреса режим последовательного обращения ко всем адресам контролируемого блока 5 памяти, адресные входы которого подключены к выходам 9 счетчика 2. Кроме того, с выходов 9 счетчика 2 п-разрядный код адреса поступает .на входы каждого из коммутаторов . Разрешение на прохождение разряда кода адреса поступает на управляющий вход б соответствующего из коммутаторов 3-1-3, с выхода блока 1управления. В первый цикл записи по всем адресам первого разряда блока 5 памяти производится запись первого разряда кода адреса, по всем адресам второго разряда второго разряда кода адреса и т.д. по всем адресам п-го разряда кода адреса, а по всем адресам (п + 1)-го производится запись инверсного первого кода адреса, по всем адресам (п + 2)-го разряда - инверсного второго разряда кода адреса и т.д., по всем адресам т-го разряда (где m 2п) инверсного п-го раз ряда кода адреса. Затем следует цикл считывания по всему объему блока памяти. Информация с выходных разрядных шин контролируемого блока 5 памяти поступает на входы 11 схемы 4 сравнения, на вторые входы которой поступает для сравнения информация (эталон) с выходов соответствующих коммутаторов (фиг. 1. При несовпадении считанной и эталонной информации сигналы с выхода 8 схемы 4 сравнения поступают в блок 1 управления, где фиксируется отказ или сбой. При совпадении блок 1 управления осуществляет следующий цикл записи. Такая запись и считывание со сравнением, выявляет взадмное влияние между .разрядами контролируемого блока 5 памяти, так как информация на выходе любого разряда будет инверсной по отношению к информации на выходах всех остальных разрядов. В последующих циклах записии считывания со сравнением блок 1 (фиг. 1) выдает на управляющий вход 6 соответствующего коммутатора 3 -3 разрешение на прохождение на выход этого коммутатора i-ro разряда кода адреса, где i 1, 2, ..... пи увеличивается на единицу в каждом новом цикле . То есть на выход первого коммутатора Зх, проходят во второй цикл записи и считывания с контролем прямой и инверсный второй разряд кода адреса, в третий цикл - прямой и инверсный третий разряд кода адреса, в п-ый цикл - прямой и инверсный п-ый разряд кода адреса; на выход второго коммутатора 3 «2 во второй, третий, ..., п-ый циклы записи и считывания проходят соответственно прямой и инверсный третий, четвертый, . . . , п-ый Ипервый разряды кода адреса и т.д. Затем повторяются все п циклов записи и считывания со сравнением для тех же разрядов кода адреса, но при инверсном значении управляющего сигнала на входах 7. В этом случае с прямых выходов коммутаторов на выходные разрядные шины блока 5 памяти поступают инверсные, а с инверсных выходов - прямые, по сравнению с первыми п циклами записи, значения разрядов кода адреса. Следовательно, за 2п циклов записи в запоминающие элементы каждого разряда блока 5 памяти записываются прямая и инверсная последовательность кодов, соответствующая изменению всех разрядов кода адреса. Такая тестовая программа выявляет взаимное влияние запоминающих элементов блока 5 внутри каждого разряда, поскольку каждый зaпo инaющий элемент, хотя бы один раз за такую проверку, запоминает информацию, инверсную по отношению к информации,запоминаемой во всех остальных запоминающих элементах разряда. образом,предлагаемое устройство контроля формирует тестовую программу, осуществляющую полную функциональную проверку блока 5 памяти, длительность которой пропорциональна количеству адресов. На фиг. 2 показана конкретная реализация коммутаторов разрядов кода адреса для п 3 и m б. Коммута торы разрядов кода адреса содержат мультиплексорь: 12 из п в 1, элементы 13 НЕ, элементы 14 НЕРАВНОЗНАЧНОСТЬ. Коммутаторы (фиг. 2) работают следующим образом. В первый цикл записи и-считывания с контролем уп--равляющий сигнал 6 разрешает.прохождение на выходы мультиплексоров соответственно первого, второго и третьего разрядов кода адреса. Прямые и инвертированные элементами НЕ значения разрядов кода адреса поступают на соответствующие входы элементов , НЕРАВНОЗНАЧНОСТЬ, на вход 7 которых поступает управляющий сигнал, имеющий состояние логического О, и на их выходы проходят прямые и инверсные значения разрядов кода адреса, которые затем поступают на соответствующий информационный выход (фиг. 1) устройства Во второй цикл записи и считывания с контролем управляющий сигнал 6 (фиг. 2) разрешает прохождение на выходы мультиплексордв ,(и сле довательно, на входы элементов соответственно второго, третьего и первого разрядов кода адреса, а в третий цикл - соответственно третьего, первого и второго разрядов кода адреса. Затем повторяются эти три цикла записи и считывания ролем, но на вход 7 элементов (, НЕРАВНОЗНАЧНОСТЬ поступает управ ляющий сигнал, имеющий состояние логической 1, и на их выходы приходят инверсные, по отношению к первым трем циклам записи и считывания, зна чения первого, второго и третьего разрядов кода адреса. Технико-экономическое преимущество предлагаемого устройства заключается в его более высоком быстродейтвии по сравнению с прототипом. Формула изобретения 1.Устройство для контроля блоков памяти, содержащее счетчик адреса, схему сравнения и блок управления, причем управляющие вход и выход счетчика адреса подключены к выходу и одному из входов блока управления, другие входы которого соединены с выходами схемы сравнения, выходы счетчика адреса и одни из входов схемы сравнения являются соответственно адресными выходами и входами устройства, отл-ичающее ся тем, что, с целью повышения быстродействия устройства, оно содержит коммутаторы по числу разрядов кода адреса, одни ИЗ- входов которых подключены к выходам счетчика адреса, а другие входы являются управляющими, прямые и инверсные выходы коммутаторов соединены с другими входами схемы-сравнения и являются информационными выходами устройства. 2.Устройство по п. 1, о т л ичающееся тем,.что каждый коммутатор содержит мультиплексор, элемент НЕ и элементы НЕРАВНОЗНАЧНОСТЬ , одни из входов которых объ-ёдинены и являются одним из входов коммутатора, другой вход первого элемента НЕРАВНОЗНАЧНОСТЬ соединен с -выходом мультиплексора и входом элемента НЕ, выход которого подключен к другому входу второго элемента НЕРАВНОЗНАЧНОСТЬ, входы мультиплексора являются другими входами коммутатора, выходами которого являются выходы элементов НЕРАВНОЗНАЧНОСТЬ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 526954, кл. G 11 С 29/00, 1975. 2.Авторское свидетельство gCCP № 615546, кл. G 11 С 29/00, 1976 (прототип).

--

f-ff

5

7К /

f

10, /4

/

lOfT,

Авторы

Даты

1982-08-30—Публикация

1981-01-12—Подача