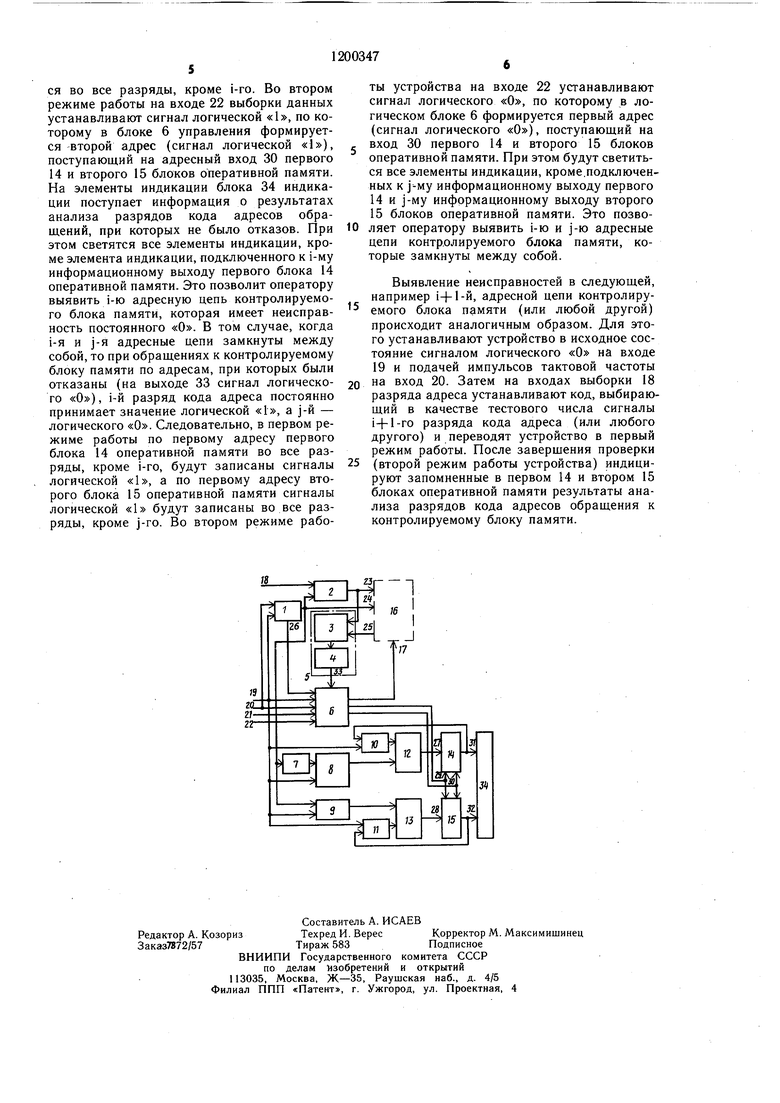

Изобретение относится к вычислительной технике и может быть использовано для контроля оперативных запоминающих устройств (ОЗУ). Цель изобретения - повышение достоверности контроля путем локализации многократных неисправностей адресных цепей блоков памяти постоянного «О или постоянной «1 и многократные замыкания двух адресных цепей собой На чертеже представлена схема устройства для контроля адресных щепей блоков памяти. i Устройство содержит счетчик 1 адреса, мультиплексор 2, блок 3 поразрядного сравнения и элемент ИЛИ 4, составляющие блок 5 сравнения, блок 6 управления, группу элементов НЕ 7, первую группу 8, вторую группу 9, третью группу 10, четвертую группу 11 элементов И, первую группу 12 и вторую группу 13 элементов ИЛИ, первый 14 и второй 15 блоки оперативной памяти. Кроме того, устройство содержит контролируемый блок 16 памяти, шины 17 записи - считывания контролируемого блока памяти, входы 18 выборки разряда адреса устройства, вход 19 начальной установки устройства, вход 20 синхронизации, вход 21 выборки режима, вход 22 выборки данных, входные числовые шины 23 контролируемого блока памяти, адресные шины 24 контролируемого блока памяти, выходные числовые шины 25 контролируемого блока памяти, выход 26 сигнала переполнения счетчика адреса, информационные входы 27 первого блока 14, информационные входы 28 второго блока 15, вход 29 записи - считывания первого и второго блоков, адресный вход 30 первого и второго блоков, информационные выходы 31 первого блока, информационные выходы 32 второго блока, выход 33 элемента ИЛИ, блок 34 индикации. Для приведения устройства в исходное состояние на вход 19 начальной установки подают сигнал логического «О, а на вход 20 синхронизации - импульсы тактовой частоты. Сигнал с входа 19 поступает на вход счетчика адреса и обнуляет его. Кроме TO-N го, этот сигнал поступает на первые входы первой 8, второй 9, третьей10 и четвертой 11 групп элементов И, что приведет к формированию на информационных входах 27 и 28 соответственно первого 14 и второго 15 блоков оперативной памяти сигналов логического «О. Одновременно в блоке 6 управления, на который также поступают сигнал логического «О с входа 19 и импульсы тактовой частоты с входа 20, формируется сигнал записи информации и попеременно первый и второй адреса, поступающие соответственно на вход 29 записи-считывания и адресный вход 30 первого 14 и второго 15 блоков оперативной памяти. Это приводит к записи по первому и вто147 рому адресу обоих блоков исходной нулевой информации. Перед проведением первого режима работы устройства на входах 18 выборки разряда адреса устройства устанавливают код, выбирающий в качестве тестового числа для проверки i-й адресной цепи контролируемого блока памяти сигналы i-ro разряда кода адреса. Для работы устройства в первом режиме на входе 21 выборки режима устанавливают сигнал логической «1, снимают с входа 19 сигнал логического «О, а подают сигнал логической «1 (импульсы тактовой частоты продолжают поступать на вход 20). В первом режиме работы в счетчике 1 адреса под воздействием импульсов тактовой частоты последовательно формируется празрядный код адресов обращения к контролируемому блоку 16 памяти, который поступает на п его адресных входов 24. Кроме того, п-разрядный код адреса поступает на первые входы селектора-мультиплексора 2. На выход селектора-мультиплексора 2 проходят сигналы одного (i-ro) разряда кода адреса (в соответствии с кодом на входах 18). С выхода селектора-мультиплексора 2 тестовое число поступает на все m входных числовых щин контролируемого блока 16 памяти. На шину 17 записи- считывания контролируемого блока памяти с первого выхода логического блока 6 поступают сигналы записи тестовых чисел. После записи тестового числа в контролируемый блок 16 памяти по последнему адресу счетчика 1 адреса продолжает последовательно формироваться адрес обращения, а на выходе 26 переполнения формируется импульс, который поступает в блок 6 управления. Импульс 26 переполнения, поступив в блок 6 управления, запретит поступление на шину 17 сигналов записи тестовых чисел и разрешит поступление на нее сигналов считывания, т. е. начнется считывание тестовых чисел из контролируемого блока памяти. В цикле считывания тестовых чисел на первые m входов блока 3 поразрядного сравнения поступает эталонное тестовое число с выхода селектора-мультиплексора 2. На вторые m входов блока поразрядного сравнения поступают считанные тестовые числа с выходных числовых шин 25 контролируемого блока памяти. При правильном сравнении всех разрядов считанного и эталонного тестовых чисел на выходе 33 элемента ИЛИ 4 формируется сигнал об отсутствии отказа, а при неправильном сравнении, хотя бы в одном разряде - сигнал о наличии отказа. Эти сигналы поступают на первый вход блока 6 управления. Если отказы есть, то на выход 33 поступает сигнал логического «О и в логическом блоке 6 формируется первый адрес (например, логический «О), который с его третьего выхода поступает на адресный вход 30 первого 14 и второго 15 блоков оперативной памяти. Если отказов нет, то на выход 33 поступает сигнал логической «1 и на третьем выходе логического блока 6 формируется второй адрес (логическая «1). Кроме того, с второго выхода блока 6 управления, в каждом такте считывания тестового числа из контролируемого блока 16 памяти, на вход 29 записи-считывания первого 14 и второго 15 блоков оперативной памяти поступают сигналы записи. Одновременно с выходов счетчика 1 адреса п-разрядный код адреса поступает на вторые входы п элементов И второй группы 9 и на входы п элементов НЕ 7. С выходов элементов НЕ 7 инвертированный п-разрядный код адреса поступает на вторые входы п элементов И первой группы 8. На первые входы элементов И первой 8 и второй 9 групп поступают сигналы логической «1 с входа 19. Если все п разрядов кода адреса обращения имеют состояние логической «, то со всех выходов п элементов И второй группы 9 сигналы логической «1 через п элементов ИЛИ второй группы 13 пройдут на п информационных входов 28 второго блока 15 оперативной памяти и запишутся во все п его разрядов по первому адресу, если были отказы при считывании тестового числа из контролируемого блока 16 памяти, или по второму адресу, если отказов не было. На информационные входы 27 первого блока 14 оперативной памяти сигналы логической «1 не поступят и в нем сохранится исходная нулевая информация. Аналогично, если все п разрядов кода адреса обращения имеют состояние логического «О, то сигналы логической «1 с выходов группы элементов НЕ 7 пройдут на п выходов элементов И первой группы 8 и через п элементов ИЛИ первой группы 12 поступят на информационные входы 27 только первого блока 14 оперативной памяти и запищутся во все п его разрядов по первому или второму адресу. Однажды записанная в первый 14 или второй 15 блоки оперативной памяти логическая «1 затем повторно переписывается в него во всех остальных тактах проверки, поступая соответственно на информационные входы 27 или 28 по цепи: информационные выходы 31 первого блока 14 оперативной памяти, вторые входы элементов И третьей группы 10, первые входы элементов ИЛИ первой группы 12 или по цепи: информационные выходы 32 второго блока 15 оперативной памяти, вторые входы элементов И четвертой группы 11, вторые входы элементов ИЛИ второй группы 12. Следовательно, если при считывании тестового числа из контролируемого блока 16 памяти, при котором был (не был) зафиксирован отказ, i-й разряд кода адреса обращения был хотя бы один раз равен сигналу логического «О, то по первому (второму) адресу в i-й разряд первого блока 14 оперативной памяти запишется сигнал логической «1, который сохранится до конца работы устройства в первом режиме. Аналогично, если при считывании тестового числа из контролируемого блока 16 памяти, при котором был (не был) зафиксирован отказ, i-й разряд кода адреса обращения был хотя бы один раз равен сигналу логической «1, то по первому (второму) адресу в i-й разряд второго блока 15 оперативной памяти запишется сигнал логической «1, который сохранится до конца работы устройства в первом режиме. После обращения со считыванием тестового числа из контролируемого блока памяти по последнему адресу счетчик 1 адреса продолжает последовательно формировать адреса обращения, а на выходе 26 переполнения сформируется импульс переноса, который поступит в блок 6 управления. Импульс переноса, поступив в блок 6 управления, запретит поступление на щину 17 сигналов считывания и разрешит поступление на нее сигналов записи, т. е. начнется повторная проверка 1-й адресной цепи контролируемого блока памяти. Для перехода из первого во второй режим работы устройства прекращают подачу импульсов тактовой частоты по входу 20, а на вход 21 выборки режима работы подают сигнал логического «О. При наличии на входе 21 сигнала логического «О блок 6 управления формирует на своем третьем выходе сигналы считывания информации, записанной в первый 14 и второй 15 блоки оперативной памяти в первом режиме работы (сигнал считывания поступает на вход 29). Установленный на входе 22 вь1борки данных сигнал логического «О или логической «1 приведет к формированию в логическом блоке 6 соответственно первого или второго адреса первого 14 и второго 15 блоков оперативной памяти, поступающего на вход 30. С информационных выходов 31 и 32 соответственно информация о заполненных результатах анализа кода адресов обращений поступает для визуального контроля на 2 п элементов индикации блока 34 индикации. Если на 1-й адресной цепи контролируемого блока 16 памяти присутствует неисправность постоянного «О, i-й разряд кода адресов обращений к контролируемому блоку памяти, при которых отсутствуют отказы (на выходе 33 сигнал логической «1), постоянно принимает значения логической «1, тогда как все остальные разряды этих адресов принимают значения как логической «1, так и логического «О. Следовательно, в первом режиме работы по второму адресу в i-й разряд второго блока 15 оперативной памяти и во все его остальные разряды записываются сигналы логической «1, а по второму адресу первого блока 14 оперативной памяти сигналы логической «1 записываются во все разряды, кроме i-ro. Во втором режиме работы на входе 22 выборки данных устанавливают сигнал логической «1, по которому в блоке 6 управления формируется второй адрес (сигнал логической «1), поступающий на адресный вход 30 первого 14 и второго 15 блоков оперативной памяти. На элементы индикации блока 34 индикации поступает информация о результатах анализа разрядов кода адресов обращений, при которых не было отказов. При этом светятся все элементы индикации, кроме элемента индикации, подключенного к i-му информационному выходу первого блока 14 оперативной памяти. Это позволит оператору выявить i-ю адресную цепь контролируемого блока памяти, которая имеет неисправность постоянного «О. В том случае, когда i-я и j-я адресные цепи замкнуты между собой, то при обращениях к контролируемому блоку памяти по адресам, при которых были отказаны (на выходе 33 сигнал логического «О), i-й разряд кода адреса постоянно принимает значение логической «Г, а j-й - логического «О. Следовательно, в первом режиме работы по первому адресу первого блока 14 оперативной памяти во все разряды, кроме i-ro, будут записаны сигналы логической «1, а по первому адресу второго блока 15 оперативной памяти сигналы логической «1 будут записаны во все разряды, кроме j-ro. Во втором режиме работы устройства на входе 22 устанавливают сигнал логического «О, по которому в логическом блоке 6 формируется первый адрес (сигнал логического «О), поступающий на ВХОД 30 первого 14 и второго 15 блоков оперативной памяти. При этом будут светиться все элементы индикации, кроме.подключенных к информационному выходу первого

14и j-му информационному выходу второго

15блоков оперативной памяти. Это позволяет оператору выявить i-ю и j-ю адресные

цепи контролируемого блока памяти, которые замкнуты между собой.

Выявление неисправностей в следующей, например i+1-й, адресной цепи контролируемого блока памяти (или любой другой) происходит аналогичным образом. Для этого устанавливают устройство в исходное состояние сигналом логического «О на входе 19 и подачей импульсов тактовой частоты

на вход 20. Затем на входах выборки 18 разряда адреса устанавливают код, выбирающий в качестве тестового числа сигналы i+1-го разряда кода адреса (или любого другого) и переводят устройство в первый режим работы. После заверщения проверки

(второй режим работы устройства) индицируют запомненные в первом 14 и втором 15 блоках оперативной памяти результаты анализа разрядов кода адресов обращения к контролируемому блоку памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля адресных цепей боков памяти | 1985 |

|

SU1274007A1 |

| Устройство адресации оперативной памяти | 1987 |

|

SU1417003A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

| Устройство адресации оперативной памяти | 1985 |

|

SU1262497A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1261014A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АДРЕСНЫХ ЦЕПЕЙ БЛОКОВ ПАМЯТИ, содержащее счетчик адреса, один вход которого является входом начальной установки устройства, а другой - входом синхронизации устройства, мультиплексор, входы первой группы которого соединены с входами выборки разряда адреса устройства, входы второй группы соединены с выходами счетчика адреса и являются адресными выходами устройства, а выходы являются информационными выходами устройства и подключены к входам первой группы блока сравнения, входы второй группы которого являются информационными входами устройства, блок управления, первый выход которого является управляющим выходом устройства, отличающееся тем, что, с целью повыщения достоверности контроля, в него введена группа элементов НЕ, первая, вторая, третья и четвертая группы элементов И, первая и вторая группы элементов ИЛИ, первый и второй блоки оперативной памяти, причем первый, второй, третий, четвертый и щестой входы блока управления соединены соответственно с выходом переполнения счетчика адреса, выходом блока сравнения, входами выборки режима, выборки данных и синхронизации устройства, пятый, вход блока управления подключен к входу начальной установки устройства и к вторым входам элементов И первой, второй, третьей и четвертой групп, а второй и третий выходы блока управления соединены с управляющим и адресным входами первого и второго блоков оперативной памяти соответственно, информационные выходы которых являются соответственно выходами результатов контроля я подключены к первым входам элементов И третьей и четвертой групп соответственно, входы элементов НЕ группы соединены с выходами счетчика адреса и первыми входами элементов И втoJ)OЙ группы, а выходы подключены к первым входам элементов И первой группы, первые и вторые входы элементов ИЛИ первой группы соединены с выходами элементов И третьей и первой групп соответственно, а выходы подк:) ключены к информационным входам первого блока оперативной памяти, первые и вторые входы элементов ИЛИ второй группы со соединены с выходами элементов И второй и четвертой групп соответственно, а выходы подключены к информационным входам второго блока оперативной памяти.

| Заявка США № 3727039, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Запоминающее устройство с обнаружением отказавших блоков | 1980 |

|

SU903974A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-12-23—Публикация

1984-06-06—Подача