(54) УСТРОПСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU902077A1 |

| Устройство для контроля блоков памяти | 1979 |

|

SU790019A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

| Устройство для контроля адресных цепей боков памяти | 1985 |

|

SU1274007A1 |

| Устройство для контроля адресных цепей блоков памяти | 1984 |

|

SU1200347A1 |

| Устройство для формирования тестовой последовательности | 1986 |

|

SU1529293A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля памяти | 1981 |

|

SU1001180A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

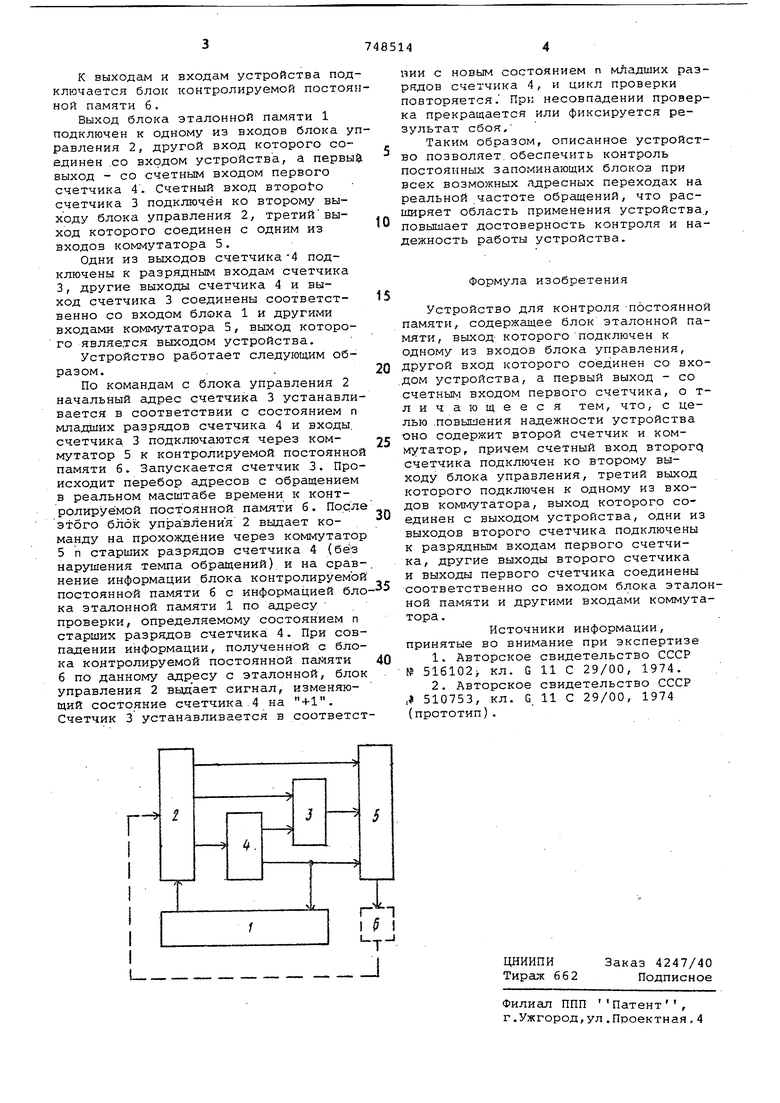

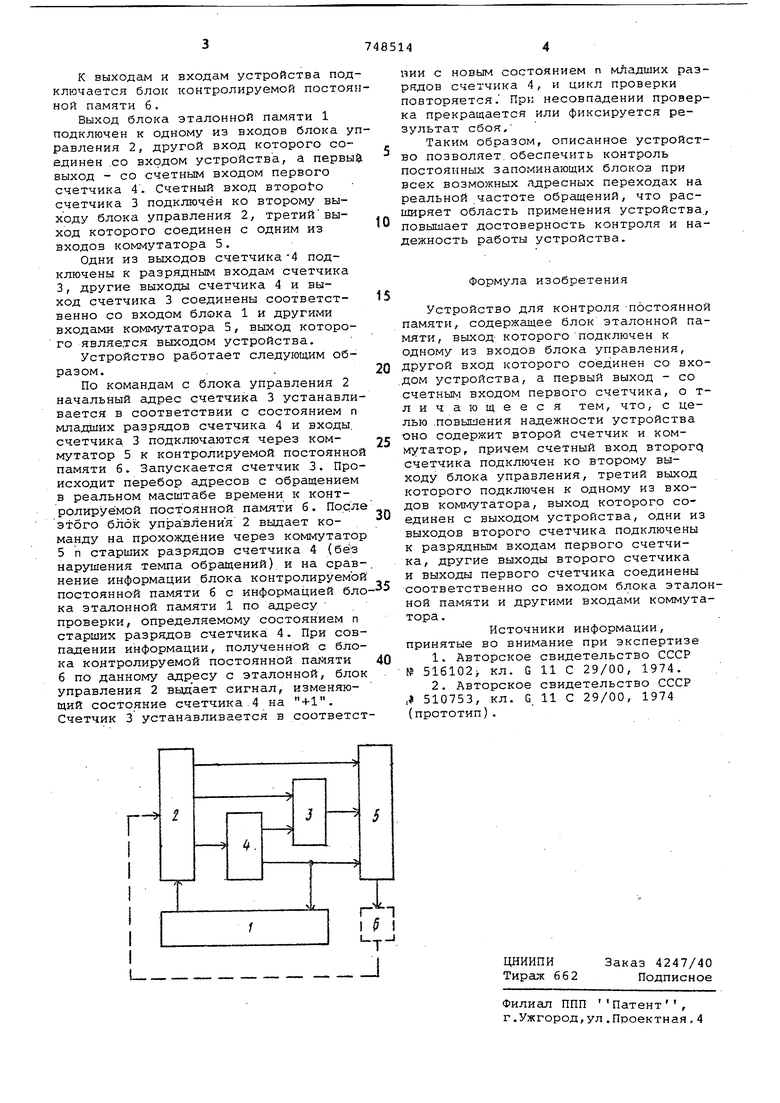

Изобретение относится к области запоминающих устройств. Известны устройства для контроля постоянной памяти 1, С2 . В одном из известных устройств контроль постоянных запоминающих блоков осу1Дествляется пос.педователь ным считыванием некоторого массива информации с образованием контрольного кода этого массива и последующим сравнением этого кода с эталонным значением . Недостатком такого устройства является невысокая эффективность ко роля.. Из известных устройств наиболее близким техническим решением к данн му изобретению является устройство для контроля постоянной памяти, содержащее блок эталонной памяти, выход которого подключен к одному из входов блока управления, другой вхо которого соединен со входом устройс а первый выход - со счетным входом первого счетчика 2 . Недостатком этого устройства 1явл ется то, что контроль постоянного з уюминающего блока выполняется тольк при последовательном считывании инф различных адресных переходах не проверяется, в результате чего снижается достоверность контроля и надежность устройства. Целью изобретения является повышение надежности у стройства,;- контроля и расширение области его применения. Поставленная цель достигается тем, что устройство содержит второй счетчик и коммутатор, причем счетный вход второго счетчика подключен ко второму выходу блока управления, третий выход которого подключен к одному из входов коммутатора, выход которого соединен с выходом устройства, одни из выходов второго счетчика подключены к разрядным входам первого счетчика, другие выходы второго счетчика и выходы первого счетчика соединены соответственно со входом блока эталонной памяти и другими входами коммутатора. На чертеже изображена блок-схема описываемого устройства. Устройство содержит блок эталонной памяти 1, блок управления 2, первый 3 и второй 4 счетчики, комК выходам и входам устройства под ключается блок контролируемой постоя ной памяти б. Выход блока эталонной памяти 1 подключен к одному из входов блока уп равления 2, другой вход которого соединен .со входом устройства, а первы выход - со счетным входом первого счетчика 4. Счетный вход Bxopoto счетчика 3 подключён ко второму выходу блока управления 2, третийвыход которого соединен с одним из входов кoм /Iyтaтopa 5 . Одни из выходов счетчика 4 подключены к разрядным входам счетчика 3, другие выходы счетчика 4 и выход счетчика 3 соединены соответственно со входом блока 1 и другими входами коммутатора 5, выход которого является выходом устройства. Устройство работает следуюгдим образом. По командам с блока управления 2 начальный адрес счетчика 3 устанавли вается в соответствии с состоянием п младших разрядов счетчика 4 и входы, счетчика 3 подключаются через коммутатор 5 к контролируемой постоянной памяти б. Запускается счетчик 3. Про исходит перебор адресов с обращением в реальном масштабе времени к контролируемой постоянной памяти б. Подл этого блок управления 2 выдает команду на прохождение через ком1 1утатор 5п старших разрядов счетчика 4 (без нарушения темпа обращений) и на сравнение информации блока контролируемой постоянной памяти б с информацией бло ка эталонной памяти 1 по адресу проверки, определяемому состоянием п старших разрядов счетчика 4. При совпадении информации, полученной с блока контролируемой постоянной памяти 6по данному адресу с эталонной, блок управления 2 выдает сигнал, изменяющий состояние счетчика.4 на +1. Счетчик 3 устанавливается в соответст ПИИ с новым состоянием п младших разрядов счетчика 4, и цикл проверки повторяется. При несовпадении проверка прекращается или фиксируется результат сбоя. Таким образом, описанное устройство позволяет.обеспечить контроль постоянных запоминающих блоков при всех возможных «адресных переходах на реальной частоте обращений, что расширяет область применения устройства., повышает достоверность контроля и надежность работы устройства. Формула изобретения Устройство для контроля -постоянной памяти, содержащее блок эталонной памяти, выход- которогоподключен к одному из входов блока управления, другой вход которого соединен со входом устройства, а первый выход - со счетныь- входом первого счетчика, о тличающееся тем, что, с целью .повышения надежности устройства оно содержит второй счетчик и коммутатор, причем счетный вход второго счетчика подключен ко второму выходу блока управления, третий выход которого подключен к одному из входов ком14утатора, выход которого соединен с выходом устройства, одни из выходов второго счетчика подключены к разрядным входам первого счетчика, другие выходы второго счетчика и выходы первого счетчика соединены соответственно со входом блока эталонной памяти и другими входами коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 516102у кл. G 11 С 29/00, 1974. 2.Авторское свидетельство СССР , 510753, кл. G 11 С 29/00, 1974 (прототип).

Авторы

Даты

1980-07-15—Публикация

1978-06-05—Подача