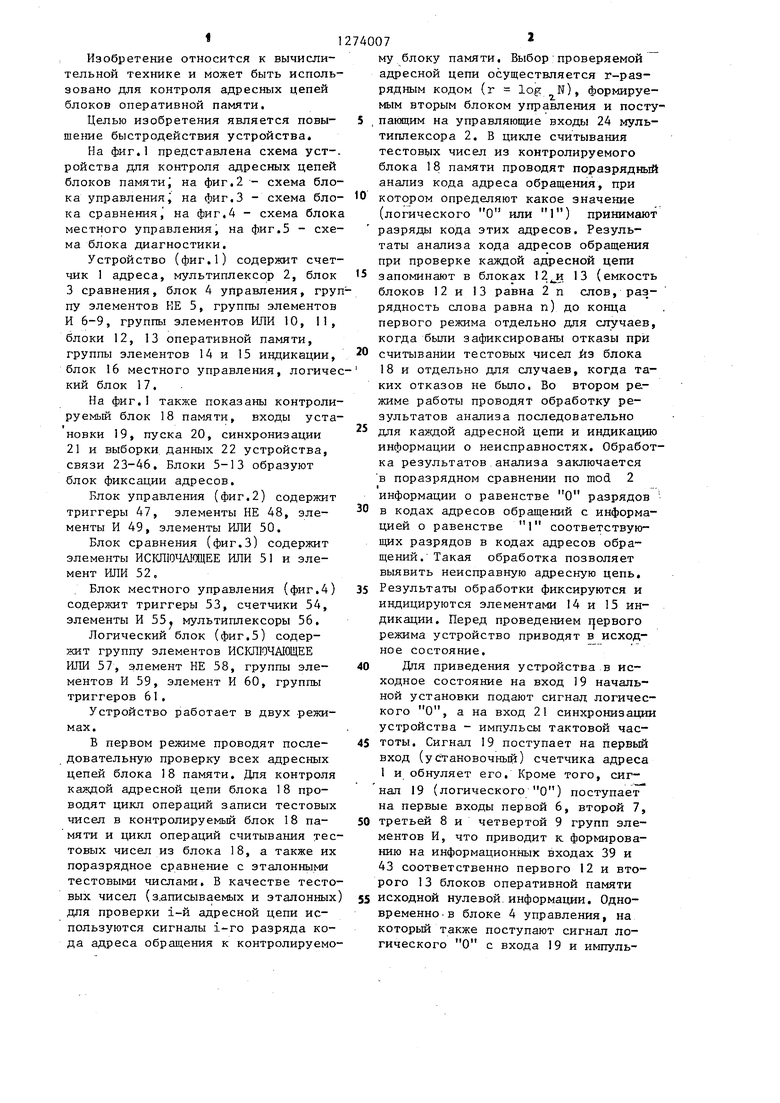

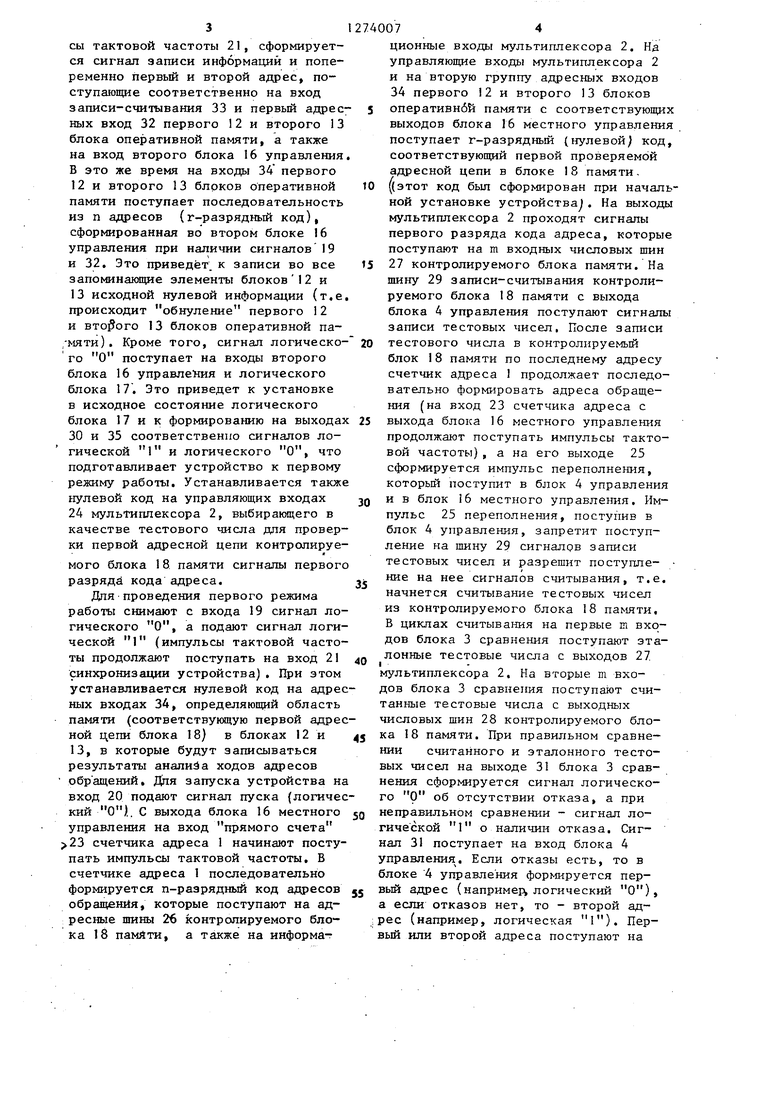

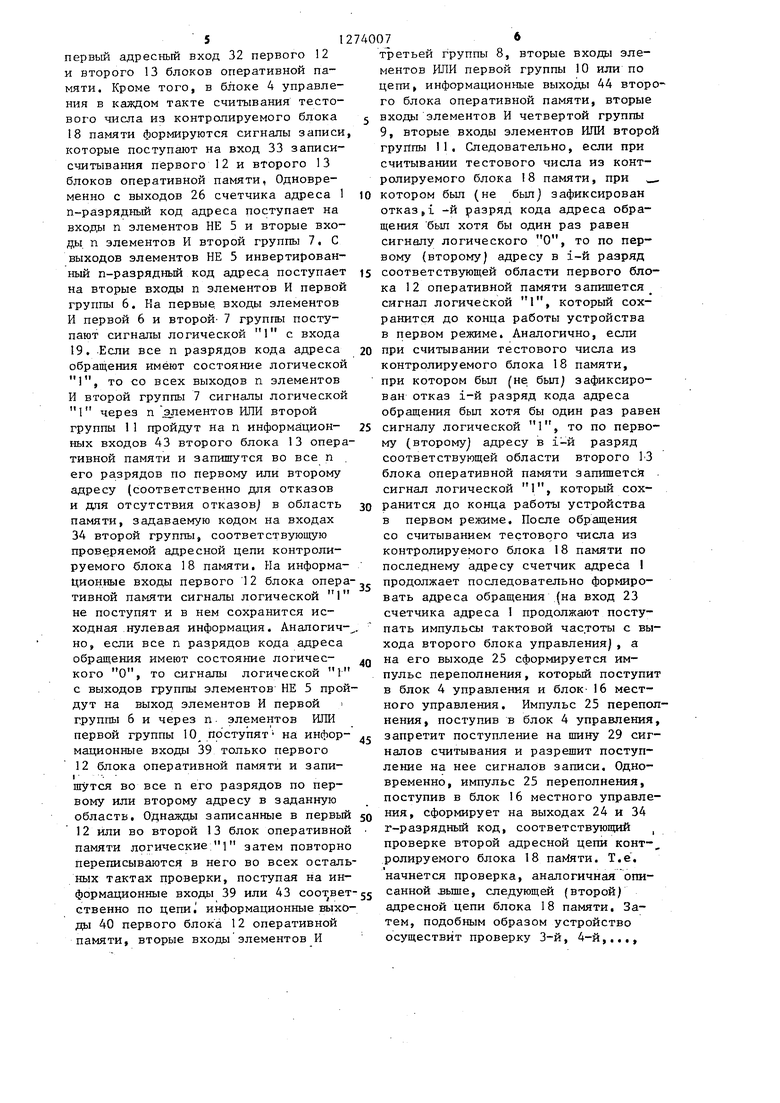

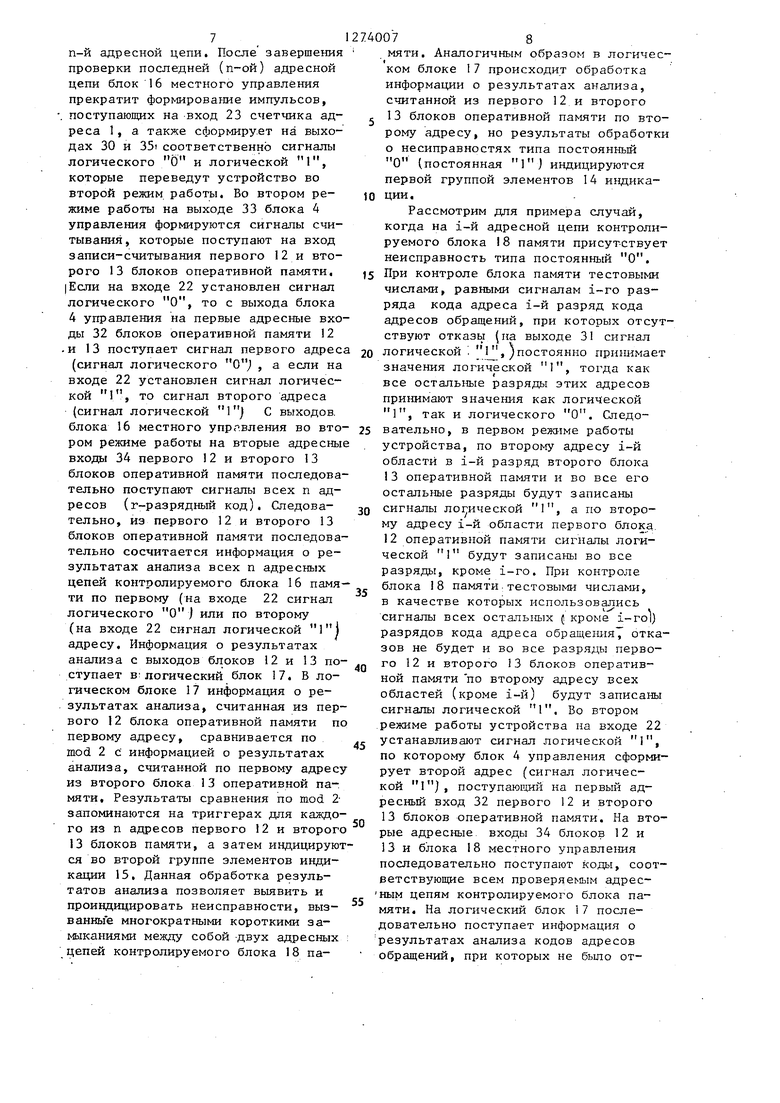

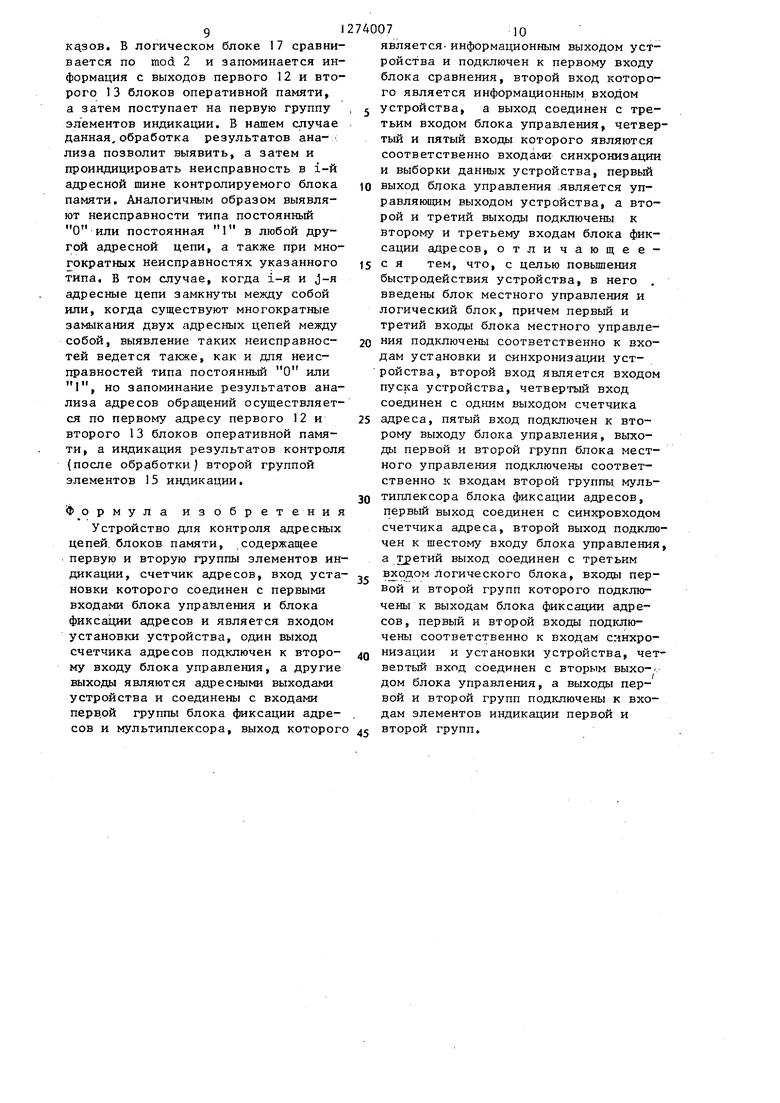

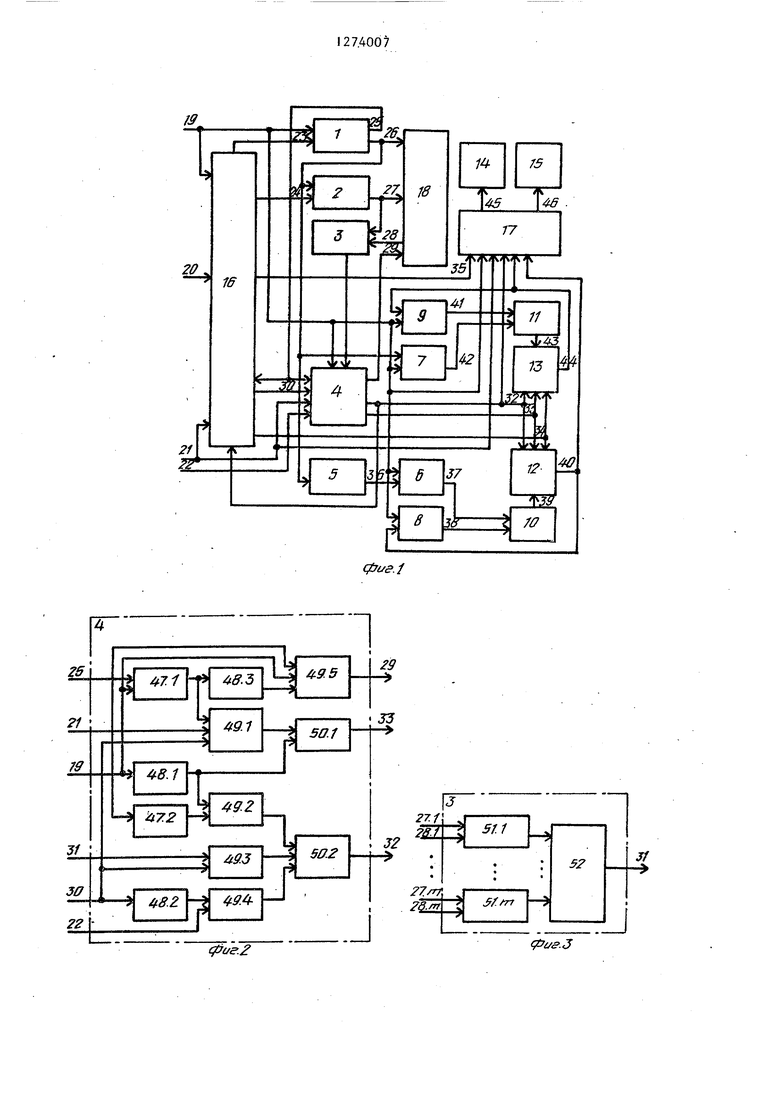

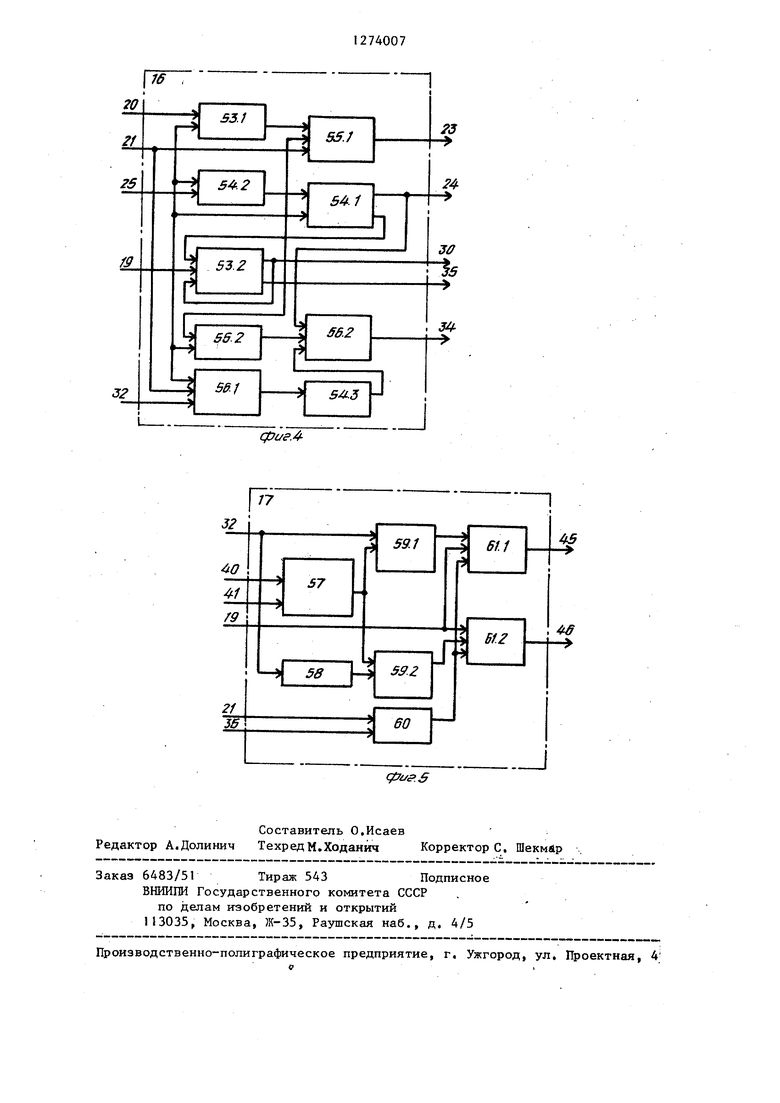

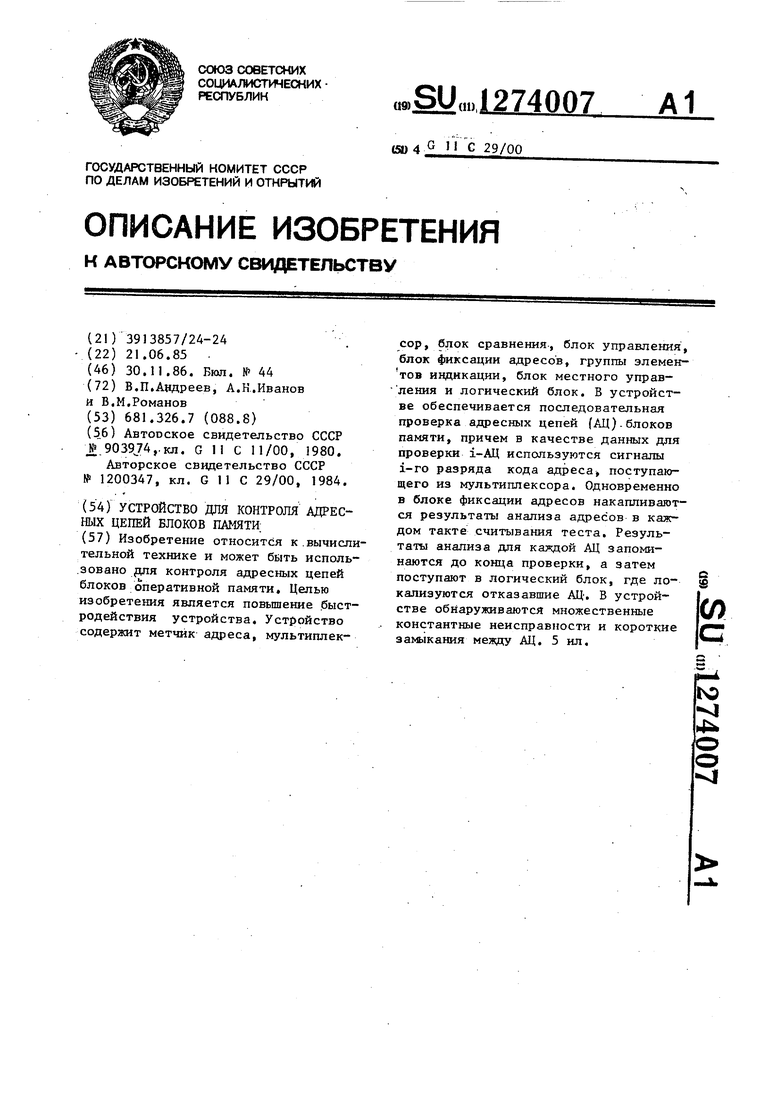

Изобретение относится к вычислительной технике и может быть использовано для контроля адресных цепей блоков оперативной памяти. Целью изобретения является повышение быстродействия устройства. На фиг.1 представлена схема уст-. ройства для контроля адресных цепей блоков памятиi на фиг.2 - схема блока управленияi на фиг.З - схема блока сравнения, на фиг.4 - схема блока местного управления, на фиг.З - схема блока диагностики. Устройство (фиг.1) содержит счетчик 1 адреса, мультиплексор 2, блок 3 сравнения, блок 4 управления, груп пу элементов КЕ 5, группы элементов И 6-9, группы элементов ИЛИ 10, П, блоки 12, 13 оперативной памяти, группы элементов 14 и 15 индикации, блок 16 местного управления, логичес кий блок 17.. На фиг.1 также показаны контролируемый блок 18 памяти, входы установки 19, пуска 20, синхронизации 21 и выборки данных 22 устройства, связи 23-46. Блоки 5-13 образуют блок фиксации адресов. Блок управления (фиг.2) содержит триггеры 47, элементы НЕ 48, элементы И 49, элементы ИЛИ 50. Блок сравнения (фиг.З) содержит элементы ИСКПЮЧАЩЕЕ ИЛИ 51 и элемент ИЛИ 52, Блок местного управления (фиг.4) содержит триггеры 53, счетчики 54, элементы И 55. мультиплексоры 56. Логический блок (фиг.5) содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 57, элемент НЕ 58, группы элементов И 59, элемент И 60, группы триггеров 61. Устройство работает в двух режимах. В первом режиме проводят последовательную проверку всех адресных цепей блока 18 памяти. Дпя контроля каждой адресной цепи блока 18 проводят цикл операций записи тестовых чисел в контролируемьм блок 18 памяти и цикл операций считывания тес товых чисел из блока 18, а также их поразрядное сравнение с эталонными тестовыми числами. В качестве тестовых чисел (з.аписываемых и эталонных для проверки i-й адресной цепи используются сигналы i-го разряда кода адреса обращения к контролируемо му блоку памяти. Выбор проверяемой адресной цепи осуществляется г-разрядным кодом (г log N), формируемым вторым блоком управления и поступагацим на управляющие входы 24 мультиплексора 2. В цикле считывания тестовых чисел из контролируемого блока 18 памяти проводят поразрядный анализ кода адреса обращения, при КОТОР07-4 определяют какое значение (логического О или 1) принимают разряды кода этих адресов. Результаты анализа кода адресов обращения при проверке каждой адресной цепи запоминают в блоках 12jH 13 (емкость блоков 12 и 13 равна 2 п слов, разрядность слова равна п) до конца первого режима отдельно для случаев, когда были зафиксированы отказы при считывании тестовых чисел из блока 18 и отдельно для случаев, когда таких отказов не бьшо. Во втором режиме работы проводят обработку результатов анализа последовательно для каждой адресной цепи и индикацию информации о неисправностях. Обработка результатов анализа заключается в поразрядном сравнении по mod 2 информации о равенстве О разрядов в кодах адресов обращений с информацией о равенстве 1 соответствующих разрядов в кодах адресов обращений. Такая обработка позволяет выявить неисправную адресную цепь, Результаты обработки фиксируются и индицируются элементами 14 и 15 индикации. Перед проведением цервого режима устройство приводят в исходное состояние. Для приведения устройства в исходное состояние на вход 19 начальной установки подают сигнал логического О, а на вход 21 синхронизации устройства - импульсы тактовой частоты. Сигнал 19 лоступает на Первьй вход (установочный) счетчика адреса I и обнуляет его. Кроме того, сигнал 19 (логического О) поступает на первые входы первой б, второй 7, третьей 8 и четвертой 9 групп элементов И, что приводит к формированию на информационных входах 39 и 43 соответственно первого 12 и второго 13 блоков оперативной памяти исходной нулевой, информации. Одновременно-в блоке 4 управления, на который также поступают сигнал логического О с входа 19 и импуль3I

сы тактовой частоты 21, сформируется сигнал записи информации и попеременно первый и второй адрес, поступающие соответственно на вход записи-считывания 33 и первый адресных вход 32 первого 12 и второго 13 блока оперативной памяти, а также на вход второго блока 16 управления. В это же время на входы 34 первого

12и второго 13 блоков оперативной памяти поступает последовательность из п адресов {г-разрядный код), сформированная во втором блоке 16 управления при наличии сигналов 19 и 32. Это приведёт, к записи во все запоминающие элементы блоков 12 и

13исходной нулевой информации (т.е. происходит обнуление первого 12

и второго 13 блоков оперативной памяти). Кроме того, сигнал логического О поступает на входы второго блока 16 управления и логического блока 17. Это приведет к установке в исходное состояние логического блока 17 и к формированию на выходах 30 и 35 соответственно сигналов логической 1 и логического О, что подготавливает устройство к первому режиму работы. Устанавливается также нулевой код на управляющих входах 24 мультиплексора 2, выбирающего в качестве тестового числа для проверки первой адресной цепи контролируемого блока 18 памяти сигналы первого разряда кода адреса.

Для проведения первого режима работы снимают с входа 19 сигнал логического О, а подают сигнал логической 1 (импульсы тактовой частоты продолжают поступать на вход 21 синхронизации устройства). При этом устанавливается нулевой код на адресных входах 34, определяющий область памяти (соответствующую первой адресной цепи блока 18) в блоках 12 и 13, в которые будут записываться результаты анализа ходов адресов обращений. Для запуска устройства на вход 20 подают сигнал пуска {логический О).. С выхода блока 16 местного управления иа вход прямого счета 23 счетчика адреса 1 начинают поступать импульсы тактовой частоты. В счетчике адреса 1 последовательно формируется п-раэрядный код адресов обращения, которые поступают на адресные шины 26 контролируемого блока 18 памйти, а также на информа-г

740074

ционные входы мультиплексора 2. На управляющие входы мультиплексора 2 и на вторую группу адресных входов 34 первого 12 и второго 13 блоков 5 оперативнбй памяти с соответствующих выходов блока 16 местного управления поступает г-разрядный (нулевой) код, соответствующий первой проверяемой адресной цепи в блоке 18 памяти, to ((этот код был сформирован при начальной установке ycтpoйcтвaj. На выходы мультиплексора 2 проходят сигналы первого разряда кода адреса, которые поступают на m входных числовых шин 15 27 контролируемого блока памяти. На шину 29 записи-считывания контролируемого блока 18 памяти с выхода блока 4 управления поступают сигналы записи тестовых чисел, После записи 20 тестового числа в контролируемый

блок 18 памяти по последнему адресу счетчик адреса 1 продолжает последовательно формировать адреса обращения (на вход 23 счетчика адреса с 5 выхода блока 16 местного управления продолжают поступать импульсы тактовой частоты), а на его выходе 25 сформируется импульс переполнения, который поступит в блок 4 управления 0 и в блок 16 местного управления. Импульс 25 переполнения, поступив в блок 4 управления, запретит поступление на шину 29 сигналрв записи тестовых чисел и разрешит поступле- ние на нее сигналов считывания, т.е. начнется считывание тестовых чисел из контролируемого блока 18 памяти. В циклах считывания на первые m входов блока 3 сравнения поступают эталонные тестовые числа с выходов 27 мультиплексора 2. На вторые m входов блока 3 сравнения поступают считанные тестовые числа с выходных числовых шин 28 контролируемого блоз ка 1В памяти. При правильном сравнении считанного и эталонного тестовых чисел на выходе 31 блока 3 сравнения сформируется сигнал логического О об отсутствии отказа, а при Q неправильном сравнении - сигнал логической 1 о наличии отказа. Сигнал 31 поступает на вход блока 4 управления. Если отказы есть, то в блоке 4 управления формируется первый адрес (например логический О), а если отказов нет, то - второй ад:рес (например, логическая I). Первый или второй адреса поступают на первый адресный вход 32 первого 12 и второго 13 блоков оперативной памяти. Кроме того, в блоке 4 управления в каждом такте считывания тестового числа из контролируемого блока 18 памяти формируются сигналы записи которые поступают на вход 33 записисчитывания первого 12 и второго 13 блоков оперативной памяти, Одновременно с выходов 26 счетчика адреса 1 п-разрядный код адреса поступает на входы п элементов НЕ 5 и вторые входы п элементов И второй группы 7. С выходов элементов НЕ 5 инвертированный п-разрядный код адреса поступает на вторые входы п элементов И первой группы 6. На первые входы элементов И первой 6 и второй- 7 группы поступают сигналы логической 1 с входа 19. .Если все п разрядов кода адреса обращения имеют состояние логической 1, то со всех выходов п элементов И второй группы 7 сигналы логической 1 через п длементов ИЛИ второй группы 11 пройдут на п информационных входов 43 второго блока 13 опера тивной памяти и запишутся во все п его разрядов по первому или второму адресу (соответственно для отказов и для отсутствия отказов в область памяти, задаваемую кодом на входах 34 второй группы, соответствующую проверяемой адресной цепи контролируемого блока 18 памяти. На информационные входы первого 12 блока опера тинной памяти сигналы логической 1 не поступят и в нем сохранится исходная нулевая информация. Аналогично, если все п разрядов кода адреса обращения имеют состояние логического О, то сигналы логической 1 с выходов группы элементов- НЕ 5 прой дут на выход элементов И первой группы б и через п. элементов ИЛИ первой группы 10 прступят на информационные входы 39 только первого 12 блока оперативной памяти и запишутся во все п его разрядов по первому или второму адресу в заданную область. Однажды записанные в первый 12 или во второй 13 блок оперативной памяти логические 1 затем повторно переписываются в него во всех осталь ных тактах проверки, поступая на информационные входы 39 или 43 ственно по цепи информационные выхо ды 40 первого блока 12 оперативной памяти, вторые входы элементов И третьей группы 8, вторые входы элементов ИЛИ первой группы 10 или по цепи, информационные выходы 44 второго блока оперативной памяти, вторые входы элементов И четвертой группы 9, вторые входы элементов ИЛИ второй группы 1. Следовательно, если при считывании тестового числа из контролируемого блока 8 памяти, при котором был (не был зафиксирован отказ 5i -и разряд кода адреса обращения был хотя бы один раз равен сигналу логического О, то по первому (второму) адресу в 1-й разряд соответствующей области первого блока 12 оперативной памяти запишется сигнал логической 1, который сохранится до конца работы устройства в первом режиме. Аналогично, если при считывании тестового числа из контролируемого блока 18 памяти, при котором был (не был зафиксирован отказ i-й разряд кода адреса обращения был хотя бы один раз равен сигналу логической 1, то по первому (второму адресу в i-й разряд соответствующей области второго 13 блока оперативной памяти запишется . сигнал логической 1, который сохранится до конца работы устройства в первом режиме. После обращения со считыванием тестового числа из контролируемого блока 18 памяти по последнему адресу счетчик адреса I продолжает последовательно формировать адреса обращения (на вход 23 счетчика адреса 1 продолжают поступать импульсы тактовой частоты с выхода второго блока управления, а на его выходе 25 сформируется импульс переполнения, который поступит в блок 4 управления и блок- 16 местного управления. Импульс 25 переполнения, поступив в блок 4 управления, запретит поступление на шину 29 сигналов считывания и разрешит поступление на нее сигналов записи. Одновременно, импульс 25 переполнения, поступив в блок 16 местного управления, сформирует на выходах 24 и 34 г-разрядный код, соответствующий проверке второй адресной цепи конт- ролируемого блока 18 паМяти. Т.е. начнется проверка, аналогичная описанной ьше, следующей (второй) адресной цепи блока 18 памяти. Затем, подобным образом устройство осуществит проверку 3-й, 4-й,..,, n-й адресной цепи. После завершения проверки последней (п-ой) адресной цепи блок 16 местного управления прекратит формирование импульсов, . поступающих на вход 23 счетчика адреса 1, а также сформирует на выходах 30 и 35i соответственно сигналы логического б и логической 1, которые переведут устройство во второй режим, работы. Во втором режиме работы на выходе 33 блока 4 управления формируются сигналы считывания, которые поступают на вход записи-считывания первого 2 и второго 13 блоков оперативной памяти. |Если на входе 22 установлен сигнал логического О, то с выхода блока 4 управления на первые адресные вхо ды 32 блоков оперативной памяти 12 -и 13 поступает сигнал первого адрес (сигнал логического , а если на входе 22 установлен сигнал логической I, то сигнал второго адреса (сигнал логической 1) С выходов. блока 16 местного управления во вто ром режиме работы на вторые адресны входы 34 первого 12 и второго 13 блоков оперативной памяти последова тельно поступают сигналы всех п адресов (г-разрядный код). Следовательно, из первого 12 и второго 13 блоков оперативной памяти последова тельно сосчитается информация о результатах анализа всех п адресных цепей контролируемого блока 16 памя ти по первому (на входе 22 сигнал логического О | или по второму (на входе 22 сигнал логической IM адресу. Информация о результатах анализа с выходов блоков 12 и 13 по ступает в: логический блок 17. В логическом блоке 17 информация о результатах анализа, считанная из пер вого 12 блока оперативной памяти п первому адресу, сравнивается по mod 2 с информацией о результатах анализа, считанной по первому адрес из второго блока 13 оперативной памяти. Результаты сравнения по mod 2 запоминаются на триггерах для каждо го из п адресов первого 12 и второг 13 блоков памяти, а затем индицирую ся во второй группе элементов индикации 15. Данная обработка результатов анализа позволяет выявить и проиндицировать неисправности, вызванные многократными короткими запеканиями между собой двух адресных цепей контролируемого блока 18 па- мяти. Аналогичным образом в логическом блоке 17 происходит обработка информации о результатах анализа, считанной из первого 12 и второго 13 блоков оперативной памяти по второму адресу, но результаты обработки о несиправностях типа постоянный О (постоянная 1Ч индицируются первой группой элементов 14 и одикации. Рассмотрим для примера случай, когда на i-й адресной цепи контролируемого блока 8 памяти присутствует неисправность типа постоянный О. При контроле блока памяти тестовыми числами, равными сигналам 1-го разряда кода адреса i-й разряд кода адресов обращений, при которых отсутствуют отказы (на выходе 31 сигнал логической . 1, )постоянно при1шмает значения логической тогда как все остальные разряды этих адресов принимают значения как логической 1, так и логического О. Следовательно, в первом режиме работы устройства, по второму адресу i-й области в i-й разряд второго блока 3 оперативной памяти и во все его остальные разряды будут записаны сигналы логической 1, а по второму адресу i-й области первого блока. 12 оперативной памяти сигналы логической 1 будут записаны во все разряды, кроме i-ro. При контроле блока 18 памяти;тестовыми числами, в качестве которых использовались сигналы всех остальных f кроме i-rol) разрядов кода адреса обращеюмУ отказов не будет и во все разряды первого 1 2 и второго 13 блоков оперативной памяти по второму адресу всех областей (кроме i-й) будут записаны сигналы логической 1, Во втором режиме работы устройства на входе 22 устанавливают сигнал логической I, по которому блок 4 управления сформирует второй адрес (сигнал логической 1), поступающий на первый адресный вход 32 первого 12 и второго 13 блоков оперативной памяти. На вторые адресные входы 34 блоков 12 и 13 и блока 18 местного управлегшя последовательно поступают коды, соответств ющие всем проверяемым адресным цепям контролируемого блока памяти. На логический блок 17 последовательно поступает информация о результатах анализа кодов адресов обращений, при которых не было откдзов. в логическом блоке 17 сравнивается по mod 2 и запоминается информация с выходов первого 12 и второго 13 блоков оперативной памяти, а затем поступает на первую группу элементов индикации. В нашем случае данная, обработка результатов анализа позволит выявить, а затем и проиндицировать неисправность в i-й адресной шине контролируемого блока памяти. Аналогичным образом выявляют неисправности типа постоянный О или постоянная 1 в любой другой адресной цепи, а также при многократных неисправностях указанного типа, В том случае, когда i-я и J-я адресные цепи замкнуты между собой или, когда существуют многократные замыкания двух адресных цепей между собой, выявление таких неисправностей ведется также, как и дпя неисправностей типа постоянный О или 1, но запоминание результатов анализа адресов обращений осуществляется по первому адресу первого 12 и второго 13 блоков оперативной памяти, а индикация результатов контроля (после обработки) второй группой элементов 15 индикации.

Формула изобретения Устройство для контроля адресных цепей, блоков памяти, содержащее первую и вторую группы элементов индикации, счетчик адресов, вход установки которого соединен с первыми входами блока управления и блока фиксации адресов и является входом установки устройства, один выход счетчика адресов подключен к второму входу блока управления, а другие выходы являются адресными выходами устройства и соединены с входами перв.ой группы блока фиксации адресов и мультиплексора, выход которого 5 второй групп.

является- информационным выходом устройства и подключен к первому входу блока сравнения, второй вход которого является информационным входом

устройства, а выход соединен с третьим входом блока управления, четвертый и пятый входы которого являются соответственно входами синхронизации и выборки данных устройства, первый

выход блока управления .является управляюищм выходом устройства, а второй и третий выходы подключены к второму и третьему входам блока фиксации адресов, отличающеес я тем, что, с целью повьшгения быстродействия устройства, в него . введеиз блок местного управления и логический блок, причем первый и третий входы блока местного управления подключены соответственно к входам установки и синхронизации устройства, второй вход является входом пуска устройства, четвертый вход соединен с одним выходом счетчика

адреса, пятый вход подключен к второму выходу блока управления, выходы первой и второй групп блока местного управления подключены соответственно к входам второй группы мультиплексора блока фиксации адресов, первый выход соединен с синхровходом счетчика адреса, второй выход подключен к шестому входу блока управления, а третий выход соединен с третьим В2СС1ДОМ Логического блока, входы первой и второй групп которого подключены к выходам блока фиксации адресов, первый и второй входы подключены соответственно к входам синхронизации и установки устройства, четвертый вход соединен с вторым выхо-дом блока управления, а выходы первой и второй групп подключены к входам элементов индикации первой и

0г/с./

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля адресных цепей блоков памяти | 1984 |

|

SU1200347A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для формирования тестовой последовательности | 1986 |

|

SU1529293A1 |

Изобретение относится к.вычислительной технике и может быть исполь.зовано для контроля адресных цепей блоков оперативной памяти. Целью изобретения является повьшение быстродействия устройства. Устройство содержит метчик адреса, мультиплексор, блок сравнения, блок управления, блок фиксации адресов, группы элементов индикации, блок местного управления и логический блок. В устройстве обеспечивается последовательная проверка адресных цепей (АЦ).блоков памяти, причем в качестве данных для проверки i-АЦ используются сигналы i-ro разряда кода адреса поступающего из мультиплексора. Одновременно в блоке фиксации адресов накапливаются результаты анализа адресов в каждом такте считывания теста. Результаты анализа для кадцой АЦ запоминаются до конца проверки, а затем поступают в логический блок, где локализуются отказавшие АЦ. В устройW стве обнаруживаются множественные с константные неисправности и короткие замь1кания меяду АЦ. 5 ил. tc

фаг.

| Колосниковый элемент для сжигания угольной мелочи | 1927 |

|

SU9039A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля адресных цепей блоков памяти | 1984 |

|

SU1200347A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-11-30—Публикация

1985-06-21—Подача