Предлагаемый способ относится к электронной технике и может быть использован в производстве интегральных микросхем, катодно-подогревательных узлов и управляющих электродных структур электровакуумных приборов, в производстве вакуумных интегральных схем и других изделий электронной техники.

Известны способы получения тонкопленочных элементов интегральных схем на диэлектрических подложках, включающие операции нанесения тонкопленочных покрытий, формирование защитного слоя, например, фоторезиста требуемого топологического рисунка и травление тонкопленочных покрытий с целью получения элементов схем. Эти способы предполагают наличие уже готовой диэлектрической подложки.

Ближайшим техническим решением является способ изготовления интегральных микросхем, включающий операции получения диэлектрической пластины-заготовки путем толстослойного анодирования, нанесения на обе стороны пластины сплошных тонкопленочных покрытий, формирование элементов схем травлением диэлектрической пластины и покрытий.

Известный способ заключается в том, что на поверхность диэлектрической пластины, контактирующую в процессе анодирования с электролитом, наносят защитный слой металла, а фотолитографическое нанесение рисунка элементов схем осуществляют на другой стороне поверхности пластины и производят вытравливание отверстий в диэлектрической пластине в местах, не защищенных фоторезистом.

В известном способе отдельные диэлектрические подложки для микросхем получают после вытравливания анодного окисла, стравливания защитного слоя металла и снятия фоторезиста. Окончательное формирование на разных поверхностях подложек тонкопленочных элементов микросхем производится отдельно на каждой подложке методом напыления через маски или с помощью фотолитографических процессов. Это существенно снижает производительность и усложняет технологию изготовления интегральных микросхем.

Целью изобретения является упрощение технологии изготовления интегральных микросхем.

Указанная цель достигается тем, что в местах будущих элементов микросхем на обеих сторонах диэлектрической пластины наносят первый защитный слой фоторезиста, затем обе стороны пластины за исключением мест будущих отверстий в подложках и контуров отдельных схем на одной из сторон пластины покрывают вторым защитным слоем фоторезиста, причем указанные фоторезисты выбирают из условия их избирательного травления в разных электролитах, производят в местах будущих отверстий и контуров схем травление тонкопленочных покрытий и диэлектрической пластины до второго защитного слоя с противоположной стороны пластины, после чего стравливают второй защитный слой, тонкопленочное покрытие в незащищенных первым защитным слоем местах и удаляют первый защитный слой.

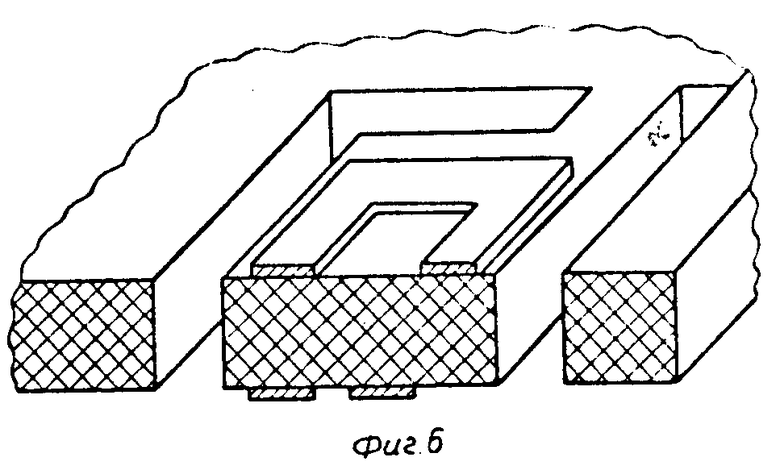

На фиг.1-6 показана последовательность осуществляемых операций.

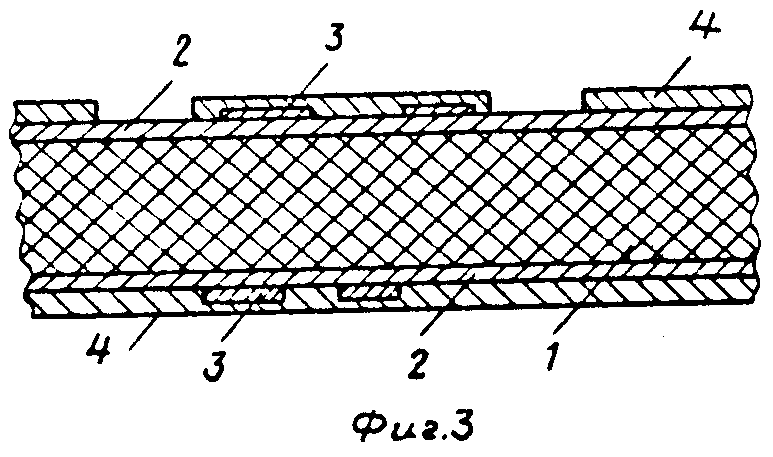

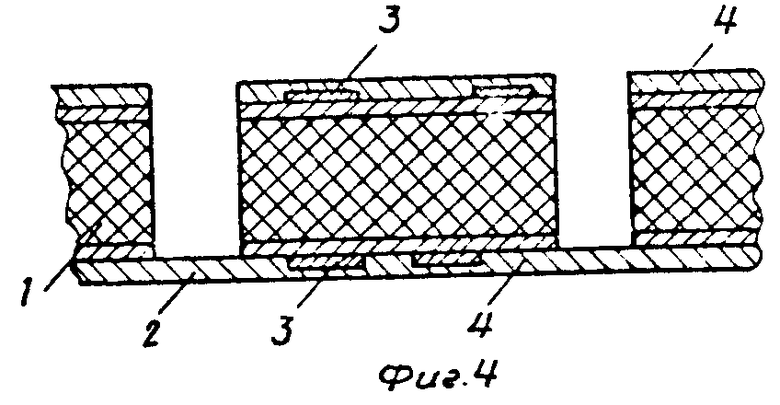

На фиг.1 изображена диэлектрическая пластина-заготовка 1 с тонкопленочными покрытиями 2. В качестве тонкопленочных покрытий могут служить металлы, например, никель молибден, вольфрам, также керметные или эмиссионные покрытия и др. На этих покрытиях (см.фиг.2) методами фотолитографии формируют защитный слой фоторезиста 3 в местах будущих элементов катодно-подогревательных узлов, т.е. подогревателя и оксидного катода. Далее (см.фиг.3) другим защитным слоем фоторезиста 4 покрывают обе стороны пластины за исключением мест будущих отверстий и контуров деталей с одной из сторон пластины. При этом слои фоторезиста 3 и 4 отличаются тем, что используются либо разные фоторезисты, например негативный и позитивный, либо эти слои выполнены из одного фоторезиста, но задублены при различной температуре и могут быть сняты поочередно в различных растворителях. Затем производят стравливание покрытий в незащищенных фоторезистом местах и травление в образовавшихся "окнах" диэлектрической пластины-заготовки до второго защитного слоя (см.фиг.4). Благодаря тому, что анодная окись металла имеет пористое строение, клин травления получается весьма малым (0,03-0,05) и отверстия формируются с высокой точностью.

Так как первый 3 и второй 4 защитные слои фоторезистов различны по своим свойствам, то они растворимы в различных растворителях, что позволяет после вытравливания отверстий снять второй защитный слой 4, не нарушая первого защитного слоя 3. После этого производят стравливание тонкопленочного металлического покрытия (см.фиг.5) с последующим удалением первого защитного слоя 3 и получают из одной диэлектрической пластины-заготовки множество катодно-подогревательных узлов. Окончательный вид катодно-подогревательного узла представлен на фиг.6.

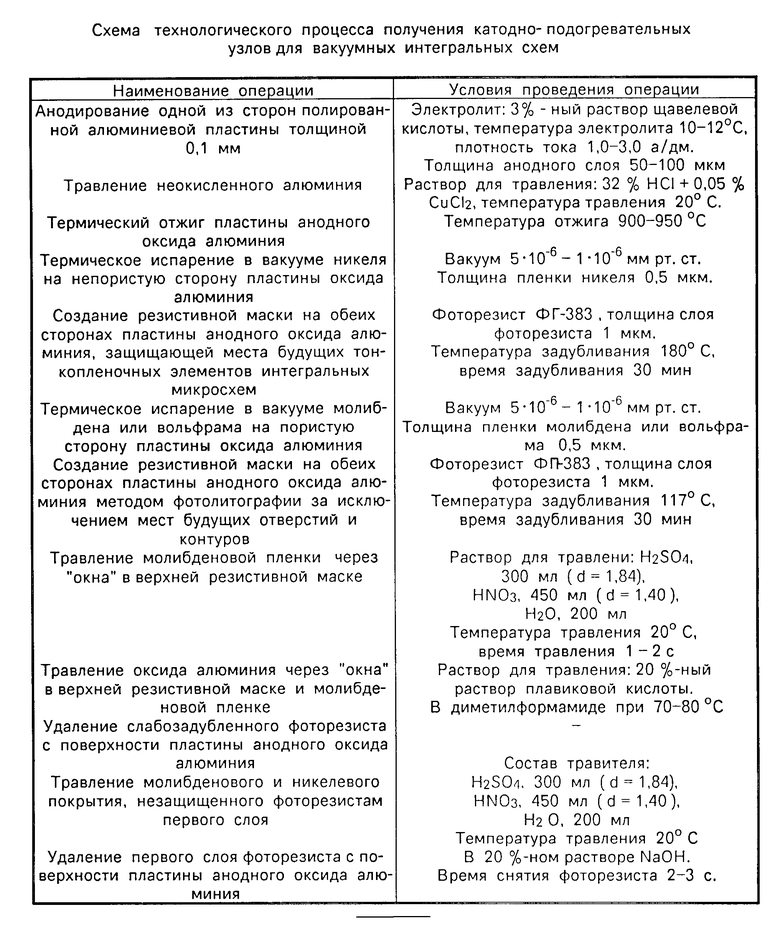

Пример реализации способа приведен в таблице.

Настоящий способ упрощает технологию получения интегральных микросхем, позволяет получать одновременно большое количество узлов, увеличивает производительность при изготовлении интегральных микросхем за счет исключения трудоемких операций получения топологии элементов микросхем индивидуально на каждой подложке методами фотолитографии или масочной технологии, позволяет значительно увеличить процент выхода годных деталей, увеличивается точность изготовления отдельных узлов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОЛУЧЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ДЕТАЛЕЙ С ОТВЕРСТИЯМИ ИЗ АНОДНОЙ ОКИСИ МЕТАЛЛА | 1977 |

|

SU688022A1 |

| СПОСОБ ПОЛУЧЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ПОДЛОЖЕК | 1974 |

|

SU524440A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МАСОК | 1979 |

|

SU784636A1 |

| СПОСОБ ПОЛУЧЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ДЕТАЛЕЙ С ОТВЕРСТИЯМИ В УГЛУБЛЕНИЯХ | 1976 |

|

SU580767A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПЛЕНОЧНОГО ТЕРМОЭЛЕКТРИЧЕСКОГО ПРЕОБРАЗОВАТЕЛЯ | 1984 |

|

SU1200762A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ПОДЛОЖЕК С ОТВЕРСТИЯМИ | 1992 |

|

RU2030136C1 |

| АВТОЭЛЕКТРОННЫЙ МИКРОТРИОД И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2006 |

|

RU2360321C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СИСТЕМЫ ЭЛЕКТРОДОВ ДЛЯ ЭЛЕКТРОВАКУУМНОГО ПРИБОРА | 1974 |

|

SU529772A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ЭЛЕКТРОДНОЙ СТРУКТУРЫ ДЛЯ ВАКУУМНЫХ МИКРОПРИБОРОВ | 1972 |

|

SU470226A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ДЕТАЛЕЙ С ОТВЕРСТИЯМИ | 1972 |

|

SU430763A1 |

СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ, включающий операции получения диэлектрической пластины-заготовки путем толстослойного анодирования, нанесения на обе стороны пластины сплошных тонкопленочных покрытий, формирования элементов схем травлением диэлектрической пластины и покрытий, отличающийся тем, что, с целью упрощения технологии изготовления, в местах будущих элементов микросхем на обе стороны диэлектрической пластины наносят первый защитный слой фоторезиста, затем обе стороны пластины за исключением мест будущих отверстий в подложках и контуров отдельных схем на одной из сторон пластины покрывают вторым защитным слоем фоторезиста, причем указанные фоторезисты выбирают из условия их избирательного травления в разных электролитах, производят в местах будущих отверстий и контуров схем травление тонкопленочных покрытий и диэлектрической пластины до второго защитного слоя с противоположной стороны пластины, после чего стравливают второй защитный слой, тонкопленочное покрытие в незащищенных первым защитным слоем местах и удаляют первый защитный слой.

| Берри Р | |||

| и др | |||

| Тонкопленочная технология | |||

| М.: Энергия, 1972, с.21-45. |

Авторы

Даты

1994-09-15—Публикация

1978-10-16—Подача