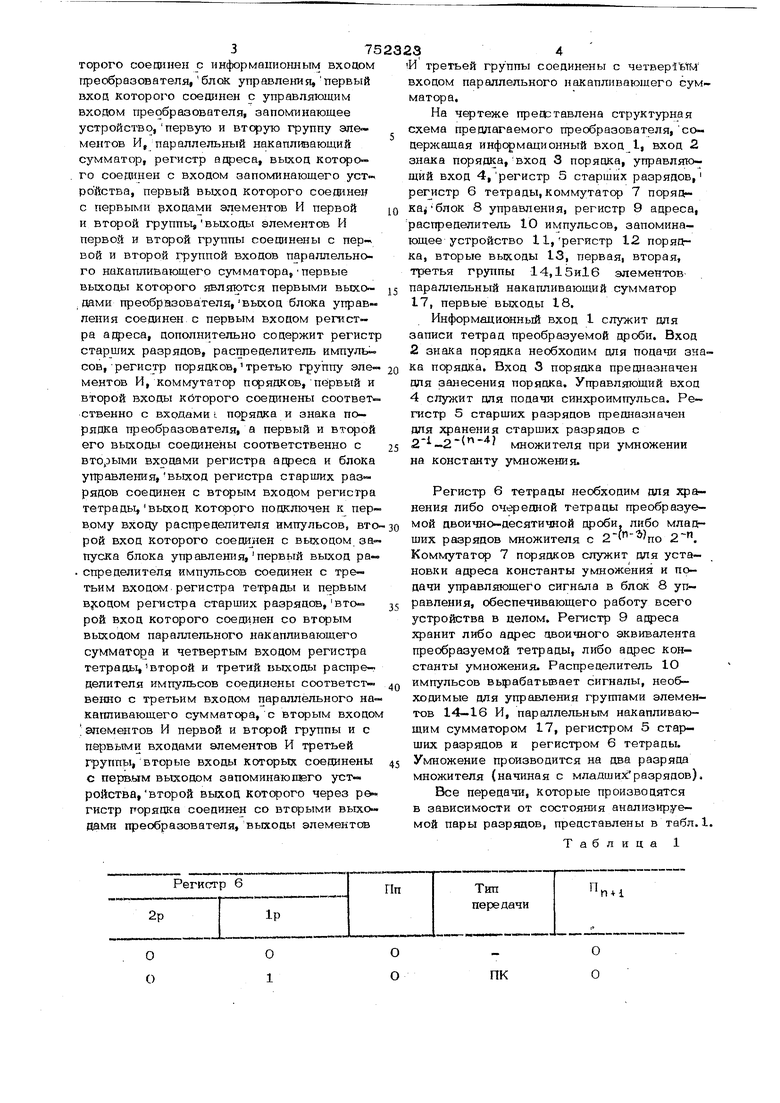

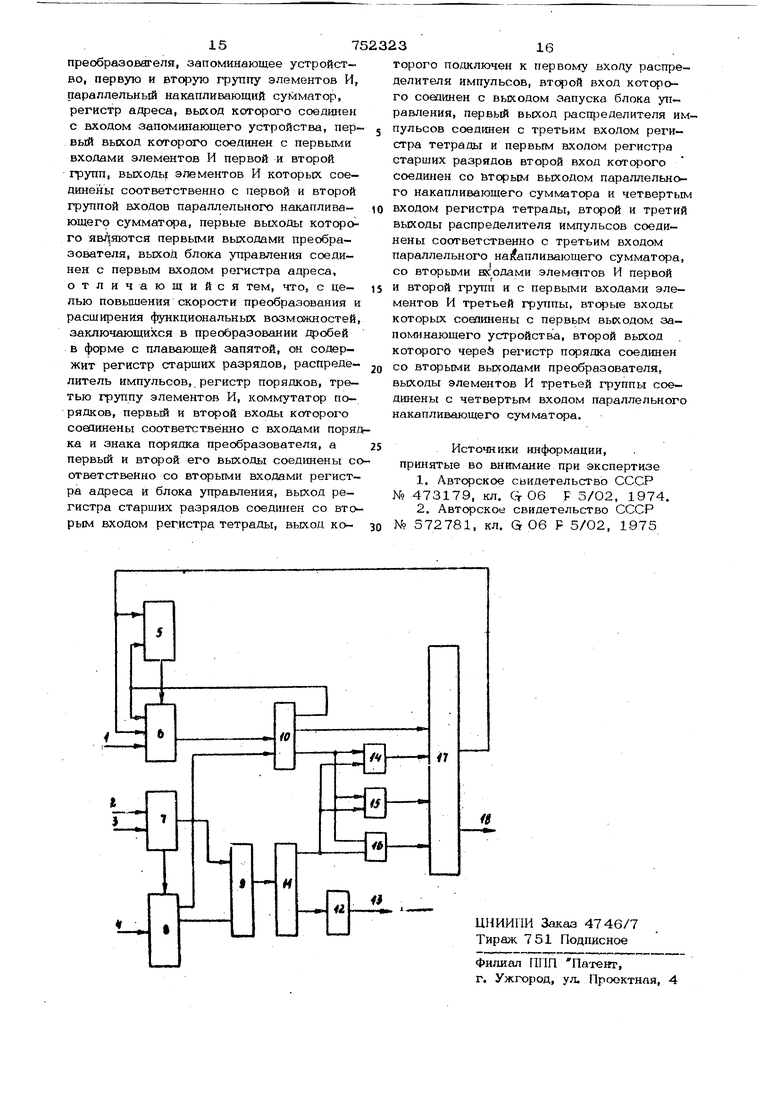

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств щтя преобразования информации. Известен преобразователь цвоично-це- сятичного коца в ороичный код« соаержа- щий блок управления, регистр тетрацы, блок памяти, формирователь двоичных эквивалентов, одноразрядный цвоичный сумматор и регистр сдвига 1 . Недостаток этого преобразователя состоит в низком быстродействии и ограниченности функциональных возможностей, связанной с невозможностью преобразоват числа в с плавающей запятой. Наиболее близким по технической сущности и схемному решению является преобразователь двоично-десятичной дроби в двоичную дробь, содержащий регистр тетрады, первый вход которого соеш1нен с информаиио1д1ым входом преобразователя блок управления, первый вход которого со динен с управляющим входом преобразователя, запоминающее устройство,первую и вторую группу элементе И, параллельный накапливающий сумматор,регистр адреса, выход которого соединен с входом запоминающего устройства, первый выход которого соединен с первыми входами элементов И первой и второй групп, выходы элементов И первой и второйгруппы соединены с первой и второй группой входов параллельного накапливающегл сумматора, первые выходы которого являются первыми выходами преобразсжателя 2J . Недостаток известного пресбразшателя состоит в относительно низком быстродействии и невозможности осуществлять пре- образование чисел в формате с плавающей запятой. Цель изобретения - увеличение скорооти преобразования и расширение функциональных возможностей за счет осуществления преобразования чисел в формате с плавающей запятой. Для этого преобразователь двоичнодесятичной дроби в двоичную дробь, содержащий регистр тетрады,первый вход ко- горого соединен с информацио1шым входом преобразователя, блок управпения, первый вход которого соедннен с управляющим входом гфеобразователя, запоминающее устройство,первую и вторую группу эле- ментов И, параллельный накапливающий сумматор, регистр адреса, выход которого соеданен с входом запоминающего уст-. ройства, первый выход которого соединен с первыми рходами ачементов И первой и второй группы,выходы элементов И первой и второй группы соединены с первой и второй группой входов параллельного накапливающего сумматора,первые выходы которого являются первыми вьосоддми преобразователя,выход блока управ ления соединен с первым входом регистра ащэеса, дополнительно содержит регистр разрядов, распределитель импуль сов,-регистр порядков, третью группу эле- ментов И, коммутатор порядков, п эрвый и второй входы кбторого соединены соответ ственно с входами t порядка и знака по- ряцка преобразователя, а первый и второй его выходы соединены соответственно с вторыми входами регистра адреса и блока управления,выход регистра старших разрядов соедннен с вторым входом регистра тетрады,выход которого подключен к первому входу распределителя импульсов, вто рой вход Которого соединен с выходом за пуска блока управления,первый выход ра. определителя импульсов соединен с третьим входом, регистра тетрады и первым вводом регистра старших разрядов,вто- рой вход Которого соединен со втсрым выходом параллельного накапливающего сумматора и четвертым входом регистра тетрады,второй и третий выходы распределителя импульсов соединены соответственно с третьим входом параллельного накапливающего сумматора, с вторым входом элементов И первой и втсрой группы и с первыми входами элементов И третьей группы, вторые входы которых соединены с первым выходом за поминаю пвго уст ройства,второй выхоц которого через ре гистр порядка соединен со вторыми выхо дамн преобразователя, выходы элементов И третьей группы соединены с чегверГътм входом параллельного накапливающего сумматора. На чертеже представлена структурная схема предлагаемого преобразователя, содержащая инфс мационный вход 1, вход 2 знака порядка, вход 3 порядка, управляющий вход 4,регистр 5 старших разрядов, 6 тетрады, коммутатор 7 порядка блок 8 управления, регистр 9 адреса, распределитель 10 импульсов, запоминающее устройство 11,регистр 12 порядка, вторые выходы 13, первая, вторая, третья группы 14,15и16 элементов параллельный накапливающий сумматор 17, первые выходы 18, Информационный вход 1 служит для записи тетрад преобразуемой дроби. Вход 2 знака порядка необходим для подачи знака порядка. Вход 3 порядка предназначен для занесения порядка. Управляющий вход 4 служит для подачи синхроимпульса. Регистр 5 старших разрядов предназначен для хранения старших разрядов с множителя при умножении на константу умноженияи Регистр 6 тетрады необходим для хранения либо очередной тетрады преобразуемой двоично-десятичной сцзоби, либо младших разрядов множителя с 2. Коммутатф 7 порядков сттужит для установки адреса константы умножения и подачи управляющего сигнала в блок 8 управления, обеспечивающего работу всего устройства в целом. Регистр 9 адреса хранит либо адрес двоичного эквивалента преобразуемой тетрады, либо адрес константы умножени51. Распределитель 1О импульсов вырабатьгоает сигналы, необходимые для управления группами элементов 14-16 И, параллельным накапливающим сумматором 17, регистром 5 старших разрядов и регистром 6 тетрады. Умножение производится на два разряда множителя (начиная с младших разрядов). Все передачи, которые производятся в зависимости от состояния анализируемой пары разрядов, представлены в табл. 1. Таблица 1

Продолжение табл. 1

О

1 1

1

о о 1 1

о 1 о 1

в первом столбце таблицы указьгоают ся возможные состо$шия анализируемой пары разрядов. Второй столбец соцержит перенос Пп от предыдущей анализируемой парьь Третий столбец указьшает тип передачи через группы элементов И 14-16 ПК - прямой код, Л1 - передач прямым коцом со сдвигом на одну позицию в сторону старших разрядов. Информация четвертого столбца указывает на возможный перенос П следующую пару разрядов множителя в зависимости от СОСТО5ШИЯ разрядов анализируемой пары разрядов множителя.

Код 11 можно представить как единицу более старшего разряда и отрицательную единицу в первом разряде. Поэтому при коде II следует вычес.ть множимое из суммы частичных произведений, noiry- ченный результат в сумматоре 17 сдвинуть на два разряда в сторону старших разрядов запомнить, что в следующей паре разрядов нужно учесть дополнительную единицу, что и указано в четвертой, седьмой и восьмой строке четвертого столбца.

Запоминающее устройство 11 хранит К двоичных эквивалентов и 2р + 1 констант умножения и двоичных порядков. Регистр 12 порядка необходим для хранения двоичного порядка искомой мантиссы. Вторые выходы 13 обеспечивают съем двоичного порядка. Первая, вторая, третья группы элементов 14,15,16 И передают поступившую на вход информацию прямым кодом, прямым кодом со сдвигом влево на один разряд, дополнительным кодом соответственно. Параллельный накапливающий сумматор 17 служит для сложения и хранения двоичной информации. Первые выходы 18 О

Л1

о 1

дк

ПК

о о Л1

дк

1 1

обходимы для съема преобразсжанной мантиссьи

Любое число двоично-десятичной системе счисления можно представить в формате с плавающей запятой как

.4Р

,0 2чО4 Х

-4

У2.Ю,, 10

где Т - тетрада двоично-десятичного числа;1

К,

-число разрядов двоично-десятичной дроби;

-Ч

10

-двоичные эквиваленты млaд ишх разрядов преобразуемых тетрад.

Первое выражение в двоичной системе счисления имеет вид

±т

V

2 У(2-10)2 7

где Yj, - искомая двоичная дробь в формате с плавающей запятой; ц,„.. -К,- мантисса искомой двоичной дроби}1

к - константа умножения;

m - ДВОИШЫЙ ПОряДСЖ.

Учигьшая, что тетрада двоично-десятичного числа имеет вид Т Ъ;|дЪ,2.Ь- Ъгде - разряды тетрады нуль или «

единица,

а запоминающее устройство 11 хранит аквнваленты младших двоичных .цов тетрад, сдвинутые на две позиции b сторону старших разрядов, то двои ную дробь { У2-1О 2 можно предстлт вить так

Уамо) ,1 Ь .Ъ ;,,. 2 ( I0-)f

,,2(|0-).

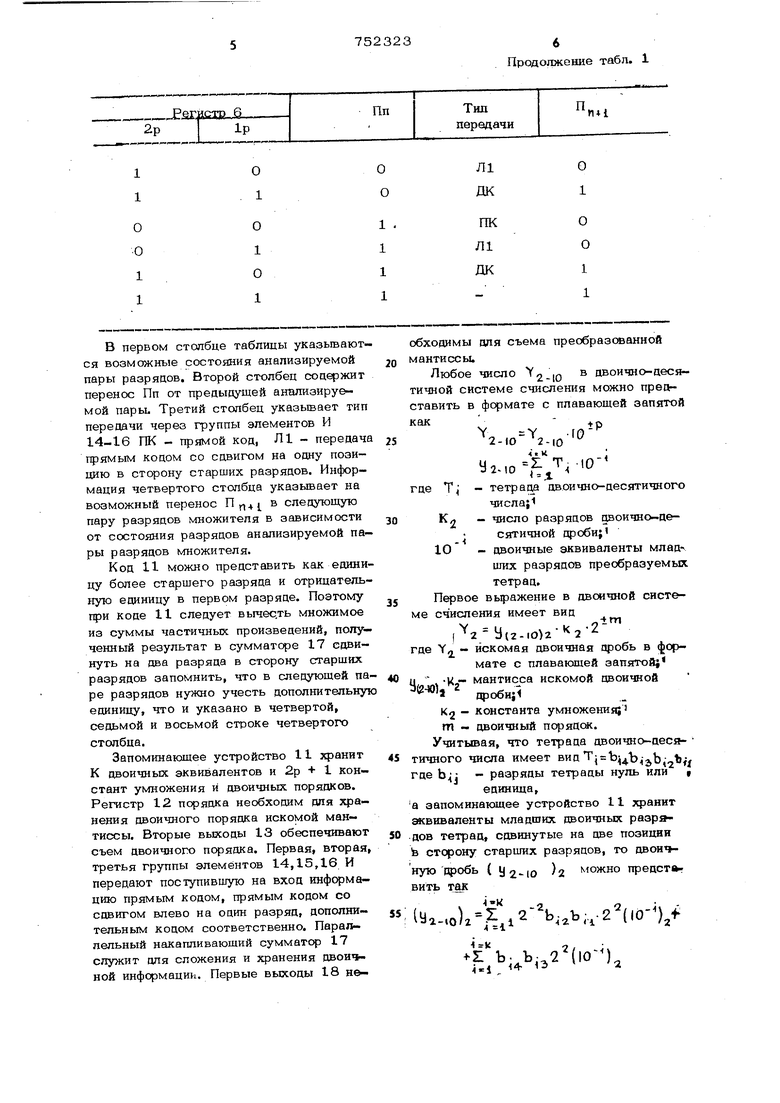

Учитьюая, ( Ъ, есть соответственно функции .и , умножения соответствующих пар разрядов тетрады, на двоичный эквивалент, то второе выражение можно прецстаяить в вице (У2-,о).2 S.- b МУ2-, Из этого следует, что процесс преобразования двоично-десятичной пробн склпдьгоается из двух этапов преобразования мантиссы исходной дроби и умножения полученной двоичной мантиссы на К(жстан ту умножения К с присвоением произведения соответствующего порядка, Этот алгоритм реализуется в предлагаемом преобрпзователе в следующей последовательности. С информационного входа 1 поочередно /поступают тетрады преобразуемого числа, начиная с младщей (старшей), Одновремен но в блок 8 управления поступает по управляющему входу 4 сигнал, запускающий все устройство в целом. Блок 8 управления вырабатьшает сигналы, необходимые для функционирования всего устройства. Синхронно с поступившей тетрадой в регистре 9 адреса устанавливается адрес необходимого двоичного эквивалента, поступающего из запоминающего устройства 11. Допустим, что преобразуется тетра- да двоично-десятичного числаТ. да параллельный накапливающий сум матер 17 хранит результат преобразования млад ших тетрад, В первом такте на регистр 6 тертады поступает тетрада Т . Парал- лельный накапливающий сумматор 17 производит сдвиг на две позиции в сторону старших pai3pHAoB хранящейся в нем ин формадни. Из запоминающего устройства 11 поступает двоичный эквивалент вида 2() ; Во втором такте распределитель 10 импульсов анализирует состояние первого и второго разряда регистра 6 тетрады и вырабатьтает сигналы, управляющие пере- дачей выбранного двоичного эквивалента из запоминающего устройства 11. Суммат(Ур 17 склацьюает результат сдвига с первым частичным произведением Р/ . В третьем такте производится сдвиг на две позиции в стсрону младших разрядов содержимых регистра тетрады 6 и параллельного накапливающего сумматора 17. В четвертом такте производятся анализ третьего и четвертого разрядов тетрады, а из запоминающего устройства 11 в соответствующем коде поступает двоичный эквивалент 2 -{Ю ) на первую, вторую, третью группу элементов 14-16 И, Параллельный накапливающий сумматс 17 складьшает второе частичное произ- ведение {(.ч результатом сдвига, полученным в предыдущем такте. На этом один цикл преобразования заканчивается , После произведенных двух умножений на два разряда, поступает следующая тетрада и осуществляется следующий цикл умножения ее на выбранный двоичный эквивалент из запоминающего устройства 11о Процесс преобразования мантиссы преобразуемой фоби производится К раз, в результате чего на параллельном накапливакзщем сумматоре 17 хранится преобразованная сфобь. В табл. 2 представлено преобразование двоично-десятичной дроби 0,987654. Первый столбец указывает номер цикла, второй столбец - вид операции, третий столбец содержит два знаковых и двадцать один числсжой разряды сумматфа 17. Каждый цикл представлен шестью строками.

Таблица 2

и

752323

В первой строке представлено соцержимое сумматора 19, -сцвинутое на две позиции в сторону старших разрядов. Эта операция обозначена во втором столбце как Л2. Во второй строке представлено первое частичное произведение младших разрядов 1 -той тетрады на соответсгвующий двоичный эквивалент 2 ( Ю )2 -,- Третья строка указывает результат суммирования двух предыдущих строк,- В четвертой строке результат сум мирования сдвинут вправо на две позиции в сторону младших разрядов Пр2. В пятой строке представлен результат умножения двух старших разрядов тетрады на соответствующий двоичный эквивалент 2 (10 )„. Эта операция обозначена во втором столбце как Шестая строка есть результат суммирования четвертой и пятой строк.

После этого в коммутатор 7 порядков поступают знак и десятичный порядок, по которым в регистре 9 афеса устанавливается адрес соответствующей константы

V

Продолжение табл. 2

умножения К2 и производится пуск рас грецелителя 10 импульсов.

Одновременно производится передача двоишьис величин (y2..|Q )2 в регистр 6 тетрады и регистр 5 старших разрядов а из запоминающего устройства 11 выбирается константа К умножения и двоичный порядок, поступающий на регистр порядка 12. Затем производится умножение величины (У2-1О константу ум южения Kg. . Умножение ничем не отличается от умножений; при преобразсжании мантисс двоично-десятичной дроби. После П /2 умножений результат произведения хранится на параллельном накапливающем сумматоре 17.

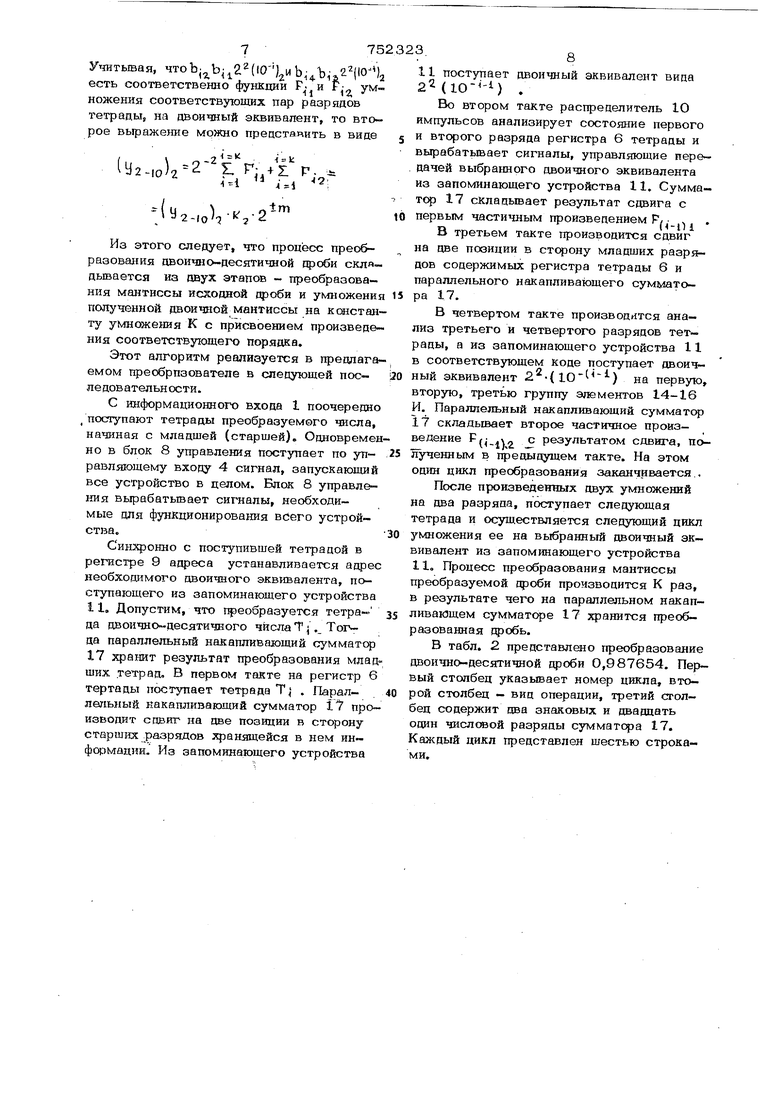

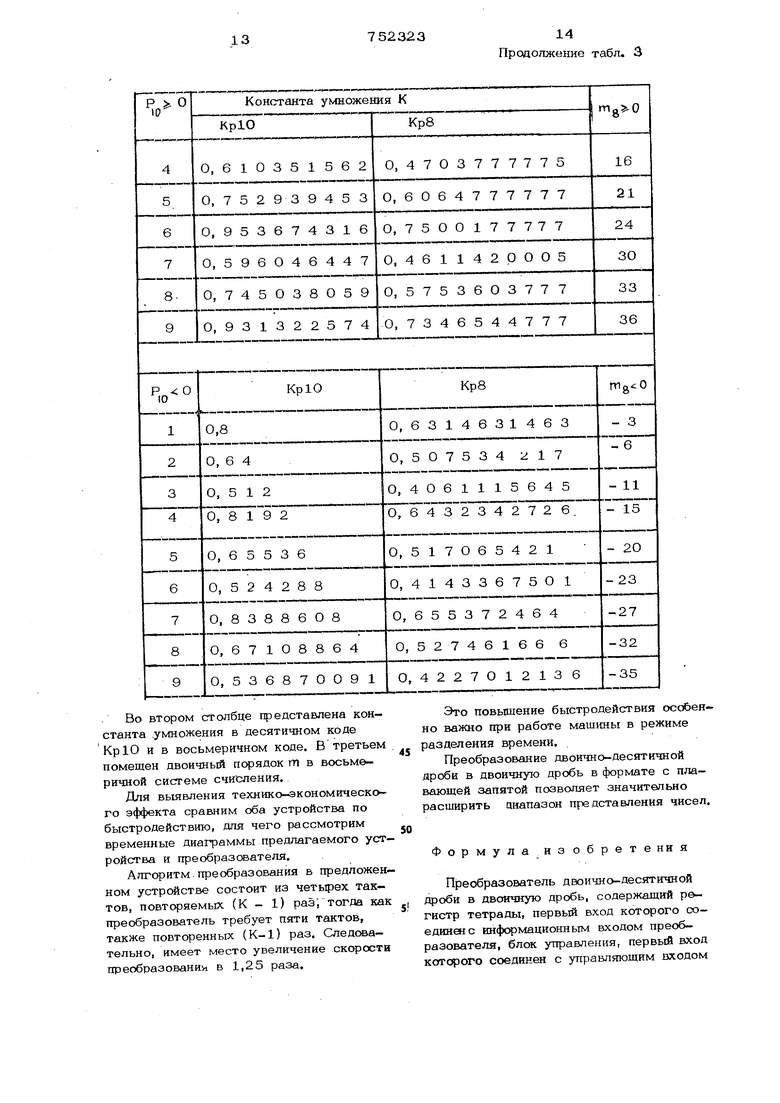

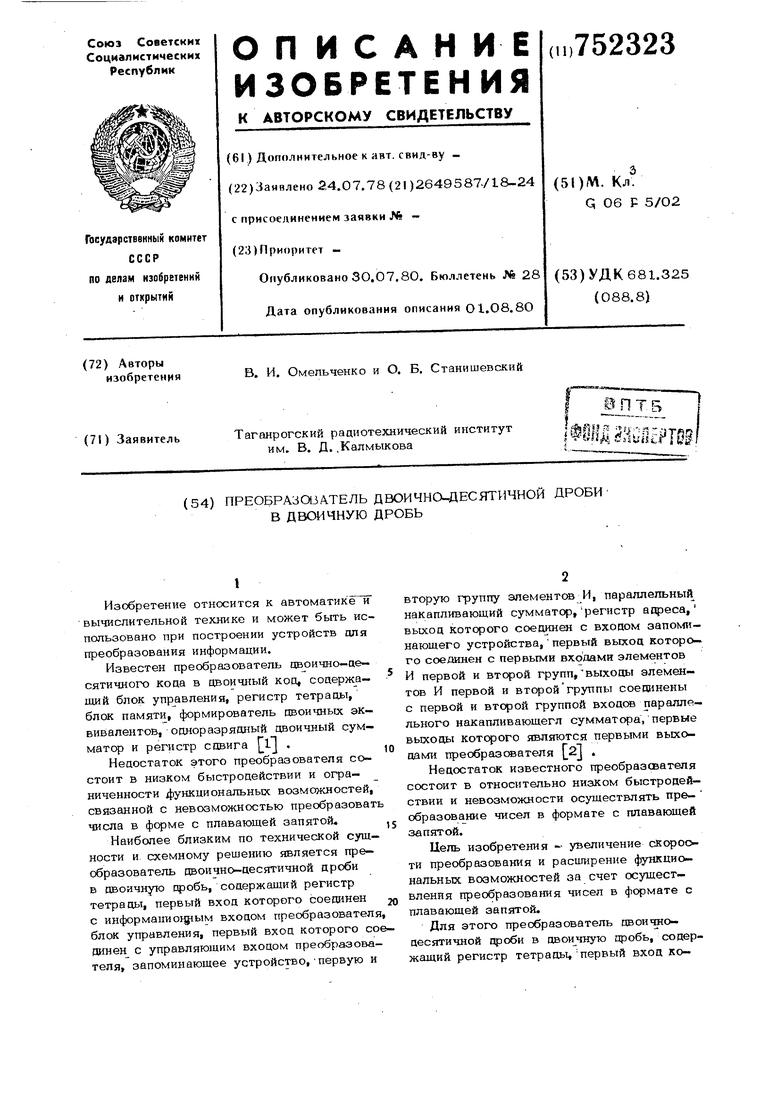

Огсончательный результагснимается с параллелЕзНого двоичного сумматора 17 с помощью вторых выходов 18, а двичный порядок считьшания с регистра 12 порядка и поступает на первые выходы 13, Константы умножения К2 и двоичные порядки m представлены в табл. 3. В первом столбце указьшается десятичный порядок с соответствующим знаком.

Таблица 3: Во втором столбце представлена константа умножения в десятичном коде КрЮ и в восьмеричном коде. В третьем помещен двоичньй порядок m в восьмеричной системе счисления. Для выявления технико-экономического эффекта сравним оба устройства по быстродействию, для чего рассмотрим временные диаграммы предлагаемого устройства и преобразователя. Алгоритм.преобразования в предложенном устройстве состоит из четырех тактов, повторяемых (К - 1) раз; тогда как j, преобразователь требует пяти тактов, также повторенных (К-1) раз. Следовательно, имеет место увеличение скорости преобразование, в 1,25 раза. Это повышение быстродействия особенно важно при работе машины в режиме разделения времени, Преобразование двоично-десятичной дроби в двоичную дробь в формате с плавающей запятой позволяет значительно расширить диапазон представления чисел. Формула из обрете нй я Преобразователь двоично-десятичной дроби в двоичную дробь, содержащий регистр тетрады, первый вход которого соединен с информационным входом преобразователя, блок управления, первый вход которого соединен с управляющим входом преобразователя, запоминающее устройство, первую и вторую группу элементов И, параллельный накапливающий сумматор, регистр адреса, выход которого соедш ен с входом запоминающего устройства, первый выход которого соединен с первыми входами элементов И первой и второй групп, выходы элементов И которых соединены соответственно с первой к второй группой входов параллельного накапливающего сумматора, первые выходы которого являются первыми выходами преобразователя, выход блока управления соединен с первым входом регистра адреса, отличающийся тем, что, с целью повышения скорости преобразования и расширения функциональных возможностей, заключающихся в преобразовании дробей в форме с плавающей запятой, он содержит регистр старших разрядов, распределитель импульсов,, регистр порядков, третью группу элементов И, коммутатор порядков, первый и второй входы которого соединены соответственно с входами порядка и знака порядка преобразователя, а первьй и второй его вькоды соединены соответственно со вторыми входами регистра адреса и блока управления, выход регистра старших разрядов соединен со вторым входом регистра тетрады, вькод ко1 } 75

11

18 23 торого подключен к первому входу распределителя импульсов, второй вход которого соеаинен с выходом запуска блока уп равления, первый выход распределителя им. пульсов соединен с третьим входом регистра тетрады и первым входом регистра старших разрядов второй вход которого соединен со вторым выходом параллельного накапливающего сумматора и четвертым входом регистра тетрады, второй и третий выходы распределителя импульсов соединены соответственно с третьим входом параллельного накапливающего сумматора, со вторыми вх одами элемштов И первой и второй групп и с первыми входами элементов И третьей группы, вторые входы которых соединены с первьп выходом запоминающего устройства, второй выход которого черей регистр порядка соединен со вторыми выходами преобразователя, выходы элементов И третьей группы соединены с четвертым входом параллельного накапливающего сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №473179, кл. Ст 06 F 5/02, 1974. 2.Авторское свидетельство СССР № 572781, кл. G Об F 5/02, 1975

Авторы

Даты

1980-07-30—Публикация

1978-07-24—Подача