1

Изобретение относится к области запоминающих устройств.

Одно из известных устройств для контроля оперативной памяти построено на специально разработанных морфических элементах, выходы которых имеют три логических состояния, причем область применения этих специальных элементов ограничена 1. В случае обнаружения одиночной ошибки выполняется ее коррекция. Недостатком этого устройства является невысокая скорость работы.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство для контроля оперативной памяти, содержащее генератор кода Хэмминга, блок коррекции контрольного кода, дешифратор ошибок, вход которого подключен к выходу блока обнаружения неисправностей, выходной регистр и входной регистр, входы которого подключены к первому и второму входам устройства 2. Недостатками этого устройства являются отсутствие сквозного контроля работы оборудования устройства, приводящее

при его неисправности к искажению информации, и наличие избыточного оборудования. Указанные недостатки снижают надежность устройства и приводят к большим аппаратурным затратам.

Целью настоящего изобретения является повышение надежности и упрощение устройства. Это достигается тем, что устройство содержит блок коррекции входной информации, селектор, регистр контрольного кода, регистр кода Хэмминга, блок сравнения кода Хэммин™ га и контрольный блок сравнения, первый вход которого соединен с выходом блока обнаружения неисправностей, второй вход - с выходом блока коррекции контрольного

кода и с первым входом выходного регистра, третий вход - с выходом регистра кода Хэмминга, первым входом блока обнаружения неисправностей и первым входом блока сравнения кода Хэмминга, а четвертый

вход - с выходом блока коррекции входной информации и вторым входом выходного регистра, к третьему входу которого подключен выход генератора кода Хэмминга, входы регистра кода Хэмминга и регистра

кинтр ;ьног() КОЛЯ, втог)ои н;.0;1 олокг. cjsaEспавнгни : пи-кчлч емой кчформуднн, вг/ппм :5:чол, ;гторО1( соем. г: выХп;,пу ;;и-и-: :: s;;-:ii ;:г:г; г;ГГ.(Г1 р Д ; Ь:ХОД

Ku-;n ., 1-. i:u,j,K.;:LOien ::) :vru 7):ni iii-H неигправ1,пт:д1. ;-; :: i,););jM;M.:/;)Hi-;:iiii Еых()д . i ouoNy nxoAV rc.iCui opn, чс гдеитому кх.оду вьнодного i eri crpii, гервому вхсзду блока i oppeKКим ччод, 1Н(Ьормнцид, второй в;;од кодо5ок и пспвгдм вхс),д)Д- о.кжя Д)ррскции KOii р(. ;д),,;а, BTCiijoii мход KfsTopoTi додкдочси к ) т)ег- С-д;а к()нтр(),;1Ь11Ог;)

ратора кода Хзммингя, s втооой длод, - д .с иервым лодл;. ДТРОЙСТ ;У, 1)л;;д у-дгройстна гюд|.;ючрн к -rpCTbCNiv иход;/ д; д:1b /i{i п;.Г;;с г,; КГ ;-(;i) ВлОлу д,сп и Ьп; ncncivi г;- записыиаемой чафор.тании.

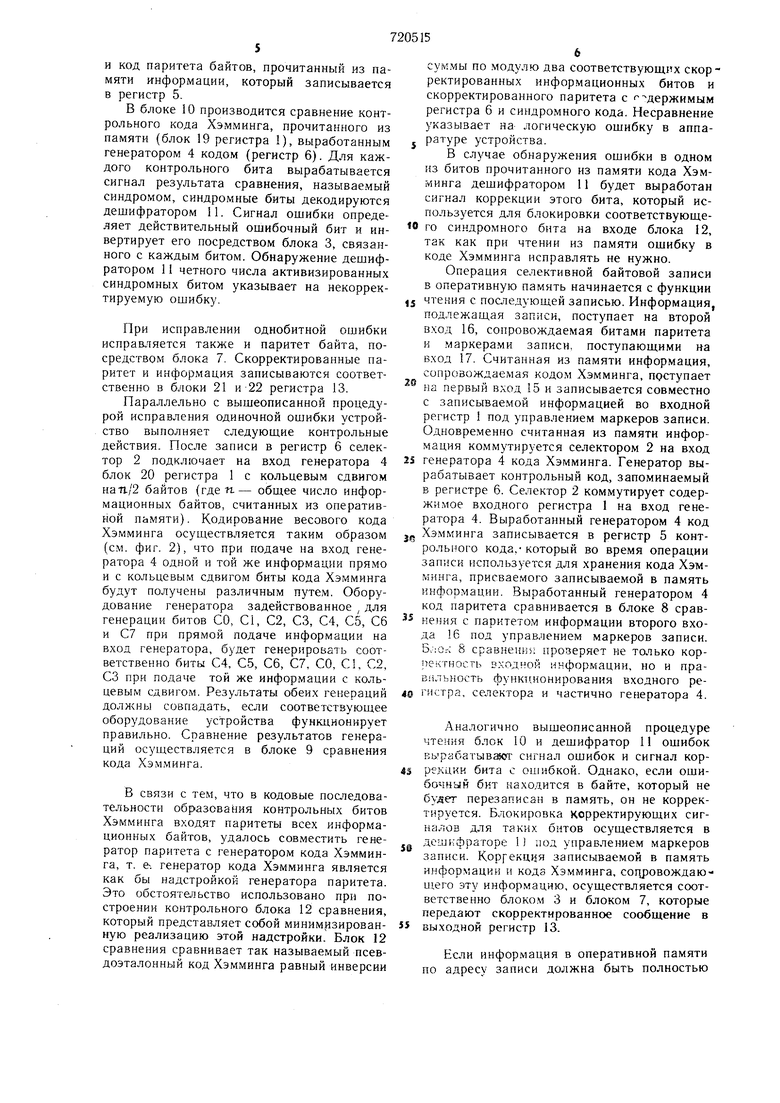

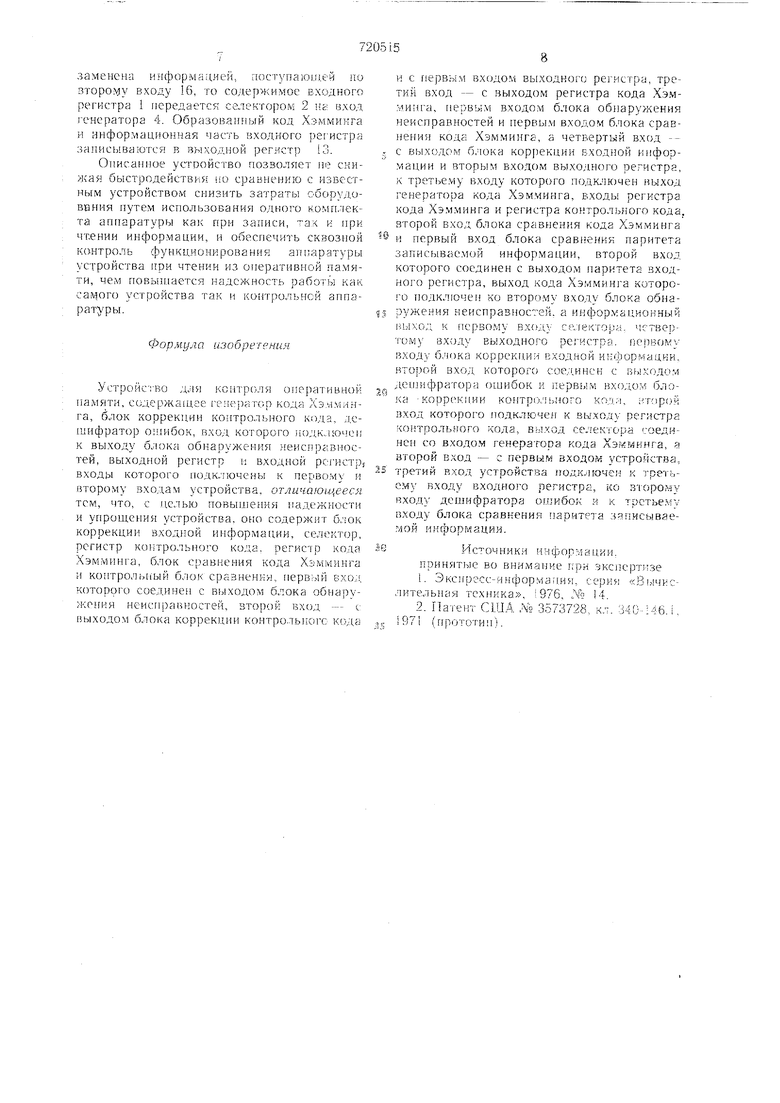

на фиг. 2 -- матргП й ч(я;;сЬ;;иирог;аи :ого вгсового кол,;; Хчиминга; на Фиг. 3 --- 4атр1-д и,а кояГ) блол:а ciUiBHeisHH.

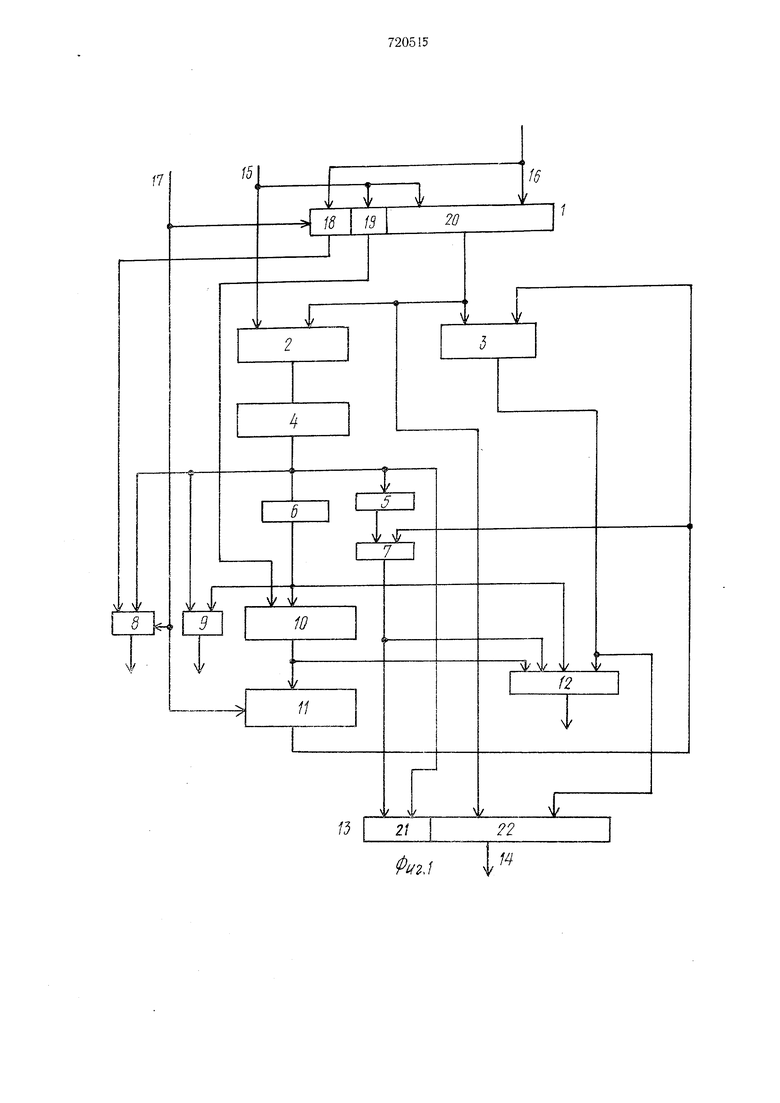

УстройсПзс (елд оэкг. ; 1 содержит входкой pesHCTp i. селск1-ор 2, блок 3 хоррекцим входной инсродмации, генепатор t Ko.n,:i , рез ис М h )(л/1Ь}Н Ги куда, регистр fc хода X:iM 5Hnra. блок 7 коррекции ко:дгрсль- К)го кодй, 5.;к)( ; срявнеипя парите;;: зааисьпаемой ид ± 0р11;йд:-и-,. 5..: 9 соэвнрн;;: ..а Хэммкнга, (; обг апуже.гин еяспрад

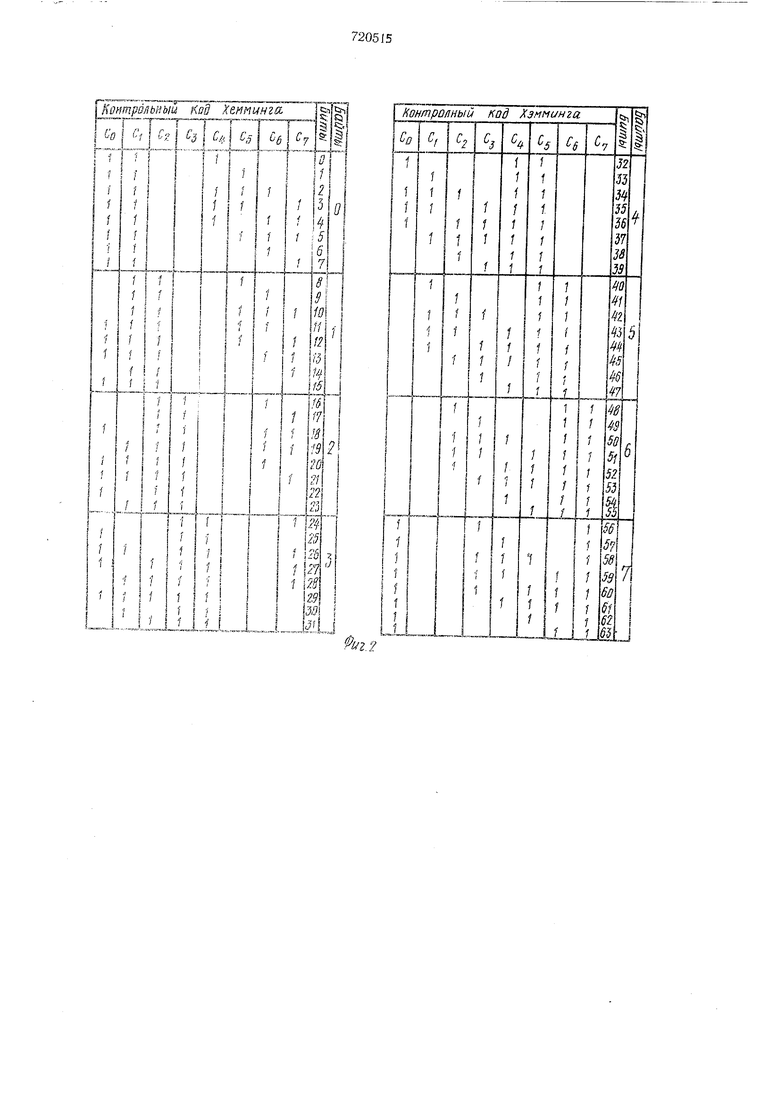

второй 16 и 7 влодгд. И гоотиедствк/ с хранимоы iiuj;opMTi: i K оегисдр I г аздс1 etiepaTOp --1 кода /.эммиига состд;--;- из элементов, рсалчаукпцих функцию сдож: 1и; по модулю два. 64 днформацгоннь х битов генеоад р вырасатывае 8 cvivrvi г;о

МОДуЛ С два согласие: ф:1Г 2 - СС)--С;,

именуемых кодох лэ ии:нгя. Б,:1ок И) п|)ед.ставляст собой К. {К --- число сиглволов кода Хэмминга) двухвходовых эдементов, реализующих ,и:о сложении яо доду.лю два симзо.лоЕ ко.ца Хэмимггга, продктадиых КЗ памяти, с д;ответстчу Jijj,H:vii-; сккс.одам;; кода Хзммищ-а, выра)атаннх1М1-1 гег:ера;0 ром 4 кода Хдммн ч-а.

Б.ТОК 3 состоит из (уДО:зьх эле1-;;еД 1ов, реали 3 у:а;.ддх сдожснд : г:о модулю два.

Каждый элемент скла.динает ин{:|зормационный бит с соответгтпудицим сигиадохд выработаи ;ыгл дешифратором li, указываю цим на oiiixoxy ii зтом оате.

Бдок 7 состоит из :,зухвхо.довых элемсп -той сдожели; по молулю два, на один вход которых заводится содержимое соответствую:и.сго разряда ре йстра 5 контрольного кода, а пу второй ВХО.Д -- (Д1гнал OHJKOKH н информации этого разряда, выработанный .п,еп5и4|Дат()ром 1 i.

Во время операции «чтение регистр Ь контрольного кода хранит пзритеты байтов информационных CHMBO..:IOB сообиления, а во время операции селективной записи код, Хзмминга записываемой в память икux)piv,aii.HH.

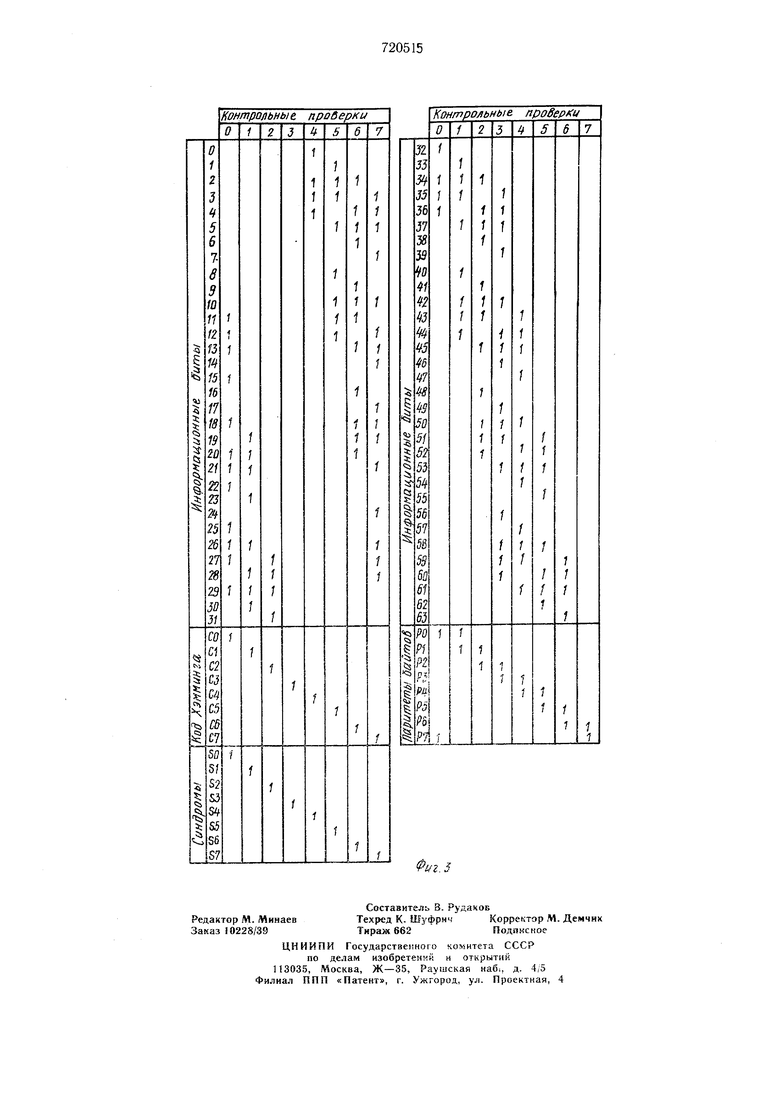

Первый вход блока i2 сравнения соединен с ВЫХО.ДОМ бдока 10 обнаружения Е еисгтрйвностей, втооой вхо.п. - с шдходом блока 7 коррекции контродьног;з ;хода и с перБход, f: вь:ход.оч регд.гфа G ксд.а Хэммидга 1Х/рвыд входом блока И; об;;аруження не(.{(мтрянностей и хервьм входом бдока 9 сравдения кода ХэхиДиихд, а зетсе:)тый вход с вь ходом п/юка 3 коррекции входной кд1рормации и ;торЫ1... вхо.до1; .Horfj регистра i 3, к 1ретьему входу ;(оторогс юд,1-:.ли)пен вь:ход генератора 4 код,а .хзиминга. Бходы региег{)а В кода Хзммиига и pei-истра п контрольного :ода, второй вход бдока 9 сравдсния кода Хэх;мингк м асрввж вход, блока 8 еравиения дари-1ета заиисынаемой 1Д(:)Ормации, второй в;-у)д хоторогг соеднпен с зь;ходо ; каритета вх( регистра. Kozia Кэимднга которого подк-тюче: ко

исдоавноегей, а информа иоддвй выход к керволп ВХОД , сслект.ра v. 1к-твертс му ;;ходу )го регис:ра (3, иериому вх(;ду бдока 3 1;оррек:1ии ьхо.дной vnitpopMariH -;, 1-гпгкгй вход KOioporo соддхвен . зых;х5Ог дешифратора 1 S о)нипок и дервьп1 входов

рой вход которого до. хдычех к Ы7:ход рсгдс -ра G коитродьного кода, вкхсх. с-д ектора 2 соединен со входол- генератопа 4 кода хчлминга, а второй вход - - с первьил входом ус ройства 15, крстий вход :7 устройства гкхчк.лочен к третьему входу входного реi нслрн S, ко олоролгу входу д.ех1ифсатора II сшибок и к третье1ду входу бдока и сравне дия иаритета записв ваемой икбор мадии. Устройство работает следуклии;-.; .х R О ератив1и Й Т1Ял1Яти хр аится /дфорiviaBl-ivi СОХМ;х.ДНО с КОгГГРОДЬХо,: КО.Длх Хэг,1::/iv,Hra. Bf; врекя оиеруци-; хчгеник;; из viaмити инфоомад.;{И с с;зтровождак)ш,км ее ходом Хзмминта оссдиает иа 1ервый вход to и записввается во входной регист;} caj негетвенно в блох:-; д5 i 2() регистра i. С)д;1овремеи;о считанная ияфорл ация перех.аетсх cej.iexTopoM 2 з:; гоод ге1:сратода 4 :дхда Хэкминга. Геператод 4 вырабатывает

и код паритета байтов, прочитанный из памяти информации, который записывается в регистр 5.

В блоке 10 производится сравнение контрольного кода Хэмминга, прочитанного из памяти (блок 19 регистра 1), выработанным генератором 4 кодом (регистр 6). Для каждого контрольного бита вырабатывается сигнал результата сравнения, называемый синдромом, синдромные биты декодируются дешифратором 11. Сигнал ошибки определяет действительный ошибочный бит и инвертирует его посредством блока 3, связанного с каждым битом. Обнаружение дешифратором 11 четного числа активизированных синдромных битом указывает на некорректируемую ошибку.

При исправлении однобитной ошибки исправляется также и паритет байта, посредством блока 7. Скорректированные паритет и информация записываются соответственно в блоки 21 и-22 регистра 13.

Параллельно с вышеописанной процедурой исправления одиночной ошибки устройство выполняет следующие контрольные действия. После записи в регистр 6 селектор 2 подключает на вход генератора 4 блок 20 регистра 1 с кольцевым сдвигом наи/2 байтов (где ti- обшее число информационных байтов, считанных из оперативной памяти). Кодирование весового кода Хэмминга осушествляется таким образом (с.м. фиг. 2), что при подаче на вход генератора 4 одной и той же информации прямо и с кольцевым сдвигом биты кода Хэмминга будут получены различным путем. Оборудование генератора задействованное , для генерации битов СО, С1, С2, СЗ, С4, С5, С6 и С7 при прямой подаче информации на вход генератора, будет генерировать соответственно биты С4, С5, С6, С7, СО, С, С2, СЗ при подаче той же информации с кольцевым сдвиго.м. Результаты обеих генераций должны совпадать, если соответствующее оборудование устройства функционирует правильно. Сравнение результатов генераций осуществляется в блоке 9 сравнения кода Хэмминга.

В связи с тем, что в кодовые последовательности образования контрольных битов Хэмминга входят паритеты всех информационных байтов, удалось совместить генератор паритета с генератором кода Хэмминга, т. е-, генератор кода Хэмминга является как бы надстройкой генератора паритета. Это обстоятельство использовано при построении контрольного блока 12 сравнения, который представляет собой минимизированную реализацию этой надстройки. Блок 12 сравнения сравнивает так называемый псевдоэталонный код Хэмминга равный инверсии

сум.мы по модулю два соответствующих скорректированных инфор.мационных битов и скорректированного паритета с держимым регистра б и синдромного кода. Несравнение указывает на логическую ошибку в аппаратуре устройства.

В случае обнаружения ошибки в одном из битов прочитанного из памяти кода Хэмминга дешифратором 11 будет выработан сигнал коррекции этого бита, который используется для блокировки соответствующео го синдромного бита на входе блока 12, так как при чтении из памяти ошибку в коде Хэмминга исправлять не нужно.

Операция селективной байтовой записи в оперативную память начинается с функции чтения с последующей записью. Информация, подлежащая за1п1си, поступает на второй вход 16, сопровождаемая битами паритета и маркерами записи, поступающими на вход 17. Считанная из памяти информация, сопровождаемая кодом Хэмминга, поступает

на первый вход ID и записывается совместно с записываемой информацией во входной регистр 1 под управлением маркеров записи. Одновре.менно считанная из памяти информация коммутируется селектором 2 на вход

5 генератора 4 кода Хэмминга. Генератор вырабатывает контрольный код, запоминаемый в регистре 6. Селектор 2 коммутирует содержимое входного регистра 1 на вход генератора 4. Выработанный генератором 4 код

J5 Хэмминга записывается в регистр 5 контрольного кода,- который во время операции записи используется для хранения кода Хэмминга, присваемого записываемой в память информации. Выработанный генератором 4 код паритета сравнивается в блоке 8 сравнения с паритетом информации второго входа 16 под управлением маркеров записи. Б.гОг; 8 сравнении проверяет не только корректность в.ходной информации, но и праВ льность функтгионирования входного регистра, селектора и частично генератора 4.

Аналогично вышеописанной процедуре чтения блок 10 и дещифратор 11 ошибок вырабатывают сигнал ощибок и сигнал корS рехцкн бита с ошибкой. Однако, если ошибочный бит находится в байте, который не будет перезаписан в память, он не корректируется. Блокировка корректирующих сигналов для таких битов осуществляется в дешифраторе 1) под управлением маркеров записи. Коррекция записываемой в память информации и кодз Хэмминга, согфовождающего эту информацию, осуществляется соответственно блоком 3 и блоком 7, которые передают скорректированное сообщение в

выходной регистр 13.

Если информация в оперативной памяти по адресу записи должна быть полностью

заменена информацией, лоступаюихей по

BTOpOiVjV входу 16, то СОДеТ)ЖИМОС Е:ХОДНОГО

регистра 1 передается селектором 2 на вход ге-нератора 4. Образовапр ый код Хэммикга и информационная часть входного Регистра записываются в выходной регистр 3.

OiiHcaFinoe устройство позволяет не быстродействия liO сравнению с известн,м устройством снизить затраты оборудоввния нутем иснользования одного и.омплек та аппаратуры как при записи, и при чт.ении информации, и опеснечить сквозной контроль функционировання аггнаратуры устройства при чтении из онератнвной памяти, чем повышается надежность работы Kai салюго устройства так и коЕггрольнсй анпаратуры.

Формула изобретения

стройство для контроля оперативной намяти, содержащее генератор кода Хэл1минга, блок коррекции контрольного кода, дешифратор ошибок, вход которого ио,ч,ключе1 к выходу блока обнаружения неисправностей, выходной регистр и входной регистр} входы которого нодк.лючены к первому и второму входам устройства, отличаю1цееся тем, что, с целью повьннения надежности и упрощения устройства, оно содержит блок коррекции информации, селектор, регистр контрольного кода, регистр кода Хэмминга, блок сравнения кода Хэммипга и контрольный блок сразненки, первый вхо.л, которого соединен с выходом блока обнаруже гия неисправностей, второй вход -- с (ыходом блока коррекции контролы1С ГС код,а

и с первым входом выходного регистра, третий вход - с выходом регистра кода Хэмминга, ие;;Бым входом блока обнаружения неисправностей и первым входом блока сравнения кода Хэмминге, а четвертый вход -с гзыходом блока коррекции информации и вторым входом выходного регистра, к третьему входу которого подключен выход генератора кода Хэмминга, входы регистра кода Хэмминга и регистра контрольного кода, второй вход блока сравнения кода Хэмминга

и первый вход блока сравнения паритета записываемой информации, второй вход которого соединен с выходом паритета входного регистра, выход кода Хэмминга которого подключен ко второму ВХОДУ блока обнаружекия неиспразносгей, а информационный выход к ficpBOMy сатектора, четвертому выходного региетра, негшоку входу блока коррекции входной и};формации, второй вход которого соединен с выходом де1нифратора ошибок и первь м входом блока -коррекции KOirrpiJ.lhHOrO КОДМ, ;-:ТОрОЙ

вход которого подкл.ючен к выходу регис-тра ко - трольного кода, выход селектора соединен со входом генератора кода Хэг минга, а второй вход - с первы.й входом устройства, третий вход устройства подключен к третьему входу входного регистра, ко втсфому входу дешифратора ошибок и к третье,му входу блока сравнения каритета записы ваемой икгроркации.

Иг

Принятые во внимание при зкенерткзе

1,Экспресс-информаг1ия, серия лительная техника, 1976, Mb J4.

2.Патент США ,N« 3573728, кл, 3 1971 (нрототин).

Kot anpoiibHbm Код ,;

ГТттГ j- p-- -y-j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1978 |

|

SU752502A1 |

| Устройство для записи и воспроизведения информации из блоков оперативной памяти с коррекцией ошибки | 1977 |

|

SU974410A1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU940242A1 |

| Устройство для обнаружения и коррекции одиночных ошибок | 1982 |

|

SU1075313A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1985 |

|

SU1277214A1 |

Авторы

Даты

1980-03-05—Публикация

1977-09-01—Подача