«1

Изобретение относится к вычислительной технике и может бь1ть использовано при разработке блоков памяти микроэвм с коррекцией ошибок.

Цель изобретения - повьшение на- дежности устройства.

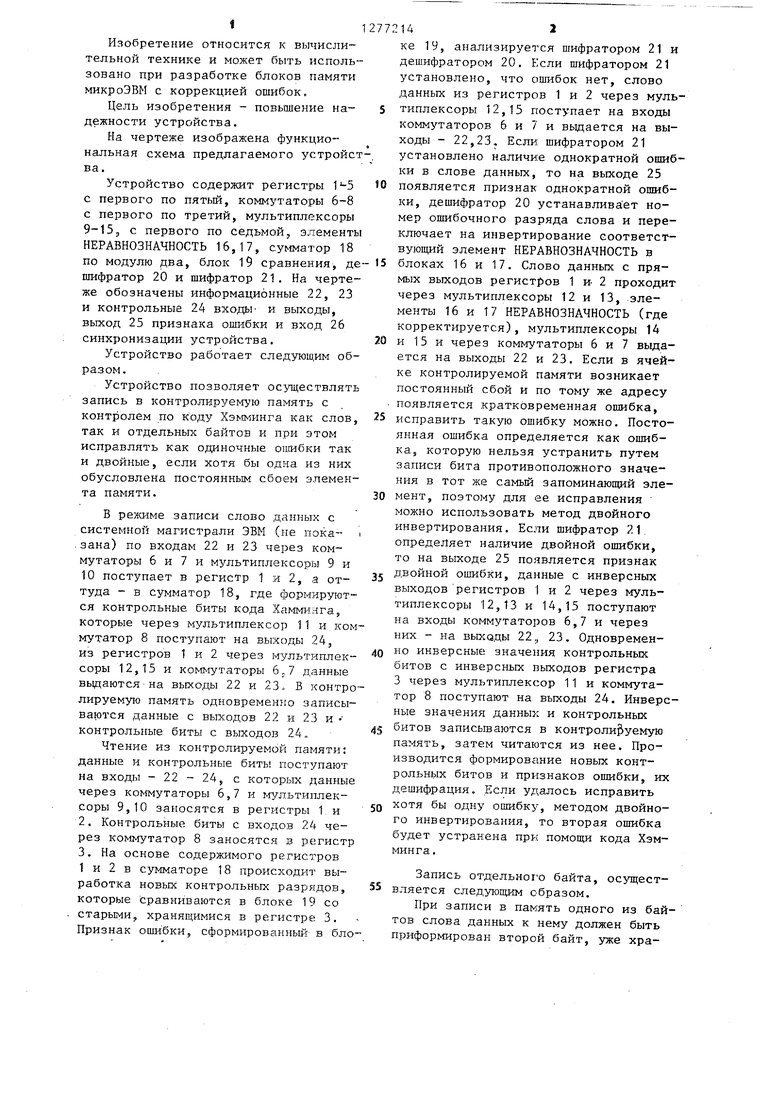

На чертеже изображена функциональная схема предлагаемого устройст на.

Устройство содержит регистры 1-5 с первого по пятый, коммутаторы 6-8 с первого по третий, мультиплексоры 9-15р с первого по седьмой, элементы НЕРАВНОЗНАЧНОСТЬ 16,17, сумматор 18 по модулю два, блок 19 сравнения, де шифратор 20 и шифратор 21, На чертеже обозначены информационные 22, 23 и контрольные 24 входы и выходы, выход 25 признака ошибки и вход 26 синхронизации устройства,

Устройство работает следуюш,им образом.

Устройство позволяет ос уществлять запись в контролируемую память с контролем по коду Хэмминга как слов, так и отдельных байтов и при этом исправлять как одиночные оигибки так и двойные, если хотя бы одна из них обусловлена постоянным сбоем элемента памяти.

В режиме записи слово данных с системной магистрали ЭВМ (не пока- .зана) по входам 22 и 23 через коммутаторы 6 и 7 и мультиплексоры 9 и 10 поступает в регистр 1 и 2, а от- туда - в сумматор 18, где формируются контрольньге биты кода Хамминга, которые через мультиплексор 11 и коммутатор 8 поступают на выходы 24, из регистров 1 и 2 через мультиплек- соры 12,15 и коммутаторы 6.. 7 данные выдаются на выходы 22 и 23. В контролируемую память одновременно записываются данные с выходов 22 и 23 и контрольные биты с выходов 24„

Чтение из контролируемой памяти: данные и контрольные бить5 поступают на входы - 22 - 24, с которых данные через кo fмyтaтopы 6,7 и 1 7льтиплек- соры 9,10 заносятся в регистры 1 и

2,Контрольные биты с входов 24 через коммутатор 8 заносятся з регистр

3.На основе содержимого регистров

1 и 2 в сумматоре 18 происходит выработка новых контрольных разрядов, которые сравниваются в блоке 19 со старыми, хранящимися в регистре 3. Признак ошибки, сформированный в бло142

ке 19, анализируется шифратором 21 и дешифратором 20, Если шифратором 21 установлено, что ошибок нет, слово данных из регистров 1 и 2 через мультиплексоры 12,15 поступает на входы коммутаторов 6 и 7 и вьщается на выходы - 22,23« Если шифратором 21 установлено наличие однократной ошибки в слове данных, то на выходе 25 появляется признак однократной ошибки, дешифратор 20 устанавливает номер ошибочного разряда слова и переключает на инвертирование соответствующий элемент НЕРАВНОЗНАЧНОСТЬ в блоках 16 и 17, Слово данных с прямых выходов регистров 1 и. 2 проходит через мультиплексоры 12 и 13, элементы 16 и 17 НЕРАВНОЗНАЧНОСТЬ (где корректируется), мультиплексоры 14 и 15 и через коммутаторы 6 и 7 выдается на выходы 22 и 23, Если в ячейке контролируемой памяти возникает постоянный сбой и по тому же адресу появляется кратковременная ошибка, исправить такую ошибку можно. Постоянная ошибка определяется как ошибка, которую нельзя устранить путем записи бита противоположного значения в тот же самый запоминающий элемент, поэтому для ее исправления можно использовать метод двойного инвертирования. Если шифратор 21. определяет наличие двойной ошибки, то на выходе 25 появляется признак двойной ошибки, данные с инверсных выходов регистров 1 и 2 через мультиплексоры 12,13 и 14,15 поступают на входы коммутаторов 6,7 и через них - на вьосоды 22,, 23, Одновременно инверсные значения контрольных битов с инверсных выходов регистра 3 через мультиплексор 11 и коммутатор 8 поступают на выходы 24. Инверсные значения данных и контрольных битов записьтаются в контроли уемую память, затем читаются из нее. Производится формирование новых контрольных битов и признаков ошибки, их дешифрация. Если удалось исправить хотя бы одну ошибку, методом двойного инвертирования, то вторая ошибка будет устранена при помощи кода Хэмминга,

Запись отдельног о байта, ос тцест- вляется следующим образом.

При записи в память одного из байтов слова данных к нему должен быть приформирован второй байт, уже хранящийся в контролируемой памяти, контрольные биты вырабатываются на основе полного слова. Поэтому вначале из памяти читается слово, записанное по тому же адресу, по которому должен быть записан байт. Устройство функционирует так же, как в режиме Чтение из памяти. После того, как слово данных проверено и в.случае необходимости скорректировано, оно записьтается в регистры 4 и 5. Тепер по входам 22 (23) через коммутатор 6(7) и мультиплексор 9(10) в регистр 1(2) заносится записываемый байт, одновременно в регистр 2(1) через мультиплексор 10(9) записьшается другой байт из регистра 4(5), после чего формируются контрольные биты. Оба байта и контрольные биты записываются в память.

По входам 26 подаются управляющие воздействия для управления работой дешифратора 20, шифратор 21, коммутаторов 6-8, мультиплексоров 9-15 и стробы записи информации в регистры 1 -5.

Формула изобретения

Устройство для обнаружения и исправления ошибок в блоках памяти, содержащее коммутаторы, регистры, сумматор по модулю два, блок сравнения, шифратор, дешифратор и элементы НЕРАВНОЗНАЧНОСТЬ, причем одни из входов и выходов первого и второго коммутаторов являются информационным входами и выходами устройства, одни из входов и выходов третьего коммутатора являются контрольными входами и выходами устройства, прямые выходы первого регистра подключены к одним из входов сумматора по модулю два, другие входы которого соединены с прямыми выходами второго регистра, а выходы - с одними из входов блока сравнения, другие входы которого подключены к прямым выходам третьего регистра, входы которого соединены с другими выходами третьего коммутато-

5 Ю t5 20

25

0

5

0

5

ра, выходы блока сравнения соединены с входами дешифратора и шифратора, выход которого является выходом признака устройства, управляющие входы коммутаторов, входы синхронизации регистров с первого по третий, дешифратора и шифратора являются вхо- дом синхронизации устройства, выходы дешифратора подключены к одним из входов элементов НЕРАВНОЗНАЧНОСТЬ, отличающееся тем, что, с целью повьш1ения надежности устройства, в него введены четвертый и пятый регистры и с первого по седьмой мультиплексоры, причем одни из входов первого и второго мультиплексоров подключены соответственно к выходам пятого и четвертого регистров, другие входы - соответственно к другим выходам первого и второго коммутаторов, а выходы - соответственно к входам первого и второго регистров, входы третьего мультиплексора соединены соответственно с инверсными выходами третьего регистра и с выходами сумматора по модулю два, а выхода - с другими входами третьего коммутатора, входы четвертого мультиплексора подключены к прямым и инвзрсным выходам первого регистра, а выходы - к. одним из входов седьмого мультиплексора и другим входам элементов НЕРАВНОЗНАЧНОСТЬ, выходы которых соединены со входами пятого регистра и другими входами седьмогб мультиплексора, выходы которого подключены к другим входам первого коммутатора, входы пятого мультиплексора соединены с прямыми и инверсными выходами второго регистра, а выходы - с одними из входов шестого мультиплексора и другими входами элементов НЕРАВНОЗНАЧНОСТЬ, выходы которых подключены ко входам четвертого регистра и другим входам шестого мультиплексора, выходы которого соединены с другими входами второго комьгутатора, управляющие входы мультиплексоров и входы синхронизации четвертого и пятого регистров являются входом синхрони- зации устройства.

Редактор М. Товтин

Составитель Т. Зайцева,

Техред А.Кравчу1С Корректор М. Максимишинец

Заказ 6687/48Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для формирования тестов | 1988 |

|

SU1573457A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

Изобретение относится к вычислительной технике и может быть применено для разработки блоков памяти микроэвм с коррекцией ошибок. Целью изобретения является повьшение надежности устройства. Устройство содержит регистры с первого по третий, коммутаторы, элементы НЕРАВНОЗНАЧНОСТЬ, сз мматор по модулю два, блок сравнения, дешфратор, шифратор, а также вновь введенные мультиплексо ры с первого по седьмой, четвертый и пятый коммутаторы. Надежность хранения информации повышается за счет того, что устройство позволяет за- письтать в память микроЭВМ как информационные слова, так и отдельные байты, с контролем по коду Хемминга, и при этом исправлять как одиночные, так и двойные ошибки, если хотя бы одна из них обусловлена постоянным сбоем элемента памяти. 1 ил. i (Л to N к

| Автоматика н- вычислительная техника | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| Электронная промьшшенность, 1983, № 4, с | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1986-12-15—Публикация

1985-04-12—Подача