СП

со со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU890441A1 |

| Запоминающее устройство | 1990 |

|

SU1753491A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для контроля памяти | 1984 |

|

SU1249589A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОДИНОЧНЫХ ОШИБОК, содержащее блок формирован-ия контрольных сигналов, одни из входов которого являются информаufiOHHbiMH входами устройства, и элементы НЕ, о т л ичающееся тем, что, с целью повышения быстродействия устройства, в него введены элемент И-НЕ и коммутаторы, адресные входы которых подключены к одним из выходов блока формирования контрольных сигналов, первые информационные входы коммутаторов соединены с информационными входами устройства, вторые информационные входы - с выходами элементов НЕ, входы которых подключены к информационным входам устройства, а выходы коммутаторов являются информа.ционными выходами устройства, контрольным входом которого является выход элемента И-НЕ, входы которого подключены к другим выходам блока формирования контрольных сигналов.

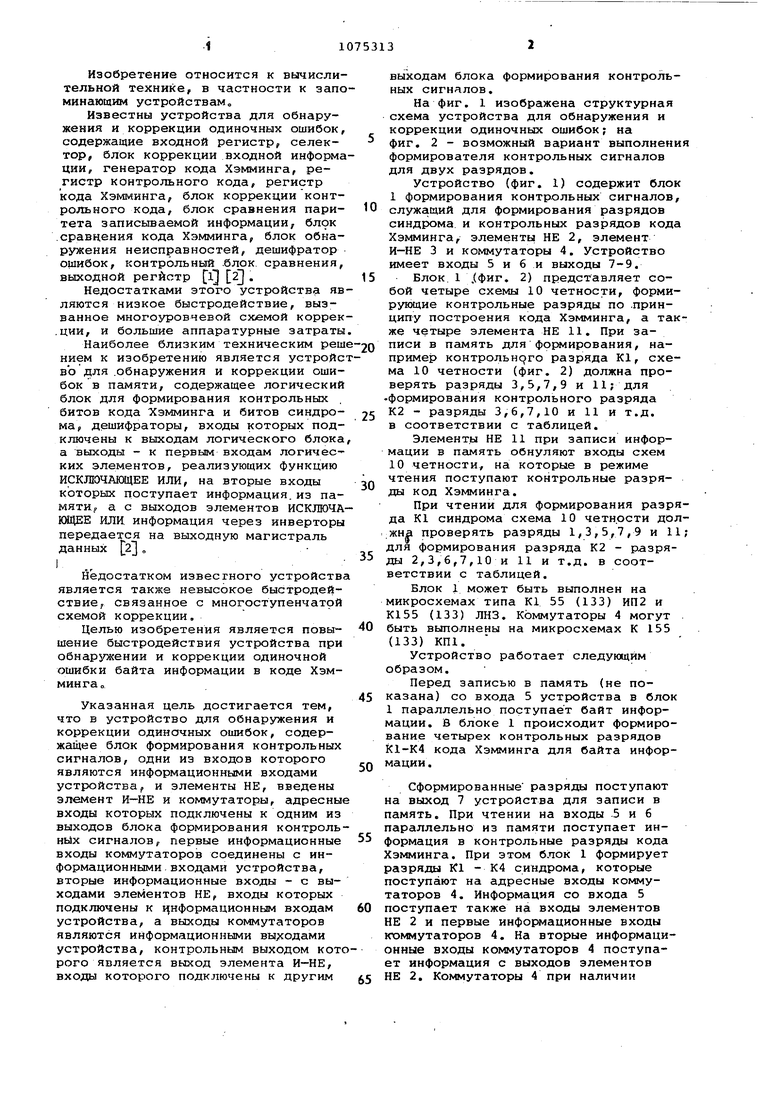

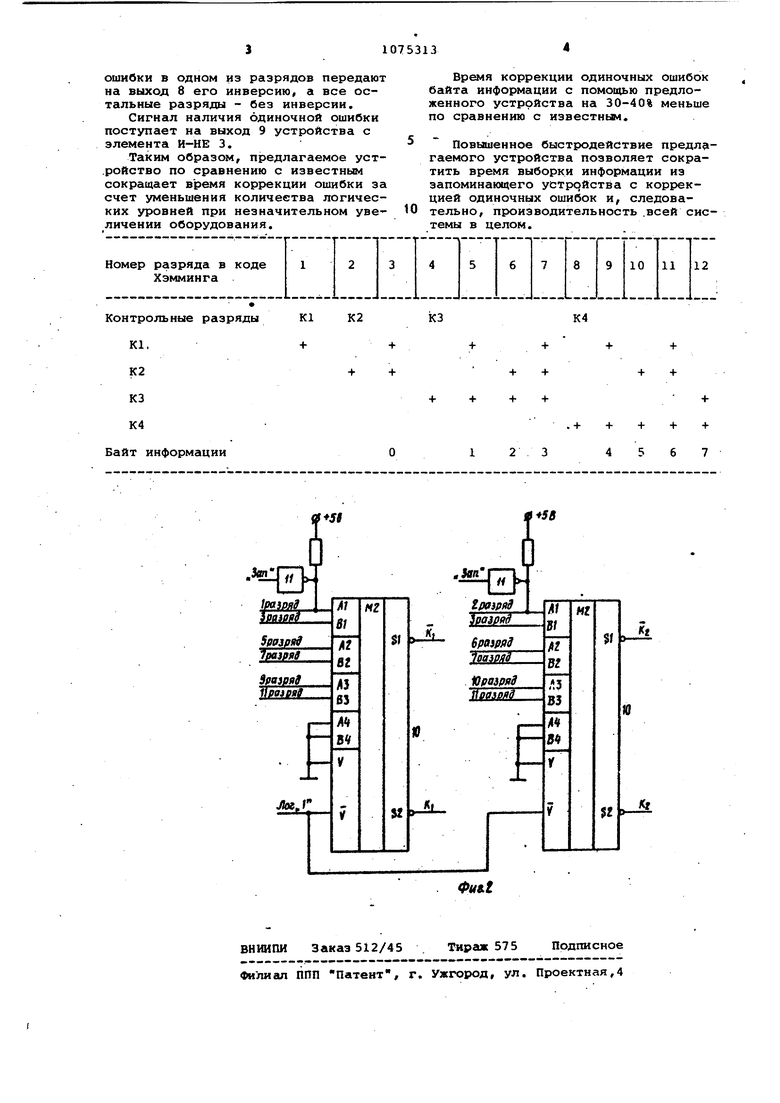

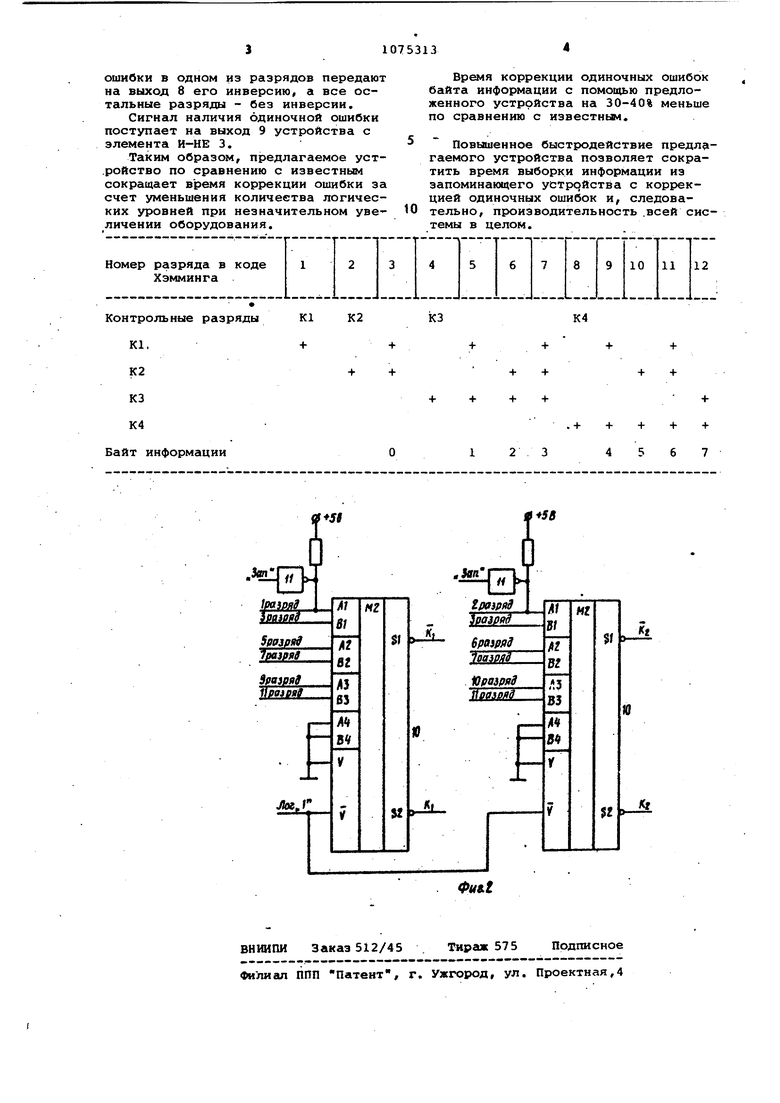

Фи8.1 Изобретение относится к вычислительной технике, в частности к запо минающим устройствам. Известны устройства для обнаружения и коррекции одиночных ошибок, содержащие входной регистр, селектор, блок коррекции входной информа ции, генератор кода Хэмминга, регистр контрольного кода, регистр кода Хэмминга, блок коррекции контрольного кода, блок сравнения паритета записываемой информации, блок .сравнения кода Хэмминга, блок обнаружения неисправностей, дешифратор ошибок, контрольный .блок, сравнения, выходной регистр ij 2 . Недостатками этого устройства яв ляются низкое быстродействие, вызванное многоуровневой схемой коррек .ции, и большие аппаратурные затраты Наиболее близким техническим реш нием к изобретению является устройс во для .обнаружения и коррекции ошибок в памяти, содержащее логический блок для формирования контрольных битов кода Хэмминга и битов синдрома, дешифраторы, входы которых подключены к выходам логического блока а выходы - к первым входам логических элементов, реализующих функцию ИСКЛЮЧАЮЩЕЕ ИЛИ, на вторые входы которых поступает информация.из памяти, а с выходов элементов ИСКЛЮЧА ЩЕЕ ИЛИ информация через инверторы передается на выходную магистраль данных 2 о I .,. Недостатком известного устройств является также невысокое быстродействие, связанное с многоступенчатой схемой коррекции. Целью изобретения является повышение быстродействия устройства при обнаружении и коррекции одиночной ошибки байта информации в коде Хэмминга „ Указанная цель достигается тем, что в устройство для обнаружения и коррекции одиночных ошибок, содержащее блок формирования контрольных сигналов, одни из входов которого являются информационными входами устройстваJ, и элементы НЕ, введены элемент И-НЕ и коммутаторы, адресны входы которых подключены к одним из выходов блока формирювания контроль ных сигналов, первые информационные входы коммутаторов соединены с информационными входами устройства, вторые информационные входы - с выходами элементов НЕ, входы которых подключены к информационным входам устройства, а выходы коммутаторов являются информационными вы;ходами устройства, контрольным выходом кото рого является выход элемента И-НЕ, входы которого подключены к другим выходам блока формирования контрольных сигналов. На фиг. 1 изображена структурная схема устройства для обнаружения и коррекции одиночных ошибок; на фиг, 2 - возможный вариант выполнения формирователя контрольных сигналов для двух разрядов. Устройство (фиг. 1) содержит блок 1 формирования контрольных сигналов, служащий для формирования разрядов синдрома и контрольных разрядов кода Хэмминга, элементы НЕ 2, элемент И-НЕ 3 и коммутаторы 4. Устройство имеет входы 5 и 6 и вьлходы 7-9. Блок. 1 ,(фиг. 2) представляет собой четыре схемы 10 четности, формирующие контрольные разряды по .принципу построения кода Хэмминга, а также четыре элемента НЕ 11. При записи в память для формирования, например контрольного разряда К1, схема 10 четности (фиг. 2) должна проверять разряды 3,5,7,9 и 11; для -формирования контрольного разряда К2 - разряды 3,6,7,10 и 11 и т.д. в соответствии с таблицей. Элементы НЕ 11 при записи информации в память обнуляют входы схем 10 четности, на которые в режиме чтения поступают контрольные разряды код Хэмминга. При чтении для формирования разряда К1 синдрома схема 10 четности должна проверять разряды 1,3,5,7,9 и 11; для формирования разряда К2 - разряды 2,3,6,7,10и 11 и т.д. в соответствии с таблицей. Блок 1 может быть выполнен на микросхемах типа К1 55 (133) ИП2 и К155 (133) ЛНЗ. Коммутаторы 4 могут быть выполнены на микросхемах К 155 (133) КП1. Устройство работает следующим образом. Перед записью в память (не показана) со входа 5 устройства в блок 1 параллельно поступает байт информации. В блоке 1 происходит формирование четырех контрольных разрядов К1-К4 кода Хэмминга для байта информации. Сформированные разрядам поступают на выход 7 устройства для записи в память. При чтении на входы .5 и 6 параллельно из памяти поступает информация в контрольные разряды кода Хэмминга. При этом блок 1 формирует разряды К1 - К4 синдрома, которые поступают на адресные входы коммутаторов 4. Информация со входа 5 поступает также на входы элементов НЕ 2 и первые информационные входы коммутаторов 4. На вторые информационные входы коммутаторов 4 поступает информация с выходов элементов НЕ 2. Коммутаторы 4 при наличии ошибки в одном из разрядов передают на выход 8 его инверсию, а все остальные разряды - без инверсии. Сигнал наличия одиночной ошибки поступает на выход 9 устройства с элемента И-НЕ 3. Таким образом, предлагаемое уст.ройство по сравнению с известным сокращает время коррекции ошибки за счет уменьшения количества логических уровней при незначительном увеличении оборудования.

К1

Контрольные разряды

К4

КЗ

5В Время коррекции одиночных ошибок байта информации с помощью предложенного устройства на 30-40% меньше по сравнению с известным. Повышенное быстродействие предлагаемого устройства позволяет сократить время выборки информации из запоминающего устррйства с коррекцией одиночных ошибок и, следовательно, производительность .всей системы в целом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля оперативной памяти | 1977 |

|

SU720515A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| с | |||

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

Авторы

Даты

1984-02-23—Публикация

1982-12-30—Подача