(54) УСТРОЙСТВО ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ

ИНФОРМАЦИИ ИЗ БЛОКОВ ОПЕРАТИВНОЙ ПАМЯТИ С КОРРЕКЦИЕЙ ОШИБКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1977 |

|

SU720515A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU752502A1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU940242A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для обнаружения и коррекции одиночных ошибок | 1982 |

|

SU1075313A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

1

Изобретение относится к запоминающим устройствам.

Известно устройство для записи и воспроизведения информации из блоков оперативной памяти с коррекцией ошибки построенное на специально разработанных морфйческих элементах, выходы которых имеют три логических состояния, причем область применения этих специальных элементов ограничена. В случае обнаружения одиночной ошибки выполняется ее коррекция Cl 1

Недостатком этого устройства является невысокая скорость работы.

Наиболее близким к предлагаемому является устройство содержащее селек- . тор входной информации, вход которого подключен к первому информационному входу устройства, а выход - к первому входу генератора синдромов, выход которого соединен со входом регистра паритета, выход которого подключен к nepBivмувходу блока коррекции паритета, дешифратор ошибки, первой вход которого

соединен со входом маркеров записи устройства, а выход - с первым входом блока коррекции входной информации, вторым входом блока коррекции паритета, регистр адреса, первый информационный

5 и контрольный входы которого подключены к адресному входу устройства, второй информационный вход регистра адреса подключен ко входу маркеров записи устройства, а информационный выход - к первому входу cxeivibi сравнения контрольного кода Хэмминга, выход которой. соединен с первым входом блока коррекции конт- рольцого кода Хэмминга, второй вход блока коррекции входной информации подключен ко второму информационному входу устройства, а выход - к третьемуинформационному входу регистра адреса, второй контрольный вход которого соеjg динен с выходом блока коррекции паритета, генератор паритета и схему сравнения паритета 2.

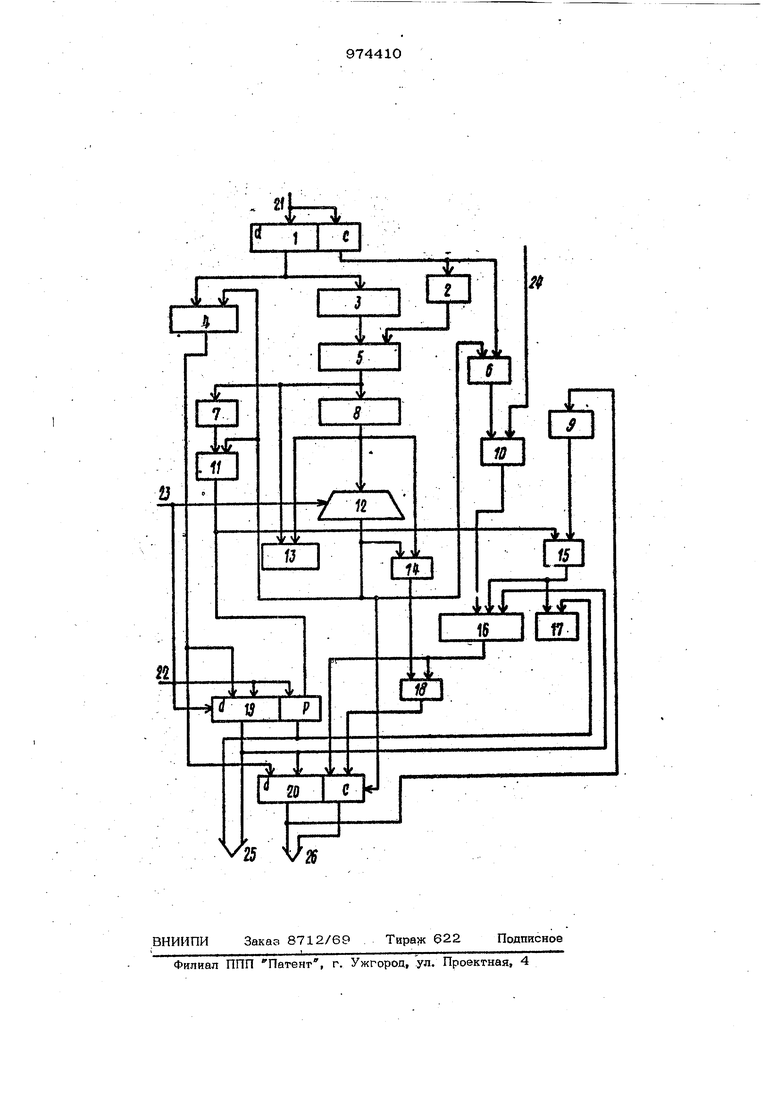

Недостатком этого устройстгмл является OTcyrcTBife BO3N oxHOCTH опновр моиной трансляции информации иэ двух модулей памяти, имеющих автономное управление. Это устройство позвехпнет лишь последовательно отрабатывать операции сначала с одним модулем памяти, а потом с другим и проводить лишь частичный контроль при операции селективной байтовой записи. Цель изобретения - повышение быстродействия и надежности работы устройства. Поставленная цель достигается тем, что в устройство введены элементы И, регистр синдромов, схема сравнения синд ромов, блок коррекции псевдоэталонного кода, селектор паритета, буферный регист селектор псевдоэталонного кода, вход которого соединен с первым контрольным входом устройства, а выход - со вторым входом генератора синдромов, выход кото рого подключен к первому входу схемы сравнения синдромов и ко входу регистра синдромов, выход КОТОРОГО подключен ко второму входу схемы сравнения синцромов, ко второму входу дешифратора ошиб ки и к первому входу первого элемента И, второй вход которого подключен к выЗГОДУ дешифратора ошибки, а выход - ко второму входу блока коррекции контрольного кода Хэммингй, выход которого подключен к первому контрольному входу буферного регистра, первый вход блока коррекции псевдоэталонного кода соединен с выходом дешифратора ошибки, второй - с контрольным входом устройства, а выход с первым входом второго элемента И, второй вход которого подключен ко входу Чтение устройства, а выход - ко второму входу схемы сравнения контрольного кода Хэмминга, третий вход которой подключен к выходу селектора паритета, первый вход которого подключен к выходу блока коррекции паритета,второй вход-к .выходу генератора паритета, вход KOTopo |го соединен с информационным выходом буферного регистра, первый вход .схемы сравнения паритета подключен к выходу селектора паритета, второй вход ее подключен к контрольному выходу регистра адреса, информационный выход которого «хюдинен с первым информационным входом буферного регистра, второй информаци онный вход которого соединен с выходом блока, коррекции входной информации, вто рой контрольный вход буферного регистра подключен к выходу схемы сравнения контрольного кода Хэмминга, а третий вход - к выходу дешифратора ошибки. , На чертеже представлена блок-схема устройства для записи и воспроизведения информации из блоков оперативной памяти с коррекцией ошибки. Устройство содержит регистр входной информации 1, селектор псевдоэталонного кода Хэмминга 2, селектор входной информаци 3, блок коррекции входной информации 4, генератор синдромов 5, блок коррекции псевдоэталонного кода (Хэмминга) 6, регистр паритета 7, регистр синдромов 8, генератор паритета 9, второй элемент И 10, блок коррекции паритета 11, дешифратор ошибки 12, схему сравнений синдромов 13, элемент И 14, селектор паритета 15, схему сравнения контрольного кода Хэмминга 1G, схему сравнения паритетов 17, блок коррекции контрольного кода Хэмминга 18, регистр адреса (скорректированной информации) 19, буферный регистр (записываемой информации) 20. Устройство имеет вход прочитанной из оперативной памяти информации 21, вход записываемой информации в память 22, вход маркеров записи 23 устройства, вход команды Чтение 24 устройства, выход скорректированной информации 25 устройства, выход записываемой информации 26 устройства. В соответствии с хранимой информацией регистр входной информации разделяется на блоки d (информационный) и С (контрольный хранит код Хэмминга), регистр скорректированной информации разделяется на блоки а и Р (контрольный, хранит код паритета), регистр записываемой информации разделяется на блоки d и С. Генератор кода Хэмминга состоит из элементов, реализующих функцию сложения по модулю 2. Для 64 информационных битов генератор вырабатывает 8 сумм по модулю 2. Генератор синдромов предсТгав- ляет собой К (К - число символов кода Хэмминга) двухвходовых элементов, реализуюших функцию сложения по модулю 2 символов кода Хэмминга, прочитанных из памяти с соответствующими символами кода Хэмминга, выработанными генератором кода Хэмминга. На чертеже генератор кода Хэмминга и генератор синдромов показаны одним функциональным блоком, названным генератором синдромов 5. Блок коррекции входной информации представляет собой т двухвходовь1Х элементов, реализующих функцию сложения по модулю 2 (где m - число информационных битов сообщения). Каждый элемент складывает информационный бит с соот59ветствук)Щ11М сигналом, выработанным де шифратором ошибки, указывающим на ошибку в этом бите. Устройство работает следуюшим образом. В оперативной памяти хранится информация совместно с контрольным кодом Хэмминга. Во время операции Чтение из памяти информация с сопровождающим ее кодом Хэмминга поступает через вход 21 и записывается в регистр входной ин формации 1 соответственно в блоки «3 и С регистра. Записанная в регистр 1 ин,формация поступает через селектор 3 на .вход генератора синдромов 5, туда же через селектор 2 поступает прочитанный ,иа памяти код Хэмминга. В генераторе синдромов вырабатывается код Хэмминга прочитанной из памяти информации и результат сравнейия этого кода с кодом Хэмминга, прочитанного из памяти. Результат сравнения, называемый син дром, записывается в регистр синдромов 8. Ненулевое значение синдрома характеризует наличие ошибки в сообщении. Кроме того, генератор синдромов вырабатывает паритеты байтов прочитанной из памяти информации, которая запоминается на регистре паритетов 7. Синдромные би ты декодируются дешифратором ошибок 12, Сигнал ошибки определяет действительный ошибочный бит и инвертирует ег посредством блока коррекции входной информации 4, связанного с каждым битом. Обнаружение дешифратором 12 четного числа активизированных синдромных битов указывает на некорректируемую ошиб ку. При исправлении однобитной ошибки исправляется также и паритет байта посредством блока коррекции паритета 11. Скорректированные паритеты и информаци записываются соответственно в блоки Р и с1 регистра скорректированной информа ции 19. Параллельно с вышеописанной процедурой исправления одиночной ошибки выполняются следующие контрольные действия. После записи синдромов в регистр 8 селектор 3 подключает на вход генератора 5 информационный блок d регистра 1 с кольцевым сдвигом на г /2 байтов (где г - общее число информационных байтов, прочитанных из оперативной памяти). Аналогично селектор 2 подключает на вход генератора 5 блок С регистра 1 с кольцевым сдвигом на К/2 битов (где К - число разрядов кода Хэмминга, прочитанных из оперативной памяти). 0« Кодирование матрицы кода Хэмминга | осуществляется таким образом, что при подаче на вход генератора 5 одной и той же информации и разрядов кода Хэмминга прямо и с кольцевым сдвигом, синдрюмы получаются различным путем. Оборудование генератора, задействованное для генерации битов SO, 51, 52, 53, S4, S5, SG, 57 при прямой подаче информации и кода Хэмминга на вход генератора, генерирует cooiветственно биты 54, 55, 56, S7, SO, 51 S2, 53. при подаче той же информации и кода Хэмминга с кольцевым сдвигом. Результаты обеих генераций должны совпадать, если соответствующее оборудование функционирует правильно. Сравнение результата генераций осуществляется в блоке сравнения синдромов 13. Скорректированная информация, записанная в регистр 19, поступает на первый вход контрольной схемы сравнения 16. На третий вход через селектор 15 поступает скорректированный побайтный паритет сообщения. На второй вход через второй элемент И Ю из регистра 1 под управлением команды Чтениепоступает псевдоэталонный код Хэмминга, который в случае ошибки в С - бите подвергается коррекция в блоке коррекции 6. Псевдоэталонный код Хэмминга, прочитанный из памяти, мы называем потому, что в нем возможны ошибки. Несравнение псевдоэталонного кода Хам минга, поступающего из блока коррекции 6 и кода Хэмминга, образованного в контрольной схеме сравнения 16, указывает на логическую ошибку в аппаратуре Таким образом, во время операции чтения контрольный блок сравнения выполняет функцию генератора синдромов. В схеме сравнения паритетов 17 проверяется правильность записи скорректированных паритетов в блок Р регистра ,19 и правильность поступления их на |ВХо.д контрольного блока сравнения через «селектор 15. При операции полной записи информация и сопровождающие ее паритеты поступают на вход 22 и записываются соответственно в блоки с1 и Р регистра 19. С выхода регистра 19 содержимое блока 61 перезаписывается в блок cJ регистра 20. Записанная в блок «3 регистра 2О информация поступает на генератор паригетов 9. Выработанные генератором 9 паритеты через селектор 15 подаются на третий вход контрольной схемы сравнения 16. На первый вход блока поступа7 97 ют необходимые для образования кода Хэмминга информационные биты с регистра 19, на второй вход информация не поступает, так как на время операции записи второй элемент И 10 блокируется. Таким об.разом, во время операции полной запи/зй контрольная схема сравнения выступает в роли генератора кода Хэмминга. Образованный в контрольной схейе сравнения 16 код Хэмминга, минуя блок коррекции 18 записывается в блок С регистра 20. Образованные генератором 9 паритеты сравниваются в схеме сравнения 17 с содержимым блока Р регистра 19. В устройстве операцииЧтение и Запись.могут выполняться одновремено для различных модулей оперативной памяти, имеющих автономное управление, т, е. с одним модулем памяти, инициируется операция Чтение и информация с сопровождающим ее кодом Хэмминга записьтается в регистр входной информации одновременно с другим модулем оперативной памяти инициируется Jэпepaция Запись 1и записываемая информация в сопровожде- НИИ битов паритета записывается в регист .скорректированной информации 19. Далее обе операции выполняются устройством параллельно согласно вышеизложенному порядку. Операция селективной байтовой записи в оператнвйую память начинается с функции чтения информации из памяти по входу 21 и записи поступающей из процессора информации по входу 22. Считанная из оперативной памяти информация записывается под управлением маркеров записи совместно с информацией поступающей по входу 22 в блок «3 регист ра 19. В блок Р регистра также под управлением маркеров записи записываются паритеты, поступающие по входу 22, и паритеты, образованные генератором 5 из прочитанной информации. Как считанная из оперативной памяти информация, так и образрванные из нее паритет поступают на регистр 19, не подвергаясь коррекции, так как в ©тот момент, ошибка еще не обнаружена. Содержимое блока d регистра 19 перезаписывается в блок 61 регистра 20 Генератор паритетов 9 вырабатывает паритеты записанной в регистр 20 информа-. ции. В схеме сравнения 17 производится сравнение паритетоЬ, записанных в блок Р регистра 19, и паритетов, образованных генераторов9 из информации, подлежащей записи. Образованные паритеты через селектор 15 поступают на третий вход конт рольной схемы сравнения 16. На первый 10 вход поступают необходимые для образования кода Хэмминга информационные биты, записанные в регистр 19. Прочитанный из памяти код Хэмминга не пропускается через второй элемент И 1О. Таким образом, контрольная схема сравнения выполняет функцию генератора кода Хэмминга. Одновременно с этим, в случае обнаружения ошибки в информации, прочитанной из памяти, дешифратор 12 вырабатывает сигналы ошибки информационного бита и паритета. Производится операция коррекции информации и, если ошибка происходит в байте, который должен быть перезаписан в оперативную память, блок коррекции 18 производит инвертирование соответствующих С битов путем подачи на блок коррекции 18 синдромов с регистра 8 через К элементов И 14, на вторые входы которых подается команда с дешифратора ошибок гГ:ОШР - М УОШР -М V...VOUJP™ .м . где ОШР, - ошибка паритета; М - маркер записи. Скорректированные С-биты записывают ся в блок С регистра 20, а исправленный в блоке коррекции 4 байт заменяет ранее записанный байт с ошибкой в регистре .20 под управлением сигнала ошибки в байте, поступающего с дешифратора ошибок 12. Если ошибки не обнаружено или произошла ошибка в байте, который не будет перезаписан в память, коррекция С-битов не происходит. Затем производится подключение на второй вход контрольной схемы сравнения через второй элемент И 10 содержимого блока С регистра записываемой информации 20, и контрольный блок соавнения проверяет правильность присвоенно о кода Хэмминга для скомпанованной и скорректированной информации. Активизированный выход блока сравнения свидетельствует о логической ошибке, Предлагаемое устройство позволяет одновременно транслировать обращение по чтению и записи к различным по модулям памяти и автономным управлением, таким образом, вдвое увеличивая быстродействие по сравнению с прототипом. При этом обеспечивается полный сквозной контроль оборудования адаптера Окак при чтении, так и при записи, чем повышается ноложькхть рабцты как самого устройс7вп, так и к-ятрольной аппаратуры. 997 Формула изобретения Устройство для записи и воспроизведения информации из блоков оперативной памяти с коррекцией ошибки, содержащее селектор входной информации, вход которого подключён к первому информационному входу устройства, а выход - к первому входу генератора синдромов, выход которого соединен со входом регистра паритета, выход которого подключен к первому входу блока коррекции паритета, дешифратор ошибки, первый вход которого соединен со входом маркеров записи устройства а Ьыход - с первым входом блока коррекции входной информации; вторым входом блока коррекции паритета, регистр адреса, первый информационный и контррльнь1й входы которого подключены к адресному входу устройства, второй информационный вход регистра адреса подключен ко входу маркеров записи устройства, а информационный выход - к первому входу, схемы сравнения контрольного кода Хамминга, Выход которой соединен с первым входом блока,коррекции контрольного.кода Хэммин га, второй вход блока коррекции входной информации подключен ко второму информационному входу устройства, а выход -к третьему информационному входу регистра адреса, второй контрольный вход которого соединен с выходом блока коррекции паритета, генератор паритета и схему сравнения паритета, отличающееся тем, что, с целью повьпиения быстродействия и надежности устройства, оно содержит элементы И, регистр синдромов, схем сравнения синдромов,- блок коррекции псев- доэталонного кода, селектор па{зитета, буферныйрегистр, селектор псевдоэталонного кода, вход которого соединен с первым контрольным входом устройства, а выход - со вторым входом генератора синдромов, .выход которого подключен к первому вхо10ду схемы сравнения синдромов и ко входу регистра синдромов, выход которого подключен ко второму входу схемы сравнения синдромов, ко второму входу дешифратор ошибки и к первому входу первого элемента И, второй вход которого подключен к выходу дешифратора ошибки, а выход - ко второму входу блока коррекции контрольного кода Хэмминга, выход которого подключен к первому контрольному входу буферного регистра, первый вход блока кор рекции псевдоэталонного кода соединен с выходом дешифратора ошибки, второй - с контрольным входом устройства, а выход - с первым входом второго элемента И, второй вход которого подключен ко входу . Чтение устройства, а выход - ко второму входу схемы сравнения контрольного (КОда Хэмминга, третий вход которой под- рслючен к выходу селектора паритета, пер1вый вход которого подключен к выходу блока коррекции паритета, второй вход JC выходу генератора паритета, вход- которого соединен с информационным выходом буферного регистра, первый вход схемы рравнения паритета подключен к выходу селектора паритета, второй вход ее подключен к контрольному выходу регистра адреса, информационный выход которого .соединен с первым информационным входом буферного регистра, второй иш{)0рмационный: вход которого соединен с выходом блока .коррекции входной информации, второй контрольный вход буферного регистра подключен к выходу схемы сравнения коит- рольного кода Хэмминга, а третий вход - к выходу дешифратора ошибки. Источники информации, принятые во внимание при экспертизу 1.3ЕЕЕ Trcinsaction on соториters. Voe С-25, № 6, 1976. йТ7Й5торское свидетельство СССР ПО заявке N 252037.4/18-24, кл. G 11 С 7/ОО, 15.О9.77 (прототип).

t

. itf

r iT

Авторы

Даты

1982-11-15—Публикация

1977-11-25—Подача